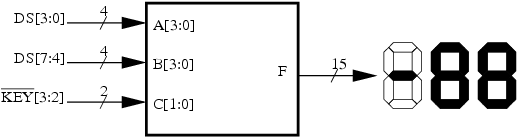

- Read the example found at the end of this lab about how to use MUXes to design a 7-segment decoder for decimal numbers. It will help a lot!

- Review two's complement arithmetic and adders in the textbook.

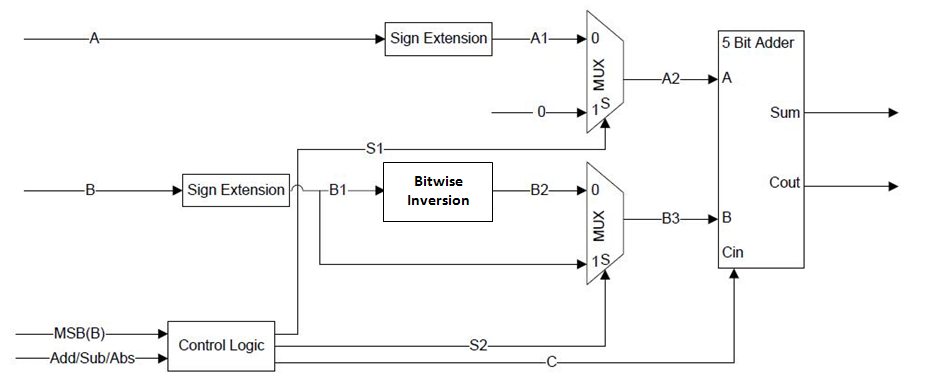

Figure 1: Top-level view of the CALCULATOR circuit.

| Key3 (C1) | Key2 (C0) | Operation |

|---|---|---|

| Pressed | Pressed | Display A+B |

| Pressed | Unpressed | Display A-B |

| Unpressed | Pressed | Display the absolute value of B |

| Unpressed | Unpressed | Display the absolute value of A |

Restrictions

- The top level module may be in schematic or Verilog.

- Sub modules may be in schematic or Verilog.

- You may use any Verilog constructs you learned thru lab 3.

- You can use the conditional ? operator. Look in the Verilog combinational reference or slides for details. It is a very powerful way to implement an N-bit, 2 to 1 multiplexer.

- You CANNOT use

the "+"

or "-" Verilog operator. This

will greatly simply the design.

- You may only use one n-bit ripple carry adder!!

This will be strictly enforced. You can use the schematic editor

version implemented in lab 2 or write it one in Verilog. Of course, you

cannot

use the + or -

Verilog

operator.

- Your design should use combinational blocks that implement such functions as: ones complement, sign extension, MUXs and data path control.

- The inputs A and B must be

expressed as buses, ie A[3..0] and

B[3..0]. See the accompanying guide on using buses for schematic entry.

- This problem is best approached by analyzing the common features among the various data operations (addition, subtraction, and absolute value) and designing an efficient multi-function datapath unit that can perform each of those operations in response to the applied opcodes. The core of the datapath must be an adder with appropriately-controlled multiplexers on its inputs in order to do addition, subtraction and absulute value. You will also need to design a "decoder" to display the two's complement result on the 7-segment LEDs.

- Big hint: You will want your adder to be 5-bits wide and you will want to sign-extend the 4-bit inputs to your 5-bit adder.

- The following module is a equivalent to a 4 bit, 2 to 1 multiplexer.