## EECS 270 Midterm Exam

## Spring 2013

| Name:                                           | unique name:                           |

|-------------------------------------------------|----------------------------------------|

| Sign the honor code:                            |                                        |

| I have neither given nor received aid on this e | xam nor observed anyone else doing so. |

|                                                 |                                        |

Scores:

| Problem # | Points |

|-----------|--------|

| 1         | /12    |

| 2         | /12    |

| 3         | /10    |

| 4         | /8     |

| 5         | /8     |

|           | /16    |

| 7         | /13    |

| 8         | /9     |

| 9         | /11    |

| Total     | /100   |

## **NOTES:**

- 1. Open book and Open notes

- 2. There are 12 pages total. Count them to be sure you have them all.

- 3. No electronic devices of any kind are allowed on this exam.

- 4. This exam is fairly long: don't spend too much time on any one problem.

- 5. You have about 120 minutes for the exam.

- 6. Some questions may be more difficult than others. You may want to skip around.

- 7. Be sure to show work and explain what you've done when asked to do so. Even if work isn't requested it is a good idea to provide your work as it will help with partial credit.

| Fil. | in each blank or circle the best answer.[12 points, -2 per wrong or blank answer, min 0]                               |

|------|------------------------------------------------------------------------------------------------------------------------|

| a)   | The 6-bit 2's complement number representation of -7 is                                                                |

| b)   | 11001, when treated as a 5-bit signed-magnitude number, has a decimal representation of — 9                            |

| c)   | The range of representation for a 6-bit 2's complement number is from $\frac{2^{5}}{2^{5}}$ to $\frac{2^{5}}{2^{5}}$ . |

| d)   | square memory (equal number of rows and columns in the memory device) the row                                          |

|      | decoder would have inputs while the column MUX would have                                                              |

|      |                                                                                                                        |

| e)   | A <u>sum-of-products</u> representation of $!(A^*!B)$ is $\overline{A} + B$                                            |

| f)   | If you were to represent A+B+C+!D using canonical sum-of-products, there would be                                      |

|      | minterms.                                                                                                              |

| g)   | If you were to represent $A \oplus B \oplus C$ in canonical product-of-sums form, there would                          |

|      | be maxterms.                                                                                                           |

| h)   | A 4-bit 8 to 1 MUX would require select lines.                                                                         |

|      |                                                                                                                        |

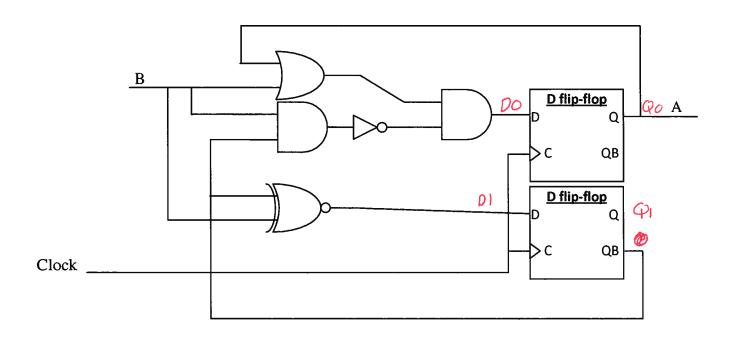

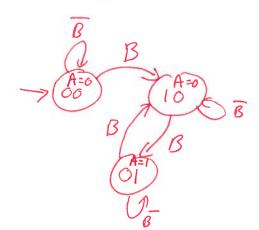

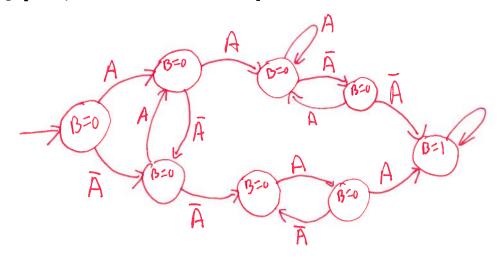

2) Draw the state transition diagram which is implemented by the above circuit. You should assume the initial state is when both flip-flops are "0". You should only include states that can be reached from the initial state. Clearly show your work. [12 points]

from the initial state. Clearly show your work. [12 points]

$$\mathcal{D}_{o} = (Q_{o} + \mathcal{B}) \cdot \overline{\mathcal{B}} \cdot \overline{Q_{1}} = (Q_{o} + \mathcal{B}) \cdot \overline{\mathcal{B}} + Q_{1}$$

$$D_1 = (B \oplus \overline{Q_1}) = B \oplus Q_1$$

| _ O. Q. B | D, Do |

|-----------|-------|

| 0 0 0     | 00    |

| 001       | 10    |

| 010       | 01    |

| 0 1 1     | 10    |

| 1 00      | 1 0   |

| (0)       | 0 1   |

| 110       | 1 1   |

| 117       | 0 1   |

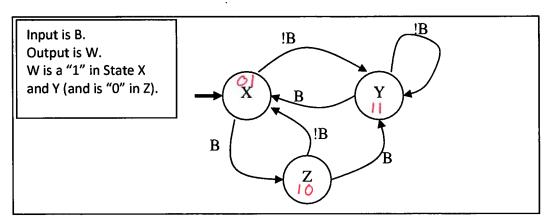

3) Design a state machine which implements the following state transition diagram. Assign state bits S[1:0] as 01 for state X, 11 for state Y, and 10 for state Z. You are to assume that you will never reach the state S[1:0]=00, so you don't care what happens in that case. You must show your work to get any credit! You only need to compute the next state and output logic, you don't need to draw the gates or flip-flops! Place your answer where shown, all answers must be in sum-of-products form.

[10 points]

(Be sure all are in sum-of-products form!)

$$NS1 = \frac{\overline{S} + \overline{S} +$$

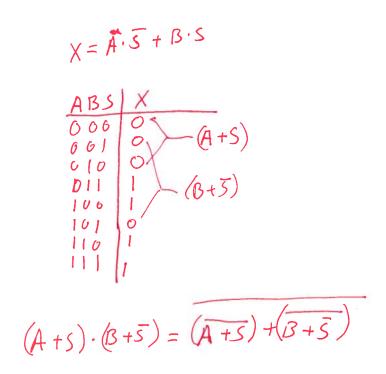

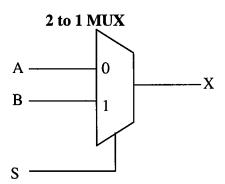

4) Implement a 1-bit 2 to 1 MUX using only 2-input NOR gates. For full credit, use 4 or fewer NOR gates. Use the inputs and outputs A, B, S and X as shown below. As always, you can freely use Vcc and ground. [8 points, half credit for using more than 4 gates]

5) Design a state transition diagram that has one input (A) and one output (B). The output should go high and stay high only when A has been high for two cycles in a row <u>and</u> low for two cycles in a row in any order. So inputs of 0011 and 1100 would both cause B to go (and stay) high, as would 00101011 (for example). You are to use as few states as possible.

[8 points, 3 are for a minimal answer]

|        | Min | Max |  |

|--------|-----|-----|--|

| OR/AND | 2ns | 4ns |  |

| NOT    | 1ns | 1ns |  |

| XNOR   | 2ns | 7ns |  |

| DFF: |             | Min    | Max |

|------|-------------|--------|-----|

|      | Clock to Q  | 2ns    | 3ns |

|      | Set-up time | 4 ns   |     |

|      | Hold time   | ??? ns |     |

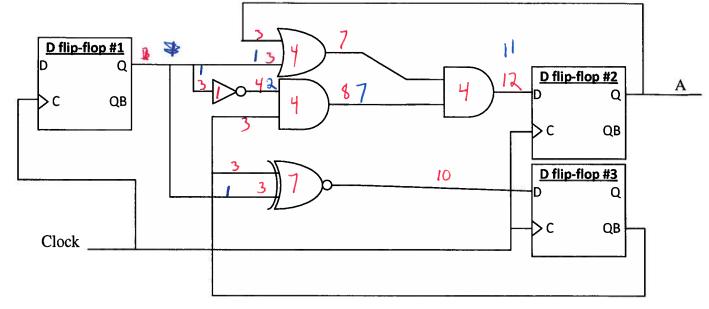

- 6) Answer the following questions [16 points]

- a) In order for this circuit to work correctly, what range of values that would be acceptable for the hold time requirement of the D flip-flops? Assume the only options range from 1ns to 10ns. Clearly show your work. [5]

Smallest Ins Largest 4ns

Fastest Path is DAI to XNOR Clock to Q+

min xNor delay: Znst2ns anything sonsiler also works 1

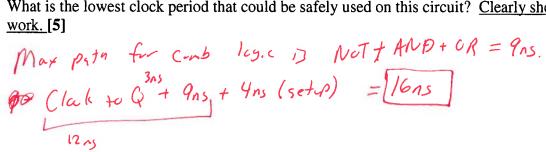

b) What is the lowest clock period that could be safely used on this circuit? Clearly show your

c) Say that flip-flop #1's clock edge <u>always</u> happens 2ns <u>before</u> the clock-edge that goes to flip-flops #2 and #3. Would that change your answer to part a, part b, both or neither? Indicate which answers would change and what they would change to. [6]

a) For part a the fisheren input to Dft3 can chance days after Dft3's rising edge. Answer becomes listo 2ns

For part b DH #1 will have it's & chanse no later

than Ins after PH2+3 have their risits edge.

New math done in blue.

Gets 15ns

## 7) Verilog [13 points]

a) Complete the following module which is to implement a 2-bit modulo counter. The counter should count in order (0, 1, 2, 3, 0, 1, etc.) if reset is low and enable is high on each rising edge. If reset is high, the output should go to 0 on the next rising edge. If reset is low and enable is low, the output should be held. [6]

```

module counter_2(clock, reset, enable, count);

input clock, reset, enable;

output [1:0] count;

reg [1:0] s, ns;

//next state

always @*

if ~reset & enable)

ns = s + 1;

else

ns = s;

//state register

always @(posedge clock)

S <= ns;

assign count = s;

endmodule</pre>

```

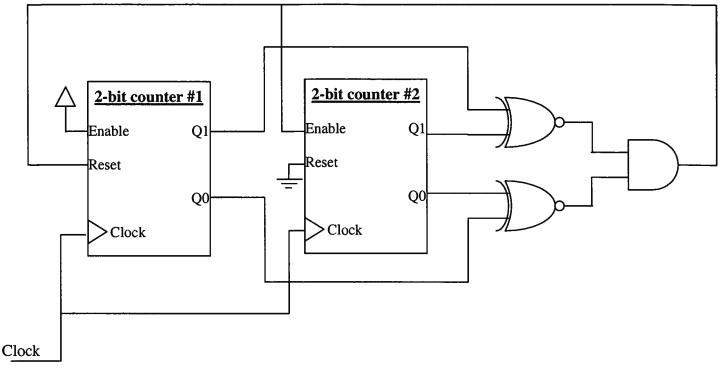

b) Using the counter you designed on the previous page, complete a Verilog module which implements the following circuit. The output should be the Q[1:0] of counter #2. [7]

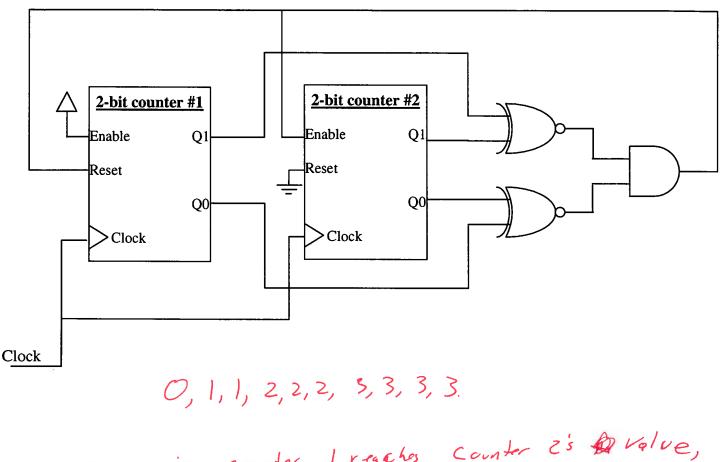

8) Consider the circuit diagram below where both counters are modulo counters and the resets are synchronous. Assuming both counters are initially zero, indicate the pattern that will appear out of counter #2. Write your answer using decimal numbers. So, for example, a possible (but wrong) answer would be "0, 1, 2, 1, 1, 3" which indicates that the output would be the pattern 012113012113012113 (etc.) repeating forever. Explain your answer. [9 points]

Every time counter I reaches counter 2's @ value, counter 1 is reset and counter 2 increments.

Pattern from counter #2:

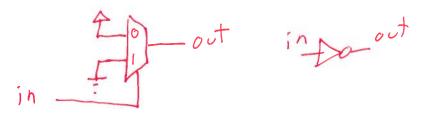

9) Using MUXes [11 points]

a) Design a NOT gate using only a 1-bit 2 to 1 MUX. [2]

b) Design a 2-input XOR gate using only a 1-bit 2 to 1 MUX. [3]

c) Design a D flip-flop using only 1-bit 2 to 1 MUXes. For full credit, you should use as few MUXes as possible. No credit will be given to any answer that uses more than 4 MUXes. [6 points, 3 for being minimal]