# EECS 270 Midterm Exam Closed book portion unique name: Key

Name:

Key

Sign the honor code:

I have neither given nor received aid on this exam nor observed anyone else doing so.

- 1. This part of the exam is closed everything. No calculators, books, notes, etc.

- 2. Once you finish this part, turn it in and you'll be given the open book part. You won't be able to come back to this part.

- 3. There are 4 pages total

- 4. You have about 120 minutes for the exam total. We'd suggest you not spend more than 15 minutes or so on this part.

- 5. In this document we use \* for AND, + for OR, ! for NOT, and  $\oplus$  for XOR.

# 00111-711000-711001-168421

- 1. Fill in each blank or circle the best answer. [7 points, -1.5 per wrong or blank question, min 0]

- a) The 5-bit 2's complement number representation of -7 is 100

- b) The range of representation for a 6-bit two's complement number is from  $\frac{-32}{10}$  to  $\frac{31}{10}$ .

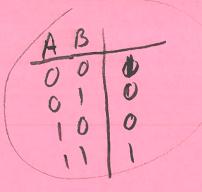

- c) The canonical <u>product-of-sums</u> representation of (AB+!A!B) is (A+B)

- d) The frequency of a 20ns clock is 0,05 GHz.

- e) With a D-flip-flop, there is a short period after the rising edge of the clock where the D input must remain constant or the flip-flop may not behave correctly. That short time is called the hold time

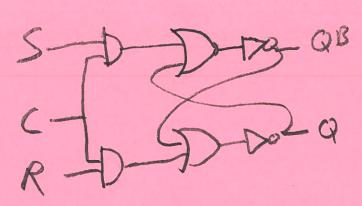

- 2. Draw the gates needed to implement an <u>SR latch with enable</u> using only AND, OR and NOT gates (no bubbles, NOR gates, or NAND gates). [3 points]

3. Using only a decoder and an OR gate, draw a circuit which implements the following: !(A+B)+A\*C Be sure things are clearly labeled. [5 points]

3 to 8 do cule 01 06 05 IZ. 04 JI 03 IN 02 01 UP

A.B +A.C ABC 000 0,1,5,7 1 60 6 h C

#### This page intentionally left blank

If you write anything here you want graded be sure to mention it on the page with the relevant problem

1-21 (1 1-21 (1 1-21 (1

4/14

٠

## EECS 270 Midterm Exam Open book portion

Spring 2023

ner Name:

unique name: <u>Key</u>

Sign the honor code:

I have neither given nor received aid on this exam nor observed anyone else doing so.

### **NOTES:**

- 1. This part of the exam is open books and open notes. You may not use any device capable of communication (cell phones, calculators with wireless, etc.)

- 2. You have about 120 minutes for the exam total.

- 3. Some questions may be harder than others. Manage your time wisely.

- 4. Unnecessarily complex designs will likely not get full credit.

- 5. Be sure to show your work when asked.

1. Using the <u>rules of logic</u>, convert !(A+!C)+(A\*C) into a *minimal* sum-of-products form. Provide the name of the rule used for each step. [5 points]

(A+1)+A.C A.C+AC Given Demorganis Combining.

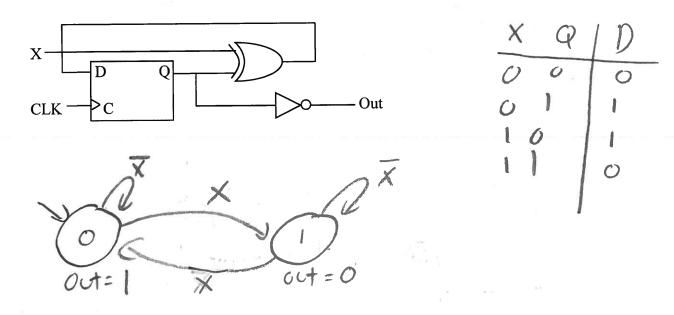

2. Draw a state transition diagram for the following state machine. The initial state is when the flip-flop has the value 0. [5 points]

3. Say you have the following values associated with the process you are using (notice the hold and setup times are not specified). Assume you intend to clock this circuit at 50MHz. 730MS

| Dff:        | Min | Max |        | Min | Max |

|-------------|-----|-----|--------|-----|-----|

| Clock to Q  | 2ns | 4ns | OR/AND | 2ns | 5ns |

| Set-up time | ??  | 'ns | NOT    | 1ns | 2ns |

| Hold time   | ??  | 'ns | XOR    | 2ns | 7ns |

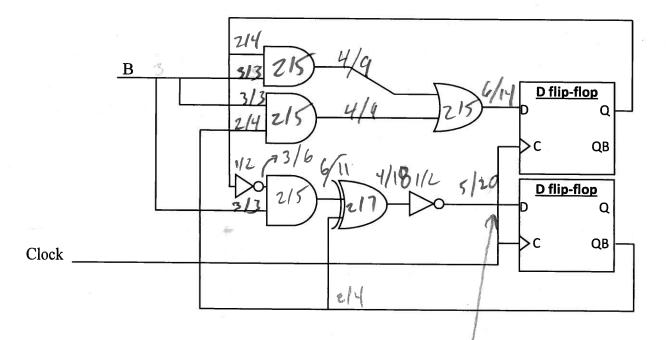

Assuming the input B always arrives 3ns after the rising edge of the clock, answer the following questions. [10 points]

a) Assuming you want a reliable circuit, what is the highest value the flip-flop could have for a hold time? <u>Clearly</u> show your work. [5]

b) Assuming you want a reliable circuit, what is the highest value the flip-flop could have for a setup time? <u>Clearly</u> show your work. [5]

7/14

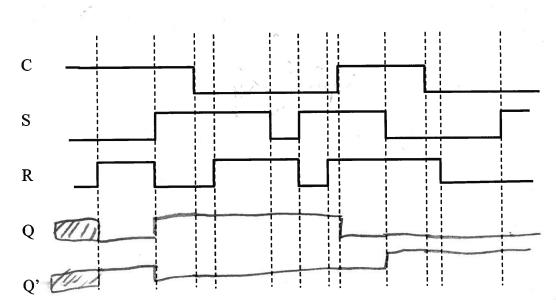

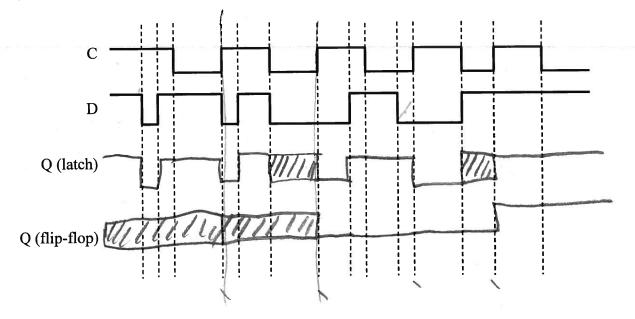

4. Complete the following timing diagrams. If the value is unknown (or oscillating) at some point, clearly indicate that with hashes (as shown). [12 points]

b) Complete the timing diagram below for both a D latch and a D flip-flop. [6]

a) Complete the timing diagram below for an SR latch with enable. [6]

Value unknown

Page 8 of 14

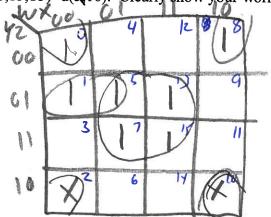

5. Find the minimum sum-of-products for the following function: F=∑wxyz(0,1,5,7,8,13,15)+d(\$,10). Clearly show your work via a Kmap. [8 points]

WXZ+WYZ+XZ

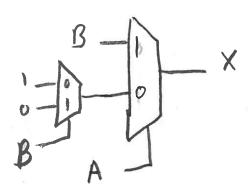

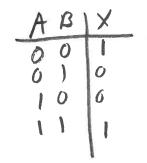

6. Using only two 2-to-1 MUXes, implement an XNOR gate with inputs A, B and an output X. You may freely use 0 and 1 as inputs as needed. [5 points]

if A=1, adout B if A=0 eclout B

- 7. Design a state transition diagram for each of the following. [12 points]

- a) The machine has one input A and one output, B. The output is to go high if the most recent values of A has been either "101" or "11", otherwise the output is to be low. [6]

A:1011001010111 ← This is the output after the machine sees the A value immediately B:0011000010111 above it. Α 10 10 5

B=0 it not shown

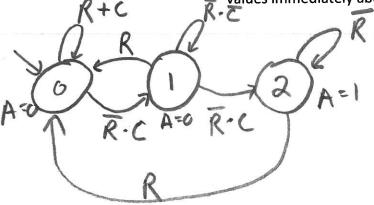

b) The machine has two inputs C and R and one output A. A should go high only if C has been high for at least two cycles since R last was high. Be sure to look at the example carefully. [6]

R:100000010000111000000 C:0110010001001110111111 A:0011111100001000011111

← This is the output after the machine sees the C and R values immediately above it.

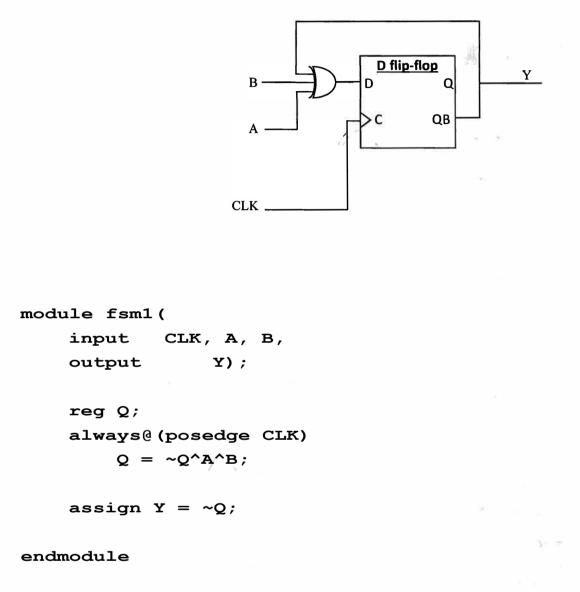

8. Write a Verilog module, Bob, which implements the following circuit. The code must be correct, clear, and reasonably concise to get full points. [9 points]

There are a number of ways to have done this, but the above is probably the easiest.

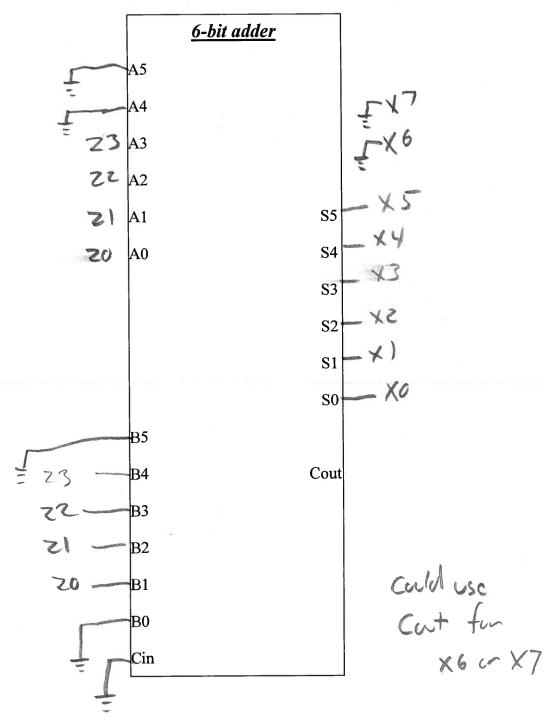

- 9. Design a circuit which has as an input Z[3:0] and output X[7:0] where both are treated as unsigned numbers. X should be equal to 3 times Z's value. You may only use:

- One 6-bit adder (with carry in and carry out), drawn below.

- Up to three NOT gates (you may use bubbles to represent these)

- Power and ground.

As always, you may not need all of those devices. [9 points]

Page 12 of 14

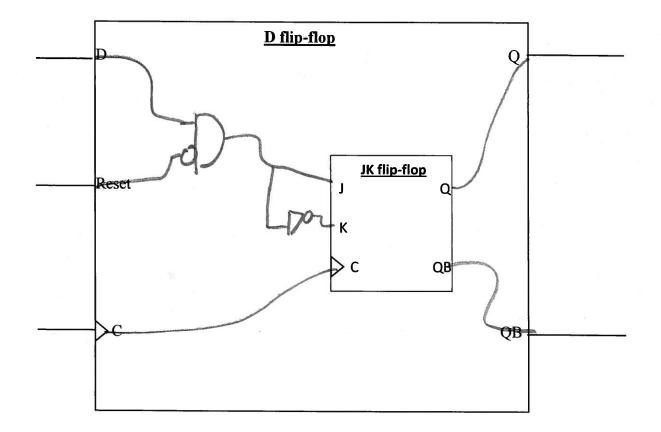

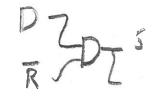

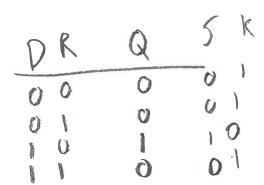

10. Build a D flip-flop with reset using only a JK flip-flop and standard gates. [10 points]

**Recall:**

| Truth Table |   |     |                            |  |  |  |

|-------------|---|-----|----------------------------|--|--|--|

| J           | К | CLK | Q                          |  |  |  |

| 0           | 0 | 1   | Q <sub>0</sub> (no change) |  |  |  |

| 1           | 0 | 1   | 1                          |  |  |  |

| 0           | 1 | 1   | 0                          |  |  |  |

| 1           | 1 | t   | $\overline{Q}_0$ (toggles) |  |  |  |

Page 13 of 14

This page intentionally left blank If you write anything here you want graded be sure to mention it on the page with the relevant problem