## **Quiz 2 - Spring 2023 - EECS 270**

| Name:      | uname:                                                                                                                                                                                    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| will have  | is graded out of 100 points and is worth about 4% of your class grade. You 20 minutes for this quiz. Closed everything including calculators! <u>To receive edit, work must be shown.</u> |

| 1. Fill-in | -the-blank [20 points, -5 for each wrong or blank answer]                                                                                                                                 |

| a.         | The time before the rising edge of the clock when no input should be changing                                                                                                             |

|            | after is called the                                                                                                                                                                       |

| b.         | is -7 as a 5-bit 2's complement number                                                                                                                                                    |

| c.         | A signal with a frequency of 10MHz has a period ofns                                                                                                                                      |

| d.         | !(A+!B+C), when expanded into canonical sum-of-products form, has                                                                                                                         |

|            | minterms.                                                                                                                                                                                 |

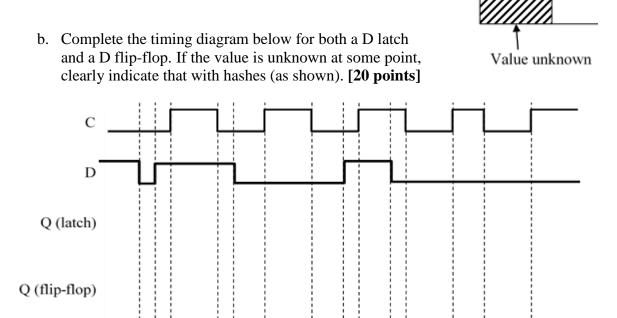

- 2. Answer the following questions:

- a. Draw gates which implement a D-latch. [15]

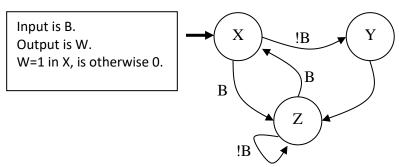

3. Design a state machine which implements the following state transition diagram. Assign state bits **S[1:0]** as **00** for state **X**, **10** for state **Y**, and **11** for state **Z**. You are to assume that you will never reach the state S[1:0]=10, so you don't care what happens in that case. You must show your work to get any credit! *You only need to compute the next state and output logic, you don't need to draw the gates or flip-flops! Place your answer where shown, all answers must be in <u>sum-of-products</u> form. [45 points]*

(Be sure all are in sum-of-products form (canonical or otherwise)!)

NS1= \_\_\_\_\_

NS0=\_\_\_\_

W= \_\_\_\_