## **Quiz 4 - Spring 2011 - EECS 270**

Name: \_\_\_\_\_\_uname: \_\_\_\_

This quiz is graded out of 100 points and is worth about 4% of your class grade. You will have 20 minutes for this quiz. Closed everything including calculators! To receive partial credit, work must be shown.

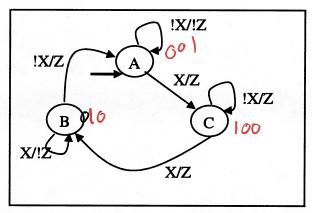

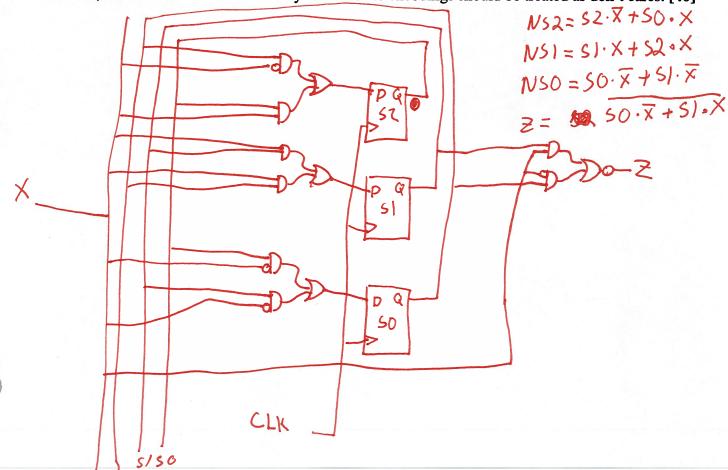

1. Consider the following state-transition diagram:

Using only AND, OR, and NOT gates (including freely using bubbles) as well as D flip-flops, <u>draw</u> the state machine for the above state-transition diagram. You are to use an encoding of A=001, B=010, and C=100 for the states. Any unused state encodings should be treated as don't cares. [40]

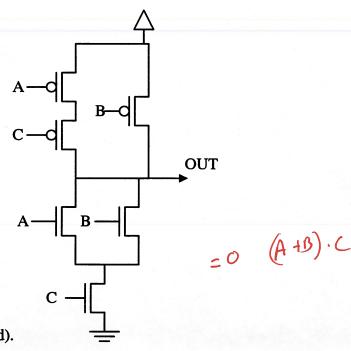

2. Transistor problem. [30]

| A | В | C | OUT |   |        |

|---|---|---|-----|---|--------|

| 0 | 0 | 0 | 1   |   | 1      |

| 0 | 0 | 1 | 1   |   | 1      |

| 0 | 1 | 0 | 1   |   | 1      |

| 0 | 1 | 1 |     | 0 | O      |

| 1 | 0 | 0 | 1   |   | - [    |

| 1 | 0 | 1 | 1   | 0 | 5 mule |

| 1 | 1 | 0 |     |   | よって    |

| 1 | 1 | 1 |     | 0 | 0      |

Fill in the above truth table with either "1", "0", "Hi-Z" or "Smoke" (the last if OUT is connected to both Vcc and Ground).

3. It is November 2011 and you've got a friend taking EECS 270 who are really confused about set-up and hold times.

a. Clearly explain what set-up time and hold time are on a D flip-flop. Include a simple sketch.

After + before the clock (respectively) when the Dinput is not allowed to change.

Clock

Clock

(""" = d must remain constant during this sets hold time

b. Explain how set-up time impacts a circuit design in 35 words or less. [10]

Betapetore Bccause the data must remain steady for a some

time before the clark edge, this ends up increasing

the regular clark periods

c. Explain how hold time impacts a circuit design in 35 words or less. [10]

We must insure that the fist path (min path) through

the circuit ist isn't fister than the half time. If

it is we must add delay.