## **Quiz 1 – Spring 2012 – EECS 270**

| Name: unar | ne: |

|------------|-----|

|------------|-----|

This quiz is graded out of 100 points. Please remember you can drop your lowest quiz score. You will have 20 minutes for the quiz. It is closed book and closed notes. Show your work and circle your answer! The last problem is quite hard and worth fewer points...

1. Convert the following to <u>canonical</u> sum-of-products using any method.

F=!(A+B)\*(C+B) [30 points]

$$\overline{A} \cdot \overline{B} \cdot \overline{C} + A \cdot \overline{B} \cdot (C + B)$$

$$\overline{A} \cdot \overline{B} \cdot (C + B)$$

2. What is the range of representation for the following schemes? Also, for each scheme indicate how you would represent using that scheme (or write "no representation" if it can't be represented.)

[25 points, -3 per wrong or blank answer, min 0]

- a. 4-bit 2's complement

b. 5-bit signed magnitude

7

to -8

to -15

- -8 is 11000

c. 6-bit unsigned

8 is () 0 ( 0 00)

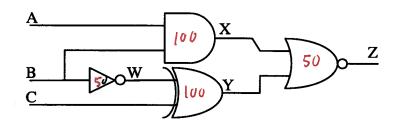

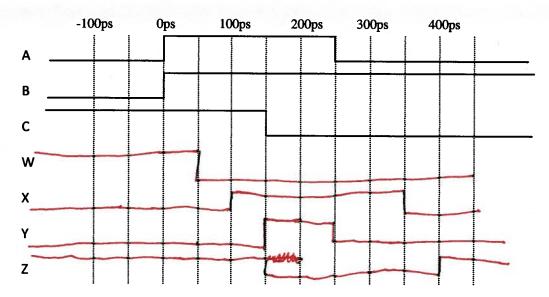

- 3. Consider the following digital circuit with the inputs shown below. Draw the values of W, X, Y and Z on the timing diagram using the following timing information.

[30 points]

- NOT and NOR gates have a delay of 50ps

- AND and XOR gates have a delay of 100ps

WOC

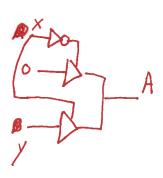

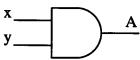

4. Design an AND gate using only tri-state buffers and inverters. You may freely use 0 and 1 as inputs. Your labels on inputs and output should be the same as the gate below. [15 points]