## **Quiz 2 - Spring 2014 - EECS 270**

| Name:                                 | uname:                                                                                                                                                                                                                                    |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| will have a                           | is graded out of 100 points and is worth about 4% of your class grade. You 20 minutes for this quiz. Closed everything including calculators! The last ould be more work than the points assigned.  e partial credit, work must be shown. |

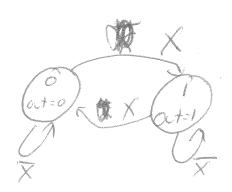

|                                       | bu have one input, X as well as a single output Y. Provide a state-transition m where Y goes high iff the last three values of X were "110". [30 points]                                                                                  |

| N N N N N N N N N N N N N N N N N N N | X X X X X X X X X X X X X X X X X X X                                                                                                                                                                                                     |

| 2. Fill-in a.                         | -the-blank [20 points, -4 for each wrong or blank answer]  The 5-bit 2's complement number representation of -6 is                                                                                                                        |

| b.                                    | The range of representation for a 6-bit <u>two's complement</u> number is from to                                                                                                                                                         |

|                                       | $(X+Y)*(X+Z) = X + \frac{1}{2}$ according to the distributive theorem.                                                                                                                                                                    |

| d.                                    | The time before the rising edge of the clock when no input should be changing                                                                                                                                                             |

is called the <u>set q</u>

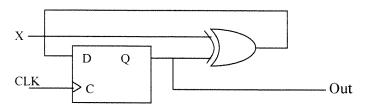

3. Draw a state transition diagram for the following circuit. [35 points]

-5 x, x

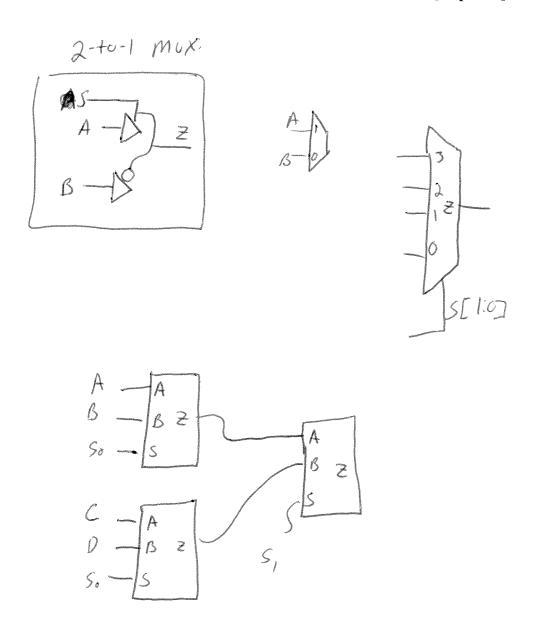

4. Design a 1-bit 4-to-1 MUX using only inverters and tri-state devices. You will be graded in part for having an efficient design. As always, feel free to build a device out of these components and then use that device as needed. [15 points]