## University of Michigan EECS 311: Electronic Circuits Fall 2008

Final Exam

12/12/2008

| NAME: | Solutions |  |

|-------|-----------|--|

| NAME: |           |  |

## **Honor Code:**

I have neither given nor received unauthorized aid on this examination, nor have I concealed any violations of the Honor Code.

| Signature |  |

|-----------|--|

|           |  |

| Problem | Points | Score | Initials |

|---------|--------|-------|----------|

| 1       | 25     |       |          |

| 2       | 30     |       |          |

| 3       | 15     |       |          |

| 4       | 30     |       |          |

|         | Total  |       |          |

## **Problem 1 (25 Points):** Potpourri – all parts in the problem are unrelated.

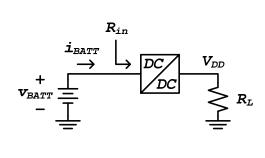

a) A DC to DC converter regulates a variable DC voltage source, such as a battery, to a stable voltage source (e.g.  $V_{DD}$ ). The symbol for a DC/DC converter is shown below, along with a typical response of  $i_{BATT}$  vs.  $v_{BATT}$ . From the graph, approximate a numerical value for the small-signal input resistance  $R_{in}$  in Ohms at a DC operating voltage of  $V_{BATT}=2V$ .

$$R_{1n} = \frac{\partial c_{BAT}}{\partial c_{BAT}} = \frac{\Delta c_{BAT}}{\Delta c_{BAT}}$$

$$= \frac{1}{\sqrt{2}} = \frac{1}{$$

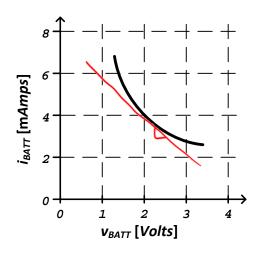

b) Determine the region of operation of  $Q_1$ , and find the DC bias current  $I_C$  for the following circuit. Assume  $\beta_F=25$ ,  $V_{BE(on)}=0.5V$ , and  $V_{CE(sat)}=0.25V$ . Ignore base width modulation.

Superposition:

$$I_{c} = (5-0.25) \frac{1}{5k+5k/2.885k} - (2.5-0.5) \frac{5k/(2.885k)}{5k(5k+5k//2.885k)}$$

$$= |588MA|$$

c) You built the following circuit on your breadboard, and measured  $B_F=100$ ,  $g_m=10m\Omega^{-1}$ ,  $R_C=10k\Omega$ , and  $R_S=10k\Omega$ . You measured the small-signal frequency response of  $v_x/v_{in}$  which has a DC gain of 0.5, and a 3dB upper cutoff frequency of 160kHz. You think this cutoff frequency is completely due to Miller multiplication of  $C_\mu$ . Assuming no other capacitances in the circuit, approximate the value of  $C_\mu$ . You may neglect base width modulation.

$$V_{IN} \stackrel{5v}{=} R_{c}$$

$$V_{IN} \stackrel{1}{=} R_{c$$

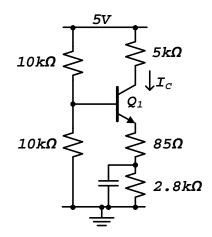

d) Find an expression for the midband gain  $A_v = v_{out}/v_{in}$  of the following amplifier in terms of the small signal parameters. The input voltage is applied to the body terminal of the FET. Include body effect in your small signal model. Ignore channel length modulation.

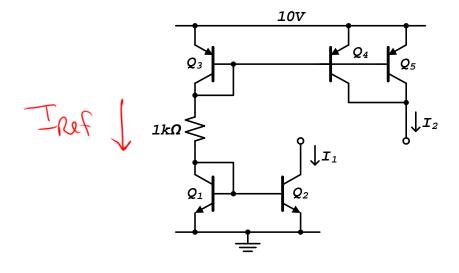

e) Find values for the two output currents  $I_1$  and  $I_2$  for the circuit below. Assume  $Q_1=Q_2$ ,  $Q_3=Q_4=Q_5$ , and  $\beta_F=\infty$ . Assume the NPN  $V_{BE(on)}=0.7V$ , and the PNP  $V_{BE(on)}=-0.7V$ , and all devices are in the forward active region. Ignore base width modulation.

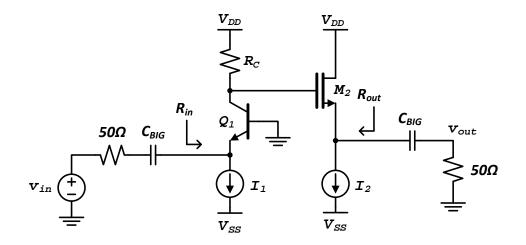

**Problem 2 (30 Points):** In the following two-stage amplifier, for  $Q_1$  assume  $\beta_F=250$  and  $V_{th}=25mV$ , ignore base width modulation, and assume it is in the forward active region. For  $M_2$ , assume  $\mu_n C_{ox} \frac{W}{L}=1mA/V^2$ , ignore channel length modulation and body effect, and assume it is in saturation. Assume capacitors  $C_{BIG}$  are DC coupling capacitors.

a) Identify the topology for each stage (C-E, C-C, C-B, C-S, C-D, C-G).

b) Draw the complete low-frequency small-signal model (DC coupling caps are short, high-frequency caps are open). Label each component (other than  $50\Omega$  source and load resistors) in terms of  $R_C$ ,  $I_1$ ,  $I_2$ ,  $\beta_F$ ,  $\mu_n C_{ox} \frac{W}{L}$ , and  $V_{th}$ . Make sure to express  $g_m$  and  $r_\pi$  in terms of these parameters.

$$T_{c} = \beta T_{1} \qquad T_{0} = T_{2}$$

$$Son \qquad V_{1} \neq \frac{\beta+1}{T_{1}} \qquad T_{1} \neq \frac{\beta+1}{T_{2}} \qquad T_{2} \neq \frac{\beta+1}{T_{2}} \qquad T_{3} \neq \frac{\beta+1}{T_{2}} \qquad T_{4} \neq \frac{\beta+1}{T_{2}} \qquad T_{5} \neq \frac{\beta+1}{T_{2}} \qquad T_{5} \neq \frac{\beta+1}{T_{2}} \qquad T_{6} \neq \frac{\beta+1}{T_{2}} \qquad T_{7} \neq \frac{\beta+$$

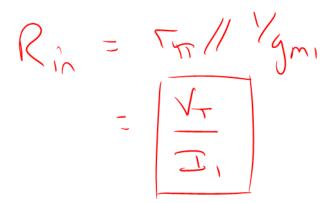

c) Find an expression for the input resistance  $R_{in}$  in terms of  $R_C$ ,  $I_1$ ,  $I_2$ ,  $\beta_F$ ,  $\mu_n C_{ox} \frac{W}{L}$ , and  $V_{th}$ . The definition of  $R_{in}$  is shown in the schematic.

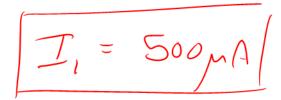

d) Solve for the value of  $I_1$  required for an input resistance of  $R_{in}=50\Omega$ .

e) Find an expression for the output resistance  $R_{out}$  in terms of  $R_C$ ,  $I_1$ ,  $I_2$ ,  $\beta_F$ ,  $\mu_n C_{ox} \frac{W}{L}$ , and  $V_{th}$ . The definition of  $R_{out}$  is shown in the schematic.

Rout =

$$\frac{1}{g_{m2}} = \frac{1}{\sqrt{2}M_n Co_x \frac{w}{L} T_2}$$

f) Find an expression for midband gain  $A_v=v_{out}/v_{in}$  in terms of  $R_C$ ,  $I_1$ ,  $I_2$ ,  $\beta_F$ ,  $\mu_n C_{ox} \frac{w}{L}$ , and  $V_{th}$ .

$$A_{V} = \frac{V_{T}}{V_{T} + SoI_{1}} \frac{I_{1}BR_{c}}{(B+1)V_{T}} \frac{1}{1+\frac{1}{50.\sqrt{2\mu_{n}Cox}}} \frac{1}{V_{T}V_{T}}$$

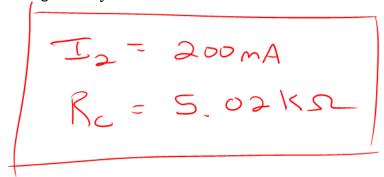

g) Solve for the values of  $I_2$  and  $R_C$  that result in an output resistance of  $R_{out}=50\Omega$  and a gain of  $A_v = 25$ .

h) Assuming  $R_{in}=50\Omega$ ,  $R_{out}=50\Omega$ , and  $C_{BIG}=10\mu F$ , use SCTC to find a value for the lower cutoff frequency  $f_L$ .

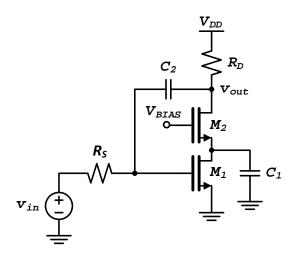

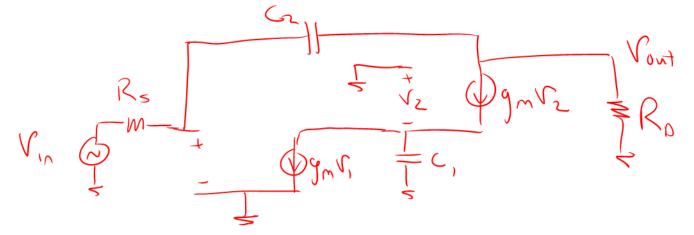

**Problem 3 (15 Points):** The amplifier shown below is referred to as a Cascode stage. It consists of a common-source stage, followed by a common-gate stage. For the following problem, neglect channel length modulation and body effect, assume both transistors are matched and are biased in the saturation region, assume  $C_1$  and  $C_2$  are high-frequency capacitors, and there are no other high-frequency capacitors in the circuit (neglect  $C_{gd}$ ,  $C_{gs}$ , etc.)

a) Draw the high-frequency small-signal model for the amplifier, including  $\mathcal{C}_1$  and  $\mathcal{C}_2$ .

| Initials: |  |

|-----------|--|

|           |  |

b) Find an expression for the midband small-signal gain  $A_v=v_{out}/v_{in}$ , assuming the high-frequency capacitors are open-circuits.

c) Use OCTC to find an expression for the upper cutoff frequency  $f_H$ . Apply the Miller multiplication technique across capacitor  $C_2$ . For this part, assume  $v_{out}/v_{in}=-A$ , and leave your answer in terms of A and the other elements in the small-signal circuit.

Initials: \_\_\_\_\_

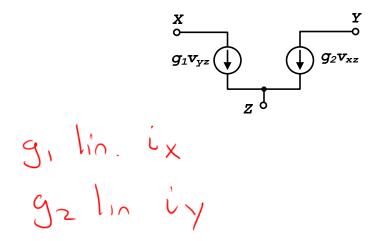

**Problem 4 (30 Points):** This problem you will linearize the three-terminal device shown below with terminals X, Y, and Z. Current  $i_X$  and  $i_Y$  are defined into the device, as shown in the symbol.

The large-signal response for current  $i_Y$  is given in the form of an expression as follows:

Large-Signal

$$i_Y$$

:  $i_Y = 0.01(v_{XZ})^3$

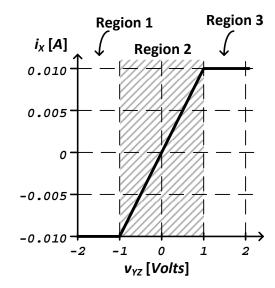

The large-signal response for current  $i_X$  is given in the form of a graph, shown below. There are three regions of operation as defined by the inequalities below, and the large-signal current response in each region can be found from the graph.

Definition of regions of operation:

Region 1:  $v_{YZ} < -1V$

Region 2:  $-1V \le x_{YZ} \le 1V$

Region 3:  $v_{YZ} > 1V$

a) The small-signal response of this device can be represented by the model below where  $g_1$  and  $g_2$  are small-signal transconductances with units  $\Omega^{-1}$ . Which transconductance ( $g_1$  or  $g_2$ ) represents the linearized  $i_X$  and which one represents linearized  $i_Y$ ?

b) Derive expressions for the transconductances  $g_1$  and  $g_2$  in terms of the DC operating point  $I_X$ ,  $I_Y$ ,  $V_{XZ}$ , and  $V_{YZ}$ . Note that the transconductance representing linearized  $i_X$  will have three separate expressions for transconductance; one for each region of operation.

$$g_{1} = \frac{\partial ix}{\partial v_{yz}} \Big|_{DC op} \quad \text{Region } 1: \quad g_{1} = 0$$

$$\text{Region } 2: \quad g_{1} = 10 \text{ mV}$$

$$\text{Region } 3: \quad g_{1} = 0$$

$$g_{2} = \frac{\partial iy}{\partial v_{xz}} \Big|_{DC op} \quad g_{2} = 0.03 (v_{xz})^{2}$$

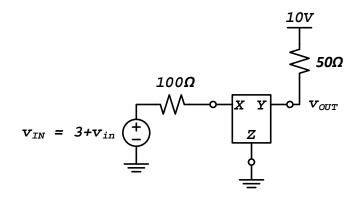

c) Solve for the values for the DC bias voltages  $V_{XZ}$  and  $V_{YZ}$  at the DC operating point of the circuit below. Note that the input voltage source has a DC bias voltage of 3V plus a small-signal input  $v_{in}$ .

$$V_{X2} = 3 - i_{X} 100$$

$V_{Y2} = 10 - 50 i_{Y}$

$$i_{\chi} = 0.01 V_{\chi 2}^{3}$$

$$i_{\chi} = 10 \text{mA} \left( \text{Reg } 3 \right)$$

$$\frac{\sqrt{\chi_2} = 2V}{i_{\gamma}} = 80mA$$

$$\sqrt{\chi_2} = 6V$$

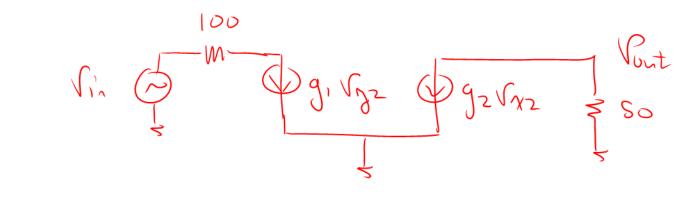

d) Draw the small-signal circuit for the circuit from part c). Derive an expression for the small-signal gain  $A_v = v_{out}/v_{in}$  and evaluate the gain at the DC operating point found in part c).

$$A_{1} = \frac{-5000}{[-5000]}$$

at

$$0 < 0$$