## University of Michigan EECS 311: Electronic Circuits Fall 2009

Quiz 1

10/21/2008

|       | $\leq 11$ |  |

|-------|-----------|--|

| NAME: | SOLUTIONS |  |

## **Honor Code:**

I have neither given nor received unauthorized aid on this examination, nor have I concealed any violations of the Honor Code.

| Signature |  |

|-----------|--|

|           |  |

| Problem | Points | Score | Initials |

|---------|--------|-------|----------|

| 1       | 25     |       |          |

| 2       | 30     |       |          |

| 3       | 15     |       |          |

| 4       | 30     |       |          |

|         | Total  |       |          |

## **Problem 1 (25 Points):** Potpourri – the following problem has three unrelated parts.

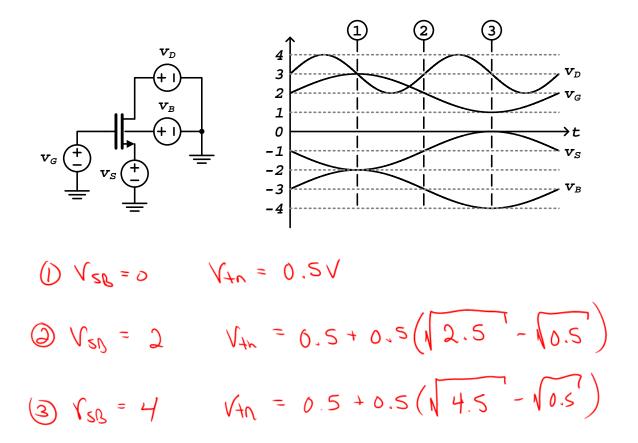

a) Use the circuit below for this part, where the voltages applied to the terminals of the NMOS vary with time as shown in the graph. Complete the table below by evaluating the specified voltages and determining the region of operation at the 3 points in time indicated on the graph. Assume for the NMOS that  $V_{t0}=0.5V$ ,  $2\phi_F=0.5V$ , and  $\gamma=0.5V^{1/2}$ .

| Point | $v_{GS}$ | $v_{DS}$ | $V_{tn}$ | Region of Operation |

|-------|----------|----------|----------|---------------------|

| 1     | 5        | 5        | 0.5      | Sat                 |

| 2     | 3        | 4        | 0.94     | Sat                 |

| 3     | 1        | 3        | 1.21     | Cutoff              |

Initials: \_\_\_\_\_

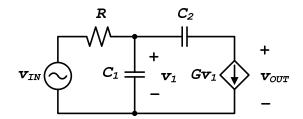

b) Find the transfer function  $H(s) = v_{OUT}/v_{IN}$  of the following circuit.

$$R\left(\frac{V_{1N}-V_{1}}{R}\right) = \left(V_{1} S C_{1} + G V_{1}\right) R$$

$$V_{1} = V_{1N} \frac{1}{1 + SRC_{1} + RG}$$

$$V_{007} = V_1 - GV_1 \frac{SC_2}{SC_2}$$

$$\frac{V_{ont}}{V_{in}} = \frac{1 - \frac{G}{SC_2}}{1 + SRC_i + GR}$$

c) Use the circuit below for this part. Assume the two diodes have identical parameters (same  $I_S$  and n), and are in the forward bias region. Using the appropriate large-signal model for the diodes, calculate the value for  $v_{OUT}$  at a temperature of  $100\,^{\circ}\text{C}$ .  $k=1.38\cdot 10^{-23}\,\text{J/K}$  and  $q=1.6\cdot 10^{-19}\,\text{C}$ .

Problem 2 (30 Points):

Use the following circuit for all parts of this problem.

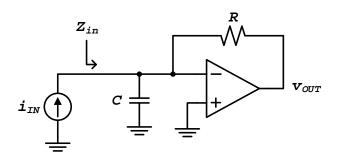

a) Assume the opamp has finite gain  $A_0$  and differential input resistance  $R_{id}$  between the (+) and (-) terminals. All other parameters of the opamp are ideal. Find an expression for the input impedance  $Z_{in}$ .

$$\dot{L}_{t} = \frac{V_{t}}{V_{sc}} + \frac{V_{t}}{R_{i}\lambda} + \frac{V_{t}-V_{ost}}{R}$$

$$Z_{IN} = \frac{1}{SC + \frac{A_0 + 1}{R}}$$

b) Assume the opamp has finite gain and bandwidth, given by the following expression. All other parameters of the opamp are ideal.

$$A(s) = \frac{A_0}{1 + s/\omega_p}$$

Find an expression for the transfer function  $H(s) = v_{OUT}/i_{IN}$ .

$$V_{out} = A(s) V_{il} \qquad V_{i} = -V_{il} \qquad (V_{i} \otimes inv. terminal)$$

$$\dot{L}_{in} = V_{i} SC + \frac{V_{i} - V_{out}}{R}$$

$$= -V_{out} \left(\frac{SC}{A(s)} + \frac{1}{A(s)} + 1\right)$$

$$\frac{V_{out}}{\dot{l}_{in}} = -\frac{A(s)R}{l + sRC + A(s)} \qquad A(s) = \frac{A_{o}}{l + \frac{s}{h_{o}}}$$

$$\frac{V_{out}}{\dot{L}_{in}} = -\frac{RA_{o}}{(sRC+1)(l + \frac{s}{h_{o}}) + A_{o}}$$

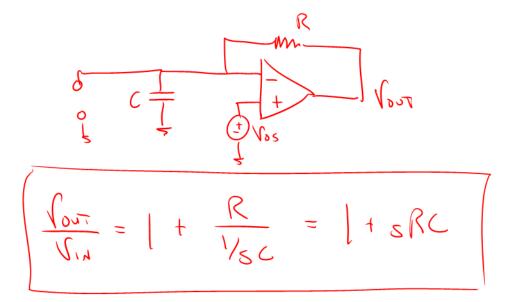

c) Assume the opamp has finite offset voltage  $V_{OS}$ . Find an expression for the transfer function  $H(s)=v_{OUT}/V_{OS}$  when  $i_{IN}=0$ .

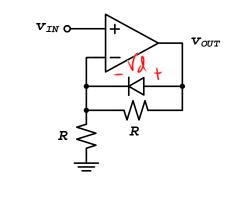

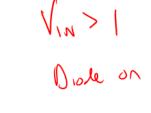

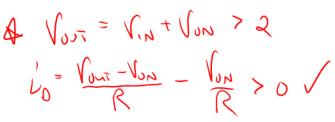

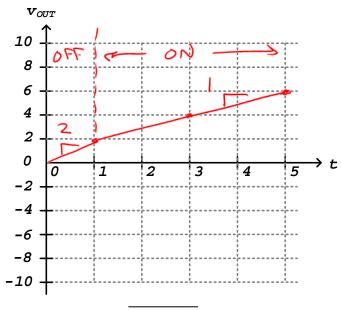

**Problem 3 (15 Points):** Use the following circuit for this problem. Assume the opamp is ideal, and use the constant-voltage-drop (CVD) model for the diode with  $V_{ON}=1\ V$ . Plot the output voltage  $v_{OUT}$  on the graph provided below for an input voltage  $v_{IN}$  of a ramp from 0 to  $5\ V$  as shown on the graph below.

$$\sqrt{l} = \sqrt{l} =$$

Page 8 of 12

**Problem 4 (30 Points):** Use the parameters from the table below for all parts of this problem. Assume  $v_{SB}=0V$  unless otherwise shown.

|                 | NMOS             | PMOS             |

|-----------------|------------------|------------------|

| $V_{th}$        | 1 <i>V</i>       | -1V              |

| $K_{n,p}$       | $500  \mu A/V^2$ | $250  \mu A/V^2$ |

| $\lambda_{n,p}$ | 0                | 0                |

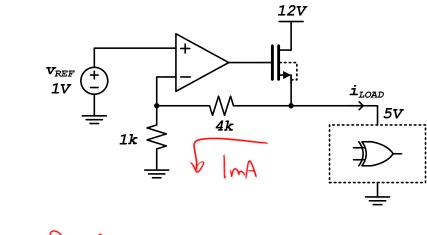

a) The following circuit is a linear voltage regulator providing a constant 5V supply voltage to a digital logic chip. Assuming the NMOS is in the Saturation region, calculate the value of  $v_{GS}$  of the NMOS when  $i_{LOAD}=1mA$ .

$$\int_{0}^{\infty} = 2 \, \text{mA}$$

$$\int_{0}^{\infty} = \frac{1}{2} \, \text{kn} \left( \sqrt{\text{ks} - \text{V+n}} \right)^{2} = 2 \, \text{mA}$$

$$\int_{0}^{\infty} \sqrt{\text{ks}} = 3.83 \, \text{V}$$

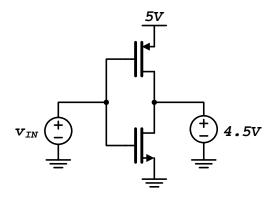

b) For the circuit below, find the range of  $v_{IN}$  that will simultaneously bias the NMOS in the Saturation region, and the PMOS in the Linear region.

$$V_{GS} = V_{IN} - 5$$

$V_{OS} = 4.5 - 5 = -0.5V$

Initials:

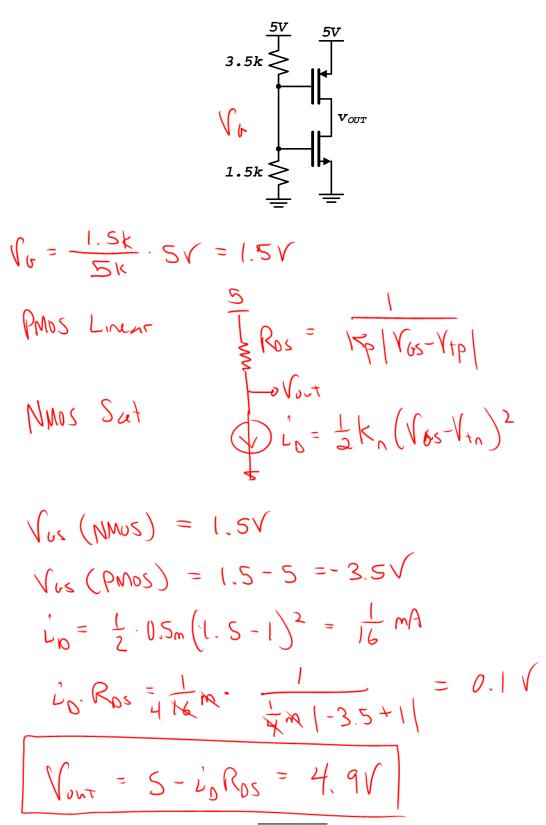

c) For the circuit below, assume the NMOS is in the Saturation region, and the PMOS is in the Linear region. Additionally, approximate the PMOS in Linear with the voltage-controlled resistor model  $R_{DS}$  (good for small  $v_{DS}$ ). Calculate the value for the voltage  $v_{OUT}$ .

Page 11 of 12

(Space for additional work)