## Today's lecture

- What's left?

- Remaining two topic talks.

- Pitches.

- Feature freeze.

- Optional AFSM lecture.

### Asynchronous synthesis te

### What's left?

- 14 April: Outline of course topics, which is useful when preparing for the final.

- 14 April: Submit poster draft PDF via Gradescope for feedback. P/F.

- 17 April: Polish project. Print poster. Practice pitch.

- 18 April

- Demo Day: Come prepared with project, poster, and pitch.

- Submit project report via Gradescope.

- Submit final version of poster via Gradescope.

- Team member evaluation.

- 19 April: Practice exam material posted.

- 26 April: Final exam

- Comprehensive, short.

- Optional review sessions covering no new material.

Robert Dick AFSM Synthesis

| Synchronous vs. asynchronous design<br>Asynchronous synchronous synchronous<br>Example | Synchronous vs. asynchronous design<br>Asynchronous synthesis techniques<br>Example |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Why pitches? Selling your ideas                                                        | Feature freeze                                                                      |

- Actual selling.

- Team building.

- Fundraising.

- Management support.

- Layered approach: 30 second, five minute, one hour.

Robert Dick AFSM Synth

- T1: No new features.

- T2: No new non bug fix code.

- T3: No new code.

- Huge impact on whether demo/product/etc., achieves goal.

Robert Dick

AESM Synth

Synchronous vs. asynchronous design Asynchronous synthesis techniques

Thanks for taking this seriously!

Working on hard problems with people...

- ... who don't really care = torture

- ... who care, lead, push hard, and get results = FUN!

Asynchronous Finite State Machine Synthesis

| Teacher: | Robert Dick      |

|----------|------------------|

| Office:  | 2417-E EECS      |

| Email:   | dickrp@umich.edu |

| Phone:   | 847-530-1824     |

Keep in contact!

13 April 2017

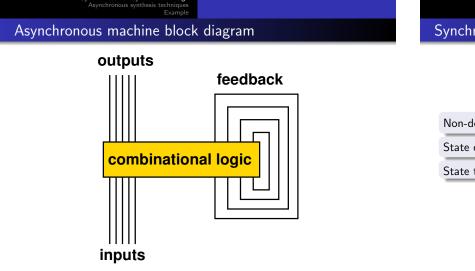

## Synchronous vs. asynchronous design

- Develop fully asynchronous circuits, e.g., microprocessors.

- Why don't people do this often? Poor CAD tool support. Greater design complexity.

- Interface synchronous circuits with different clock periods and phases.

- Interface synchronous systems with asynchronous sensors.

- Methodically design flip-flop and latch like circuits of arbitrary complexity and specifications.

- Synchronous design makes a lot of problems disappear

- Glitches not fatal

- FSM design easier

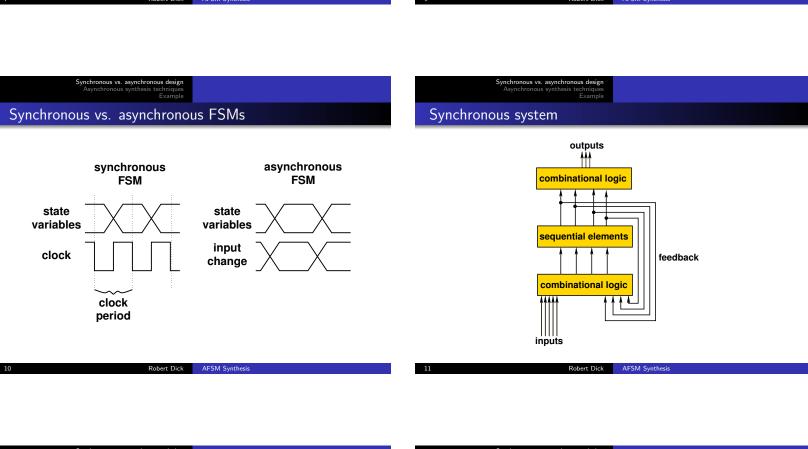

## Synchronous FSM specification

Non-deterministic (multi-input pseudo-)FSA for complex specifications

State diagram

State table

## Synchronous FSM minimization

## Synchronous FSM synthesis

| Implication chart               |  |

|---------------------------------|--|

| Maximal cliques and compatibles |  |

| Prime compatibles               |  |

| Binate covering formulation     |  |

| Minimized state table           |  |

| State variable synthesis  |  |

|---------------------------|--|

| Output variable synthesis |  |

| Technology mapping        |  |

### Synchronous vs. asynchronous design Asynchronous synthesis techniques

## Asynchronous FSM specification

| Non-deterministic (multi-output pseudo-)FSA for complex specifications |

|------------------------------------------------------------------------|

| State diagram, explicitly considering all clock-like inputs            |

| State table                                                            |

| Synchronous vs. | asynchror | nous design |

|-----------------|-----------|-------------|

| Asynchronous    | synthesis | techniques  |

|                 |           | Example     |

## Asynchronous FSM minimization

Implication chart

Maximal cliques and compatibles

Prime compatibles

Binate covering formulation

Minimized state table

Unchanged.

### Asynchronous vs. asynchronous design

Asynchronous FSM synthesis

| State splitting, if necessary                                               |

|-----------------------------------------------------------------------------|

| State assignment, preserving encoding adjacency                             |

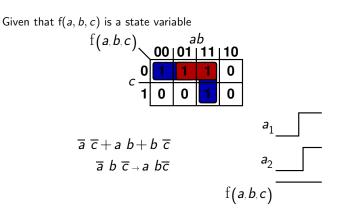

| Hazard-free state variable synthesis                                        |

| Potentially hazard-free output variable synthesis                           |

| Technology mapping                                                          |

| Disable any CAD tool optimizations that may eliminate hazard-covering cubes |

### Asynchronous vs. asynchronous design Asynchronous synthesis techniques

## Asynchronous FSM state assignment

- For synchronous FSMs, state assignment impacts area and power consumption

- For asynchronous FSMs, incorrect state assignment results in incorrect behavior

- A *race* is a condition in which the behavior of the circuit is decided by the relative switching speeds of two state variables

- An asynchronous FSM with races will not behave predictably

- Avoid *critical races*, races which result in different end states depending on variable change order

| Synchronous vs. asynchronous design<br>Asynchronous synthesis techniques               | Synchronous vs. asynchronous design<br>Asynchronous synthesis techniques                                                                                                                                                   |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Example                                                                                | Example                                                                                                                                                                                                                    |

| Incorrect asynchronous assignment                                                      | Asynchronous FSM state assignment                                                                                                                                                                                          |

|                                                                                        | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                      |

|                                                                                        | <ul> <li>Consider 00 → 11 transition</li> <li>Becomes trapped in 01 or 10</li> <li>Which one?</li> <li>Random</li> </ul>                                                                                                   |

| 21 Robert Dick AFSM Synthesis                                                          | 22 Robert Dick AFSM Synthesis                                                                                                                                                                                              |

| Synchronous vs. asynchronous design<br>Asynchronous synthesis techniques               | Synchronous vs. asynchronous design<br>Asynchronous synthesis techniques                                                                                                                                                   |

| Example                                                                                | Example                                                                                                                                                                                                                    |

| Asynchronous FSM adjacency                                                             | Asynchronous FSM adjacency                                                                                                                                                                                                 |

| $ \begin{array}{c} 00\\ 1X\\ 01\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\$ | <ul> <li>Two input bits</li> <li>When a particular input leads to a state, maintaining that input should generally keep one in the state <ul> <li>E.g., 01 for g</li> </ul> </li> <li>Will show exception later</li> </ul> |

### Synchronous vs. asynchronous design Asynchronous synthesis techniques

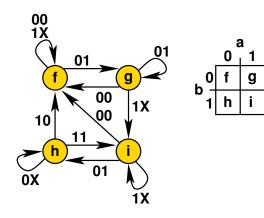

## Asynchronous FSM adjacency

- f adjacent to g, h, and i

- g adjacent to f and i

- h adjacent to f and i

- i adjacent to f, g, and h

- Four states  $\rightarrow \lceil \lg(4) \rceil = 2$  state variables

- However, in 2D space, each point is adjacent to only two others

1 X

AESM S

• Need at least 3D

### Synchronous vs. asynchronous des Asynchronous synthesis techniq Exam

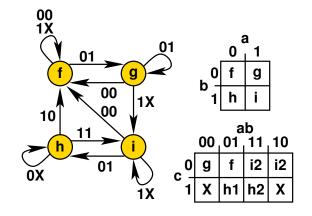

# Asynchronous FSM adjacency

# Asynchronous FSM adjacency

## Asynchronous FSM adjacency

- Need all adjacent states in AFSM to be adjacent

- *i* to *f* transition could be trapped in *g*!

- What to do for a graph with too many connections?

- Split states and hop through some states to reach others

| Synchronous vs. | asynchronous design  |

|-----------------|----------------------|

| Asynchronous    | synthesis techniques |

|                 | Example              |

Asynchronous FSM adjacency

| current        |                | ne    | ext            |                |

|----------------|----------------|-------|----------------|----------------|

| state          |                | sta   | ate            |                |

| State          | 00             | 01    | 10             | 11             |

| f              | f              | g     | f              | f              |

| g              | f              | g     | i2             | i <sub>2</sub> |

| $h_1$          | h <sub>1</sub> | $h_1$ | f              | h <sub>2</sub> |

| $h_2$          | h <sub>2</sub> | $h_2$ | h <sub>1</sub> | i <sub>1</sub> |

| $i_1$          | f              | $h_2$ | i <sub>1</sub> | i <sub>1</sub> |

| i <sub>2</sub> | i <sub>1</sub> | $i_1$ | i <sub>2</sub> | i <sub>2</sub> |

| Synchronous vs. asynchronous design<br>Asynchronous synthesis techniques<br>Example |  |

|-------------------------------------------------------------------------------------|--|

|                                                                                     |  |

## AFSM synthesis redundancy

- Even if AFSM has a fully connected adjacent state assignment there are still additional complications

- State variables must have stable transitions

- E.g., for a SOP implementation, every state pair that is connected in the state transition graph must me covered by at least one cube

Robert Dick AFSM Synth

• Hazards may cause incorrect operation for AFSMs

| Asynchronoi | us synthesis techniques<br>Example |  |

|-------------|------------------------------------|--|

|             |                                    |  |

## AFSM transition stability

### Asynchronous vs. asynchronous design Asynchronous synthesis techniques Example

- AFSMs immediately react to input changes

- No need to worry about clock

- However, design more complicated

- Stability

- Unstable states must have appropriate (no glitches) outputs

- Adjacent states must have adjacent assignments

- Glitches on state variables may be fatal

ynchronous vs. asynchro Asynchronous synthesis

## Other examples

35

|    | tput 1 iff L is low and M was high at some time during most<br>ent L high period |

|----|----------------------------------------------------------------------------------|

| Ou | tput 0 otherwise                                                                 |

|    |                                                                                  |

| 0  | an inverting D flip-flop that is simultaneously rising-edge and dge triggered    |

Robert Dick AFSM Synth

Design a falling edge triggered D flip-flop

Robert Dick AFSM Synthesis

echniques Example