# Review

# EECS 373 Design of Microprocessor-Based Systems

| R     | )   |

|-------|-----|

| R     | 1   |

| R     | 2   |

| R     | 3   |

| R     | 4   |

| R     | 5   |

| R     | 6   |

| R     | 7   |

| R     | 3   |

| R     | 9   |

| R1    | 0   |

| R1    | 1   |

| R1    | 2   |

| R13 ( |     |

| R14 ( | LR) |

| R15 ( | PC) |

| xPS   | SR  |

Robert Dick University of Michigan

Lecture 2: Architecture, Assembly, and ABI

11 September 2017

Many slides from Mark Brehob

- Course staff

- Implementation technology trends

- Application trends

- Course structure and grading

- Debugging

# Outline

- Embedded system

- ISA

- ABI

- Build process

# An embedded system

# Outline

- Embedded system

- ISA

- ABI

- Build process

| 32-bits          |                            | 32-bits                                    |

|------------------|----------------------------|--------------------------------------------|

| R0               |                            | 0xFFF<br>System                            |

| R1<br>R2         |                            | OxE01                                      |

| R3               | mov <mark>r0</mark> , #0x1 | Private peripheral bus - Internal<br>0xE00 |

| R4               |                            | 0xE00                                      |

| R5               |                            | External device 1.0GB                      |

| R6               | ld r1, [r0,#5]             |                                            |

| R7               |                            | 0xA00                                      |

| R8               | a1 ana((a0),E)             | External RAM 1.0GB                         |

| R9               | r1=mem((r0)+5)             |                                            |

| R10              |                            | 0x600                                      |

| R11              | bne loop                   | Peripheral 0.5GB                           |

| R12              |                            | 0x400                                      |

| R13 (SP)         |                            | SRAM 0.5GB                                 |

| R14 (LR)         | sub <mark>s</mark> r2, #1  | 0x200                                      |

| R15 (PC)<br>xPSR | -                          | Code 0.5GB                                 |

|                  |                            | 0×000                                      |

| Endianess        |                            | Endianess                                  |

|                  | 31 30 29 28 27 26          | 0                                          |

|                  | N Z C V Q RESERVED         |                                            |

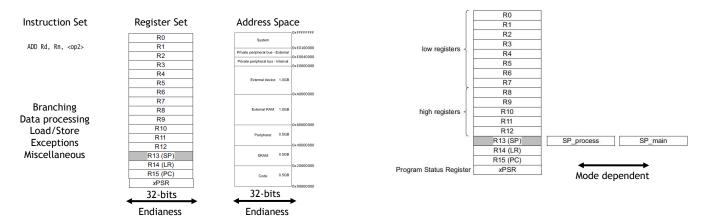

Major elements of an Instruction Set Architecture (registers, memory, word size, endianess, conditions, instructions, addressing modes)

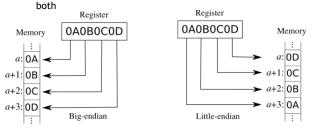

# Endianness

# Addressing: Big Endian vs Little Endian (370 slide)

# • Endianness: ordering of bytes within a word

- Little increasing numeric significance with increasing memory addresses

- Big the opposite, most significant byte first

- MIPS is big endian, x86 is little endian, ARM supports

# Instruction encoding

- MICHIGAN

- Instructions are encoded in machine language opcodes

Little-Endian (default)

uint8\_t a = 1; uint8\_t b = 2; uint16\_t c = 255; // 0x00FF uint32\_t d = 0x12345678;

Big-Endian

uint8\_t a = 1; uint8\_t b = 2; uint16\_t c = 255; // 0x00FF uint32\_t d = 0x12345678;

- LSB is at lower address

- MSB is at lower address

Memory Value Offset (LSB) (MSB)

0x0004 78 56 34 12

Memory Value Offset (LSB) (MSB)

0x0000 01 02 00 FF

0x0004 12 34 56 78

01 02 FF 00

|       | strı<br>vs r |     |       |      |       |      |     |     |          |     |     |      |     | ле<br>900   |     |      | Me<br>(L |       | -   |    | alue<br>SB) |

|-------|--------------|-----|-------|------|-------|------|-----|-----|----------|-----|-----|------|-----|-------------|-----|------|----------|-------|-----|----|-------------|

|       |              |     | -     |      |       | (    | m   | sb  | )        | 1   |     |      | ÷., | (           | 1s  | b)   | 0a       | 20    | ) ( | 00 | 21          |

| -     | vs r         | .1  | +     | 0    |       |      |     |     | <i>.</i> | a I | 0   | 01   | 100 | <b>9</b> 00 |     |      |          |       |     |    |             |

| 10    | v 5 I        | -   | ד ,   | .0   |       | 0    | 0.  | - 1 | 0        | -   | 0   |      | 196 |             | 000 |      |          |       |     |    |             |

|       | Enco         | din | a T1  |      | All v | ani  |     |     | he       | ть. | m   | TO   |     |             |     |      |          |       |     |    |             |

| S     | MOVS <       |     | -     |      | All V | ersn | ous | 011 | ще       | Im  | and | 1.57 | 16  |             | Out | side | IT blo   | rk    |     |    |             |

| ARM   | MOV <c></c>  |     |       |      |       |      |     |     |          |     |     |      |     |             | 1.5 |      | T block  | 0.000 |     |    |             |

|       |              |     |       | 10 9 | 8 -   | 6    | 5   | 4   | 2        |     | 1   | 0    |     |             |     |      |          |       |     |    |             |

| ~     | 0 0          | -   | 22.52 |      | -     | 0    | -   | im  |          | -   | -   | Ť    |     |             |     |      |          |       |     |    |             |

| ARMv7 |              |     | 0 0   | Rd   |       |      |     | Im  | mð       |     |     |      |     |             |     |      |          |       |     |    |             |

# Assembly example

| data: |                                    |

|-------|------------------------------------|

|       | .byte 0x12, 20, 0x20, -1           |

| func: |                                    |

|       | mov r0, #0<br>mov r4, #0           |

|       | movw r1, #:lower16:data            |

|       | <pre>movt r1, #:upper16:data</pre> |

| top:  |                                    |

|       | ldrb r2, [r1],#1                   |

|       | add r1, r1, #1                     |

|       | add r4, r4, r2                     |

|       | add r0, r0, #1                     |

|       | cmp r0, #4                         |

|       | bne top                            |

# Instructions used

- mov

- Moves data from register or immediate.

- Or also from shifted register or immediate!

- the mov assembly instruction maps to a bunch of different encodings!

- If immediate it might be a 16-bit or 32-bit instruction.

Not all values possible

- why?

- movw

- Actually an alias to mov.

- "w" is "wide"

- hints at 16-bit immediate.

# From the ARMv7-M Architecture Reference Manual (posted on the website under references)

Thumb Instruction Details

| A6.7.76 | MOV (register)                                                                                                                                                                                                                                                        |                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|         | Move (register) copies a value from a register to the destination register. It can optionally updat condition flags based on the value.                                                                                                                               | e the                                                             |

|         | Encoding T1 ARMv6-M, ARMv7-M If 48ds and 48ns both from R0-R7, otherwise all versions of the Thumb ISA.                                                                                                                                                               |                                                                   |

|         | MOV <c> <rd>, <rm> If <rd> is the PC, must be outside or last in I</rd></rm></rd></c>                                                                                                                                                                                 | T block                                                           |

|         | 15         14         13         12         11         10         9         8         7         6         5         4         3         2         1         0           0         1         0         0         1         1         0         D         Rm         Rd |                                                                   |

|         | d = UInt(D:Rd); m = UInt(Rm); setflags = FALSE;<br>if d == 15 && InITBlock() && !LastInITBlock() then UNPREDICTABLE;                                                                                                                                                  |                                                                   |

|         | Encoding T2         All versions of the Thumb ISA.           MOVS <rd>, <rm>         (formerly LSL-<rd>, <rm>, #0)         Not permitted inside IT bloc</rm></rd></rm></rd>                                                                                           | k                                                                 |

|         | 15         14         13         12         11         10         9         8         7         6         5         4         3         2         1         0           0         0         0         0         0         0         0         0         Rm         Rd | There are similar entries for                                     |

|         | <pre>d = UInt(Rd); m = UInt(Rm); setflags = TRUE;<br/>if InITBlock() then UNPREDICIABLE;</pre>                                                                                                                                                                        | move immediate, move shifted<br>(which actually maps to different |

|         | Encoding T3 ARMv7-M<br>M0V{\$} <c>.w </c>                                                                                                                                                                                                                             | instructions), etc.                                               |

|         | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                 | 8 2 1 0<br>Rm                                                     |

|         | d = UInt(Rd); n = UInt(Rm); setFlags = (S = '1');<br>if setFlags && (d IN (13,15)    n IN (13,15}); then UNPREDICTABLE;<br>if !setFlags && (d == 15    n == 15    (d == 13 && n == 13)) then UNPREDICTABLE;                                                           |                                                                   |

# Directives

- #:lower16:data

- What does that do?

- Why?

#### A6.7.78 MOVT

Move Top writes an immediate value to the top halfword of the destination register. It does not affect the contents of the bottom halfword.

MOVT<c> <Rd>,#<imm16> 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 1 1 1 1 0 i 1 0 1 1 0 0 imm4 0 imm3 Rd imm8

d = UInt(Rd); imm16 = imm4:i:imm3:imm8; if d IN {13.15} then UNPREDICTABLE;

#### Assembler syntax

MOVT<c><q> <Rd>, #<imm16>

where:

See Standard assembler syntax fields on page A6-7. <c><q>

Specifies the destination register.

Specifies the immediate value to be written to <Rd>. It must be in the range 0-65535. <imm16>

#### Operation

<Rd>

if ConditionPassed() then EncodingSpecificOperations(); R[d]<31:16> = imm16; // R[d]<15:0> unchanged

Exceptions

None.

# Loads

- Idrb -- Load register byte

- Note this takes an 8-bit value and moves it into a 32bit location!

- Zeros out the top 24 bits.

- Idrsb -- Load register signed byte

- Note this also takes an 8-bit value and moves it into a 32-bit location!

- Uses sign extension for the top 24 bits.

# Addressing modes

- Offset addressing

- Offset is added or subtracted from base register

- Result used as effective address for memory access

- [<Rn>, <offset>]

- Pre-indexed addressing

- Offset is applied to base register

- Result used as effective address for memory access

- Result written back into base register

- [<Rn>, <offset>]!

- Post-indexed addressing

- The address from the base register is used as the EA

- The offset is applied to the base and then written back

- [<Rn>], <offset>

# An ISA defines the hardware/software interface

## ARM architecture roadmap

- ٠ A contract between architects and programmers

- Register set •

- Instruction set

- Addressing modes Word size

- -

- Data formats

- Operating modes

- Condition codes

- Calling conventions

- Really not part of the ISA (usually)

- Rather part of the ABI

- -But the ISA often provides meaningful support.

ARM946E-S ARM966E-S Improved ARM/Thumb

Interworking DSP instructions Extensions: Jazelle (5TEJ)

ARM926EJ-S

ARM1136JF-S ARM1176JZF-S ARM11 MPCore SIMD Instructions Unaligned data support Extensions: Thumb-2 (6T2) TrustZone (6Z) Multicore (6K)

- Skim pages 1-84.

- Read pages 85-154.

- Refer to pages 154-end.

# A quick comment on the ISA: From: ARMv7-M Architecture Reference Manual

#### A4.1 About the instruction set

ARMv7-M supports a large number of 32-bit instructions that were introduced as Thumb-2 technology into the Thumb instruction set. Much of the functionality available is identical to the ARM instruction set supported alongside the Thumb instruction set in ARMv6T2 and other ARMv7 profiles. This chapter describes the functionality available in the ARMv7-M Thumb instruction set, and the Unified Assembler Language (UAL) that can be assembled to either the Thumb or ARM instruction sets.

Thumb instructions are either 16-bit or 32-bit, and are aligned on a two-byte boundary. 16-bit and 32-bit instructions can be intermixed freely. Many common operations are most efficiently executed using 16-bit instructions. However:

- Most 16-bit instructions can only access eight of the general purpose registers, R0-R7. These are

known as the low registers. A small number of 16-bit instructions can access the high registers,

R8-R15.

- Many operations that would require two or more 16-bit instructions can be more efficiently executed with a single 32-bit instruction.

The ARM and Thumb instruction sets are designed to *interwork* freely. Because ARMv7-M only supports Thumb instructions, interworking instructions in ARMv7-M must only reference Thumb state execution, see ARMv7-M and interworking support for more details.

In addition, see:

•

- Chapter A5 Thumb Instruction Set Encoding for encoding details of the Thumb instruction set

- Chapter A6 Thumb Instruction Details for detailed descriptions of the instructions.

# ARM Cortex-M3 ISA

# Registers

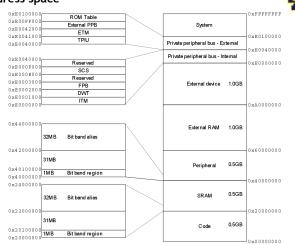

## Address space

# Instruction encoding: ADD immediate

Encoding T1 All versions of the Thumb ISA. A005 dds,dss,dss,deimb A00c dds,dss,efcimb 15 14 13 12 11 0 9 8 7 6 5 4 3 2 1 0 10 0 0 1 1 1 0 9 R 7 6 5 A 3 2 1 0

Encoding T2

All versions of the Thumb ISA.

A005 <ddm., #cim8>

A00cc>

ddm., #cim8>

1514315211109

8

7

6

5

4

3

2

1

0

1514315211109

8

7

6

5

4

3

2

1

0

Encoding T3 ARM/7.M #05[5(-o.) # db-, dro. #.costro 15 H 33 12 11 0 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 1 1 1 1 0 | 0 9 1 0 0 0 5 Rn | 0 imm3 Rd imm8

| A6.7.3 | ADD | (immediate) |  |

|--------|-----|-------------|--|

|        |     |             |  |

ADD<c> <Rd>, <Rn>, #<imm3>

ADD<c> <Rdn>,#<imn8>

Encoding T1 All versions of the Thumb ISA. ADDS <Rd>,<Rr>,#<imi3>

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

1

1

0

imm3

Rn

Rd

Encoding T2 All versions of the Thumb ISA. ADDS <Rdn>,#<im8>

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

1

1

0

Rdn

imm8

imm8

Encoding T3 ARMv7-M ADD{\$}<c>.W <Rd>, <Rn>, #<const>

Encoding T4 ARMv7-M ADDW<> <Rd>, <Rn>, #<im12>

This instruction adds an immediate value to a register value, and writes the result to the desti-It can optionally update the condition flags based on the result.

d = UInt(Rd); n = UInt(Rn); setflags = !InITBlock(); imm32 = ZeroExtend(imm3, 32);

d = UInt(Rdn); n = UInt(Rdn); setflags = !InITBlock(); imm32 = ZeroExtend(imm8, 32);

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

1

1

0

1

0

0

S

Rn

0

imma

Rd

imma

if Rd = '1111' && S = '1' then SEE OWN (immediate); if Rn = '1101' && S = '1' then SEE OWN (immediate); if dn = '1101' then SEE ADM (SP Plus immediate); d = Ulat(Rd); set = Ulat(Rd); set = Ulat(Rd); set = Ulat(Rd); set = '1'; imm32 = ThumbExpandIrm(i:imm3:imm8); if d IN (13,15) || n = 15 then UMPREDICTABLE;

if Rn == 'llll' then SEE ADR; if Rn == 'llll' then SEE ADD (SP plus immediate); d = Uln(tAD); n = Uln(tAD); setTlags = FALSE; imm32 = ZeroExtend(i:imm3;imm8, 32); if d IN (13,15) then UNWFRDCIALE;

Notes

Thumb permits use of a modified immediate constant or a zero-extended 12-bit immediate constant.

Sets flags. Like ADD but with no destination register.

Sets flags. Like SUB but with no destination register.

First operand is the PC. Second operand is an immediate constant. Thumb supports a zero-extended 12-bit immediate constant. Operation is an addition or a subtraction.

Has only one operand, with the same options as the second operand in most of these instructions. If the operand is a shifted register, the instruction is an LSL, LSR, ASR, or ROR instruction instead. See Shift instructions on page A4-10 for details.

Thumb permits use of a modified immediate constant or a zero-extended 16-bit immediate constant.

Has only one operand, with the same options as the second operand in most of these instructions.

Outside IT block.

Inside IT block.

Outside IT block

Inside IT block.

# Branch

#### Table A4-1 Branch instructions

| Usage                                                        | Range                                                                                                                                                                                                                                  |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Branch to target address                                     | +/-1 MB                                                                                                                                                                                                                                |

| Compare and Branch on Nonzero,<br>Compare and Branch on Zero | 0-126 B                                                                                                                                                                                                                                |

| Call a subroutine                                            | +/-16 MB                                                                                                                                                                                                                               |

| Call a subroutine, optionally change instruction set         | Any                                                                                                                                                                                                                                    |

| Branch to target address, change instruction set             | Any                                                                                                                                                                                                                                    |

| Table Branch (byte offsets)                                  | 0-510 B                                                                                                                                                                                                                                |

| Table Branch (halfword offsets)                              | 0-131070 E                                                                                                                                                                                                                             |

|                                                              | Branch to target address Compare and Branch on Nonzero, Compare and Branch on Zero Call a subroutine Call a subroutine, optionally change instruction set Branch to target address, change instruction set Table Branch (byte offsets) |

#### Data processing instructions

Mnemonic Instruction

Add

Add with Carry

Bitwise AND

Compare

Bitwise NOT

Dimin OD NOT

Bitwise Bit Clear

Compare Negative

Bitwise Exclusive OR

Copies operand to destination

Form PC-relative Address

ADC

ADD

ADR

AND

BIC

CMN

CMP

EOR

MOV

MVN

ODM

#### Load/store instructions

| Load | Store | Load | Store |

|------|-------|------|-------|

|      |       |      |       |

Table A4-10 Load and store instructions

| Data type                | Load  | Store | Load<br>unprivileged | Store<br>unprivileged | Load<br>exclusive | Store<br>exclusive |

|--------------------------|-------|-------|----------------------|-----------------------|-------------------|--------------------|

| 32-bit word              | LDR   | STR   | LDRT                 | STRT                  | LDREX             | STREX              |

| 16-bit halfword          | -     | STRH  | -                    | STRHT                 | -                 | STREXH             |

| 16-bit unsigned halfword | LDRH  | -     | LDRHT                | -                     | LDREXH            | -                  |

| 16-bit signed halfword   | LDRSH | -     | LDRSHT               | -                     | -                 | -                  |

| 8-bit byte               | -     | STRB  | -                    | STRBT                 | -                 | STREXB             |

| 8-bit unsigned byte      | LDRB  | -     | LDRBT                | -                     | LDREXB            | -                  |

| 8-bit signed byte        | LDRSB | -     | LDRSBT               | -                     | -                 | -                  |

| two 32-bit words         | LDRD  | STRD  | -                    | -                     | -                 | -                  |

|                          |       |       |                      |                       |                   |                    |

Many more!

### **Miscellaneous instructions**

| Instruction                                        | See                                     |

|----------------------------------------------------|-----------------------------------------|

| Clear Exclusive                                    | CLREX on page A6-56                     |

| Debug hint                                         | DBG on page A6-67                       |

| Data Memory Barrier                                | DMB on page A6-68                       |

| Data Synchronization Barrier                       | DSB on page A6-70                       |

| Instruction Synchronization Barrier                | ISB on page A6-76                       |

| If Then (makes following instructions conditional) | IT on page A6-78                        |

| No Operation                                       | NOP on page A6-167                      |

| Preload Data                                       | PLD, PLDW (immediate) on page A6-176    |

|                                                    | PLD (register) on page A6-180           |

| Preload Instruction                                | PLI (immediate, literal) on page A6-182 |

|                                                    | PLI (register) on page A6-184           |

| Send Event                                         | SEV on page A6-212                      |

| Supervisor Call                                    | SVC (formerly SWI) on page A6-252       |

| Wait for Event                                     | WFE on page A6-276                      |

| Wait for Interrupt                                 | WFI on page A6-277                      |

| Yield                                              | YIELD on page A6-278                    |

# Addressing Modes (again)

- Offset Addressing

- Offset is added or subtracted from base register

- -Result used as effective address for memory access

- [<Rn>, <offset>]

- Pre-indexed Addressing

- Offset is applied to base register

- Result used as effective address for memory access

- Result written back into base register

- [<Rn>, <offset>]!

- Post-indexed Addressing

- The address from the base register is used as the EA

- The offset is applied to the base and then written back

- [<Rn>], <offset>

# <offset> options

- An immediate constant

- #10

- An index register <Rm>

- A shifted index register - <Rm>, LSL #<shift>

- Lots of weird options...

#### A5.3.2 Modified immediate constants in Thumb instructions

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 i i a b c d e f g h Table A5-11 shows the range of modified immediate constants available in Thumb data processing instructions, and how they are encoded in the a, b, c, d, e, f, g, h, i, and imm3 fields in the instruction

#### Table A5-11 Encoding of modified immediates in Thumb data-processing instructions

| i:imm3:a | <const> a</const>                                           |

|----------|-------------------------------------------------------------|

| 0000x    | 00000000 00000000 00000000 abcdefgh                         |

| 0001x    | 00000000 abcdefgh 00000000 abcdefgh <sup>b</sup>            |

| 0010x    | abcdefgh 00000000 abcdefgh 00000000 <sup>b</sup>            |

| 0011x    | abcdefgh abcdefgh abcdefgh abcdefgh <sup>b</sup>            |

| 01000    | 1bcdefgh 00000000 00000000 00000000                         |

| 01001    | 01bcdefg h0000000 00000000 00000000                         |

| 01010    | 001bcdef gh000000 00000000 00000000                         |

| 01011    | 0001bcde fgh00000 00000000 00000000                         |

|          |                                                             |

|          | <ul> <li>8-bit values shifted to other positions</li> </ul> |

|          | 14 M                                                        |

| 11101    | 00000000 00000000 000001bc defgh000                         |

| 11110    | 00000000 00000000 0000001b cdefgh00                         |

| 11111    | 00000000 00000000 00000001 bcdefgh0                         |

b. UNPREDICTABLE if abcdefgh == 00000000.

# Application Program Status Register (APSR)

#### A2.3.2 The Application Program Status Register (APSR)

Program status is reported in the 32-bit Application Program Status Register (APSR), where the defined bits break down into a set of flags as follows: 31 30 29 28 27 26

|  | ΝZ | c v | Q | RESERVED |

|--|----|-----|---|----------|

|--|----|-----|---|----------|

APSR bit fields are in the following two categories:

Reserved bits are allocated to system features or are available for future expansion. Further information on currently allocated reserved bits is available in *The special-purpose program status registers* (*rSR*) on page B1-3. Application levels offware must ignore values read from reserved bits and preserve their value on a write. The bits are defined as UNK/SBZP.

- Flags that can be set by many instructions: Figst ball Negative condition code flag. Set to bit [31] of the result of the instruction. If the result is regarded as a two's complement signed integer, then N==1 if the result is negative and N = 0 if it is positive or zero.

- Z, bit [30] Zero condition code flag. Set to 1 if the result of the instruction is zero, and to 0 otherwise. A result of zero often indicates an equal result from a comparison.

- C, bit [29] Carry condition code flag. Set to 1 if the instruction results in a carry condition, for example an unsigned overflow on an addition.

- V, bit [28] Overflow condition code flag. Set to 1 if the instruction results in an overflow condition, for example a signed overflow on an addition.

- Q, bit [27] Set to 1 if an SSAT or USAT instruction changes (saturates) the input value for the signed or unsigned range of the result.

# Updating the APSR

- SUB Rx, Ry

- Rx = Rx Ry

- APSR unchanged

- SUBS

- Rx = Rx Ry

- APSR N, Z, C, V updated

- ADD Rx, Ry

- Rx = Rx + Ry

- APSR unchanged

- ADDS

- Rx = Rx + Ry

- APSR N, Z, C, V updated

# Overflow and carry in APSR

- unsigned\_sum = UInt(x) + UInt(y) + UInt(carry\_in);

- signed\_sum = SInt(x) + SInt(y) + UInt(carry\_in);

- result = unsigned\_sum<N-1:0>; // == signed\_sum<N-1:0>

- carry\_out = if UInt(result) == unsigned\_sum then '0' else '1';

- overflow = if SInt(result) == signed\_sum then '0' else '1';

| cond | Mnemonic<br>extension | Meaning (integer)            | Meaning (floating-point) <sup>ab</sup> | Condition flags                                 |

|------|-----------------------|------------------------------|----------------------------------------|-------------------------------------------------|

| 0000 | EQ                    | Equal                        | Equal                                  | Z == 1                                          |

| 0001 | NE                    | Not equal                    | Not equal, or unordered                | Z == 0                                          |

| 0010 | CS °                  | Carry set                    | Greater than, equal, or unordered      | C === 1                                         |

| 0011 | CC d                  | Carry clear                  | Less than                              | C == 0                                          |

| 0100 | MI                    | Minus, negative              | Less than                              | N == 1                                          |

| 0101 | PL                    | Plus, positive or zero       | Greater than, equal, or unordered      | N == 0                                          |

| 0110 | VS                    | Overflow                     | Unordered                              | V == 1                                          |

| 0111 | VC                    | No overflow                  | Not unordered                          | V == 0                                          |

| 1000 | HI                    | Unsigned higher              | Greater than, or unordered             | C == 1 and Z == 0                               |

| 1001 | LS                    | Unsigned lower or same       | Less than or equal                     | $C \mathrel{==} 0 \text{ or } Z \mathrel{==} 1$ |

| 1010 | GE                    | Signed greater than or equal | Greater than or equal                  | N == V                                          |

| 1011 | LT                    | Signed less than             | Less than, or unordered                | $N \mathrel{!=} V$                              |

| 1100 | GT                    | Signed greater than          | Greater than                           | Z == 0 and $N == V$                             |

| 1101 | LE                    | Signed less than or equal    | Less than, equal, or unordered         | $Z == 1 \text{ or } N \mathrel{!=} V$           |

| 1110 | None (AL) e           | Always (unconditional)       | Always (unconditional)                 | Any                                             |

- Onvorcent means treas one rate operation.

ARM/-7A means it reast one rate operation.

B( unsigned higher or same) is a synonym for CS.

U (unsigned lower) is a synonym for CC.

E Al is an optical memoria extension for always, except in IT instructions. See IT on page A6-

- n for cc. nsion for always, except in IT instructions. See IT on page A6-78 for details.

# The ARM architecture "books" for this class

The ARM software tools "books" for this class

#

# Outline

- Embedded system

- <del>ISA</del>

- ABI

- Build process

# ABI summary

# Detailed version

- Pass: r0-r3

- Return: r0 or r0-r1

- Callee saved variables: r4-r8, r11, maybe r9, r10

- Static base: r9

- Stack limit checking: r10

- Veneers, scratch: r12

- Stack pointer: r13

- Link register (function call return address): r14

- Program counter: r15

# Simple version

- Callee preserves r4-r11 and r13

- Caller preserves r0-r3

# ABI details

- 1. A subroutine must preserve the contents of the registers r4-r8, r11, maybe r9-r10

- Arguments are passed though r0 to r3

If you need more, we put a pointer into memory in one of the registers.

- 3. Return value is placed in r0 or r0-r1

- 4. Allocate space on stack as needed. Use it as needed.

- Reset stack pointer when done

- Word align

# Outline

- Embedded system

- ISA

- ABI

- Build process

# An ARM assembly language program for GNU

\_start:

start:

loop:

.text .syntax unified .thumb .global \_start .type start, %function

.equSTACK\_TOP, 0x20000800

.word STACK\_TOP, start

movs r0, #10 movs r1, #0

adds r1, r0 subs r0, #1 bne loop deadloop: b .end

deadloop

# A simple Makefile

all:

. arm-none-eabi-as -mcpu=cortex-m3 -mthumb example1.s -o example1.o arm-none-eabi-ld -Ttext 0x0 -o example1.out example1.o arm-none-eabi-objcopy -Obinary example1.out example.bin arm-none-eabi-objdump -S example1.out > example1.list

# An ARM assembly language program for GNU

| .equ STACK_TOP, 0x20000800<br>.text<br>.syntax unified<br>.thumb<br>.global _start<br>.type start, %function |

|--------------------------------------------------------------------------------------------------------------|

| start:                                                                                                       |

| .word STACK TOP, start                                                                                       |

| start:                                                                                                       |

|                                                                                                              |

| movs r0, #10                                                                                                 |

| movs r1, #0                                                                                                  |

| loop:                                                                                                        |

| adds r1, r0                                                                                                  |

| subs r0, #1                                                                                                  |

| bne loop                                                                                                     |

| deadloop:                                                                                                    |

| b deadloop                                                                                                   |

| •                                                                                                            |

| .end                                                                                                         |

|                                                                                                              |

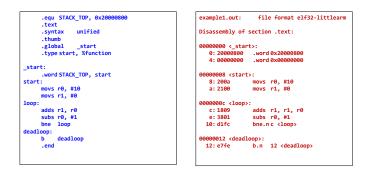

# Disassembled object code

example1.out:

Disassembly of section .text: 00000000 <\_start>:

file format elf32-littlearm

| 0:      | 20000800                                | .word 0x20000800             |

|---------|-----------------------------------------|------------------------------|

| 4:      | 000000000000000000000000000000000000000 | .word 0x00000000             |

|         |                                         |                              |

| 0000000 | 08 <start>:</start>                     |                              |

| 8:      | 200a                                    | movs r0, #10                 |

| a:      | 2100                                    | movs r1, #0                  |

|         |                                         |                              |

| 000000  | c <loop>:</loop>                        |                              |

| с:      | 1809                                    | adds r1, r1, r0              |

| e:      | 3801                                    | subs r0, #1                  |

| 10:     | d1fc                                    | bne.n c <loop></loop>        |

|         |                                         |                              |

| 0000001 | 2 <deadloop></deadloop>                 | :                            |

| 12:     | e7fe                                    | b.n 12 <deadloop></deadloop> |

|         |                                         |                              |

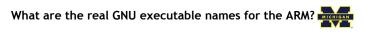

- · Just add the prefix "arm-none-eabi-" prefix

- Assembler (as) ٠

- arm-none-eabi-as

- Linker (ld) - arm-none-eabi-ld

- Object copy (objcopy) arm-none-eabi-objcopy

- Object dump (objdump)

- arm-none-eabi-objdump C Compiler (gcc)

- arm-none-eabi-gcc •

- C++ Compiler (g++) - arm-none-eabi-g++

# A simple (hardcoded) Makefile example

all: arm-none-eabi-as -mcpu=cortex-m3 -mthumb example1.s -o example1.o arm-none-eabi-ld -Ttext 0x0 -o example1.out example1.o arm-none-eabi-objcopy -Obinary example1.out example1.bin arm-none-eabi-objdump -S example1.out > example1.lst

all: arm-none-eabi-as -mcpu=cortex-m3 -mthumb example1.s -o example1.o arm-none-eabi-ld -Ttext 0x0 -o example1.out example1.o arm-none-eabi-objcopy -Obinary example1.out example1.bin arm-none-eabi-objdump -S example1.out > example1.lst

# Elements of assembly language program?

| .equSTACK_TOP, 0x20000800 | <pre>/* Equates symbol to value */</pre>       |

|---------------------------|------------------------------------------------|

| .text                     | <pre>/* Tells AS to assemble region */</pre>   |

| .syntax unified           | /* Means language is ARM UAL */                |

| .thumb                    | /* Means ARM ISA is Thumb */                   |

| .global _start            | <pre>/* .global exposes symbol */</pre>        |

|                           | <pre>/* _start label is the beginning */</pre> |

|                           | <pre>/*of the program region */</pre>          |

| .type start, %function    | <pre>/* Specifies start is a function */</pre> |

|                           | /* start label is reset handler */             |

| _start:                   |                                                |

| .word STACK_TOP, start    | /* Inserts word 0x20000 <mark>800</mark> */    |

|                           | /* Inserts word (start) */                     |

| start:                    |                                                |

| movs r0, #10              | /* We've seen the rest */                      |

| movs r1, #0               |                                                |

| loop:                     |                                                |

| adds r1, r0               |                                                |

| subs r0, #1               |                                                |

| bne loop                  |                                                |

| deadloop:                 |                                                |

| b deadloop                |                                                |

| .end                      |                                                |

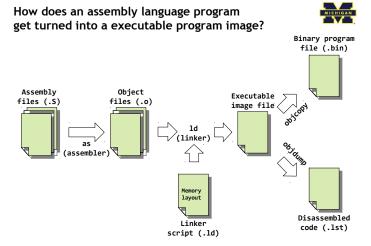

# How are assembly files assembled?

- \$ arm-none-eabi-as

- Useful options

- -mcpu

- -mthumb

- -0

\$ arm-none-eabi-as -mcpu=cortex-m3 -mthumb example1.s -o example1.o

+ link)

ſĽÌ

Memory lavout

Linker

script (.ld)

ob jai

Disassembled Code (.1st)

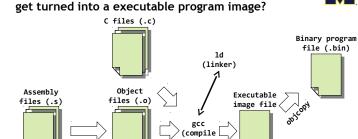

How does a mixed C/Assembly program

as

(assembler)

$\overline{}$

Library object files (.o)

| Register | Synonym | Special        | Role in the procedure call standard                                                   |

|----------|---------|----------------|---------------------------------------------------------------------------------------|

| r15      |         | PC             | The Program Counter.                                                                  |

| r14      |         | LR             | The Link Register.                                                                    |

| r13      |         | SP             | The Stack Pointer.                                                                    |

| r12      |         | IP             | The Intra-Procedure-call scratch register.                                            |

| r11      | v8      |                | Variable-register 8.                                                                  |

| r10      | v7      |                | Variable-register 7.                                                                  |

| r9       |         | v6<br>SB<br>TR | Platform register.<br>The meaning of this register is defined by the platform standar |

| r8       | v5      |                | Variable-register 5.                                                                  |

| r7       | v4      |                | Variable register 4.                                                                  |

| r6       | v3      |                | Variable register 3.                                                                  |

| r5       | v2      |                | Variable register 2.                                                                  |

| r4       | v1      |                | Variable register 1.                                                                  |

| r3       | a4      |                | Argument / scratch register 4.                                                        |

| r2       | a3      |                | Argument / scratch register 3.                                                        |

| r1       | a2      |                | Argument / result / scratch register 2.                                               |

| rO       | a1      |                | Argument / result / scratch register 1.                                               |

Done.