1

#### Outline

## **EECS 373 Design of Microprocessor-Based Systems**

**Robert Dick** University of Michigan

Lecture 9: Serial buses, ADCs, and DACs

#### 2 February 2017

Slides inherited from Mark Brehob.

- Context and review

- Serial buses

- UART

- SPI

- I2C

- ADCs and DACs

- Fundamentals

- Operation

#### **Context and review**

- Timers

- Oscillator, counter, ISR, (OS routines,) library, application.

- PWM a useful application. • Virtualization: use SW to increase apparent number of HW

- timers. Hazards

- Fundamental definitions.

- Problems they cause.

- Side-stepping them.

- · Synchronous systems.

- Pre-syncing signals using flip-flops.

- Directly addressing them.

- · Logic design techniques. • Setup and hold times

#### Terse project proposals

- Two, each 0.5-1 page in length.

- Due tomorrow.

- See sticky Piazza post for example and uploading instructions.

#### Team formation meeting

- 7:30pm-9pm on 7 Feb.

- 1311 EECS.

- Come prepared to very briefly pitch your project idea if you want to recruit team members.

- Everybody should leave with a team and a topic.

#### Student talks

- Each student will do 5-minute talk in March.

- Can team up with others by scheduling talks contiguously. ٠

4

- See Piazza post for initial (random) schedule. .

- Can change schedule, but follow rules.

- More on this later in course.

#### Outline

- Context and review

- Serial buses

- UART

- SPI

- I2C

- ADCs and DACs

- Fundamentals

- Operation

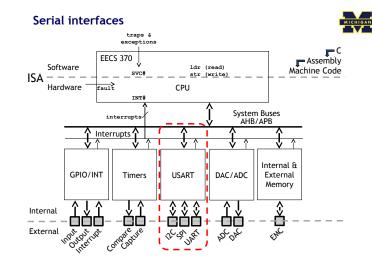

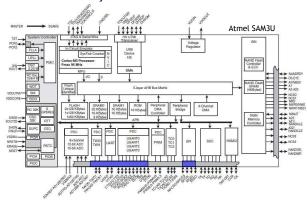

# External memory attaches to the processor via the external memory controller and bus

9

#### **Bus organization**

- Multidrop bus (MDB): all components are connected to the same set of wires.

- In the general case, a bus may have more than one device capable of driving it.

- That is, it may be a "multi-master" bus as discussed earlier.

| Microprocessor           | Control |                |                    |

|--------------------------|---------|----------------|--------------------|

| Control<br>Unit 32 wires | Data    | Memory         |                    |

| Registers 32 wires       | Address |                |                    |

|                          |         | Output<br>Port | 32 data<br>outputs |

|                          |         | Input<br>Port  | 32 data<br>inputs  |

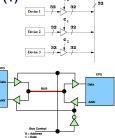

#### Review: Multiple (potential) bus drivers (1)

Tri-state devices, just have one device drive at a time.

Everyone can read though

- Pros:

- Fairly fast, pin-efficient. - Cons:

- Lons:

- Tri-state devices can be slow. - Especially drive-to-tristate?

- Need to be sure two folks not driving at the same time

Let out the magic smoke.

- Most common solution (at least historically)

Ethernet, PCI, etc.

#### Review: Multiple (potential) bus drivers (2)

- MUX

- Many pins.

- Consider a 32-bit bus with 6 potential drivers.

- Generally impractical on PCB.

- More practical on-chip.

#### Review: Multiple (potential) bus drivers (3)

## "pull-up" aka "open

- collector" aka "wired OR" - Wire is pulled high by a

- resistor.

- If any device pulls the

- wire low, it goes low.Pros:

- If two devices both drive

- the bus, it still works!

- Cons:

- Rise-time is long.

Constant power

- consumption.

- Used in I2C, CAN

al to IC External to IC

UART

14

- Universal Asynchronous Receiver/Transmitter

- Translates data between parallel and serial forms.

- UARTs used in conjunction with communication standards such as EIA, RS-232, RS-422 or RS-485.

- Universal

- Data format and transmission speeds are configurable

- Electric signaling levels and methods (such as differential signaling etc.) handled by an external driver.

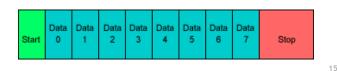

#### Protocol

- MICH

- Each character is sent as

- a logic low start bit

a configurable number of data bits (usually 7 or 8,

- sometimes 5)

- an optional parity bit

- one or more logic high **stop** bits.

- with a particular bit timing ("baud" or "baudrate")

- Examples

- "9600-N-8-1" <baudrate><parity><databits><stopbits>

- "9600-8-N-1" <baudrate><databits><parity><stopbits>

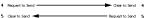

#### Signals (only most common)

- The RXD signal of a UART is the signal receiving the data. This will be an input and is usually connected to the TXD line of the downstream device.

- The TXD signal of a UART is the signal transmitting the data. This will be an output and is usually connected to the RXD line of the downstream device.

- The RTS# (Ready to Send) signal of a UART is used to indicate to the downstream device that the device is ready to receive data. This will be an output and is usually connected to the CTS# line of the downstream device.

- The CTS# (Clear to Send) signal of a UART is used by the downstream device to identify that it is OK to transmit data to the upsteam device. This will be an input and is usually connected to the RTS# line of the upstream device.

## Variations

- UART is actually a generic term that includes a large number of different devices/standards.

- RS-232 is a standard.

- Specifies characteristics and timing of signals, the meaning of signals, and the physical size and pin out of connectors.

#### DB9 stuff

- \_ \_\_\_

- DTE vs. DCEPinout of a DCE?

- Common ground?

- Noise effects?

#### Z Transmitted Data — Preceived Data Z 3 Received Data — Transmitted Data 3

DCE

Pin Number

Signal

Description

1

DCD

Data carrier detect

2

RxD

Receive Data

3

TxD

Transmit Data

4

DTR

Data terminal ready

5

GND

Signal ground

6

DSR

Data tready

7

RTS

Ready to send

8

CTS

Clear to send

9

RI

Ring Indicator

Wiring a DTE (terminal) device to a DCE (modem) device for communication is easy. The pins are a one-to-one connection, meaning all wires go from pin x to pin x. A straight through cable is commonly used for this application. In contrast, wiring two DTE devices together requires crossing the transmit and receive wires. This cable is known as a null modem or crossover cable. Also easy to wire.

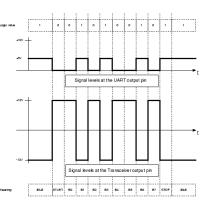

#### RS-232 transmission example

RS232 Transmission of the letter 'J'

#### Outline

- Context and review

- Serial buses

- <del>UART</del>

- SPI

- I2C

- ADCs and DACs

- Fundamentals

- Operation

19

## Introduction

- What is it?

- Basic Serial Peripheral Interface (SPI)

- Capabilities

- Protocol

- Pro / Cons and Competitor

- Uses

- Conclusion

20

# What is SPI?

- Serial bus protocol.

- Fast, easy to use, simple.

- Widely supported.

|                        | 08   |  | <b>.</b>   | unununu.     | -1 . <sup>1</sup> . |

|------------------------|------|--|------------|--------------|---------------------|

| IBM                    |      |  |            |              |                     |

| Digital Set-Top Box    | 111  |  | → <b>1</b> |              | <b>F1 11</b>        |

| Integrated Controller  |      |  |            |              | 11 -1               |

| PowerPC                | 1115 |  | -          | * Current t  | ine the             |

| 75H6051 (GEM           | 5051 |  | 404        | we current t | THE TAT             |

| 1F11DCORPB KOREA       |      |  |            |              |                     |

| IBM39 STB02100 PBC 22C |      |  |            |              |                     |

|                        |      |  |            |              |                     |

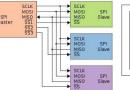

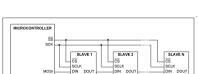

## SPI basics

- A communication protocol using 4 wires

Also known as a 4 wire bus

- Used to communicate across small distances

- Multiple slaves, single master

- Synchronized

# Capabilities of SPI

- Always Full Duplex

- Communicating in two directions at the same time

- Transmission need not be meaningful

- Multiple Mb/s transmission speed

- Transfers data in 4 to 16 bit characters

- Multiple slaves

- Daisy-chaining possible

# Protocol

| Master S | MOSI | -     |

|----------|------|-------|

|          |      | Slave |

|          | SCLK | -     |

- Wires:

- Master Out Slave In (MOSI)

- Master In Slave Out (MISO)

- System Clock (SCLK)

- Slave Select 1...N

- Master Set Slave Select low

- Master Generates Clock

- Shift registers shift in and out data

- MOSI Carries data out of Master to Slave

- MISO Carries data from Slave to Master

Both signals used for every transmission

- SS\_BAR Unique line to select a slave

- SCLK Master produced clock to synchronize data transfer

MICHIGAN

# Shifting protocol

# Master Slave

Master shifts out data to Slave, and shift in data from Slave

# Diagram

Master and multiple independent

Slaves http://upload.wikimedia.org/wikipedia/commons/thumb/fifc/SPI\_three\_sl ves.svg/350px.SPI\_three\_slaves.svg.png

Some wires have been rename

Master and multiple daisychained slaves

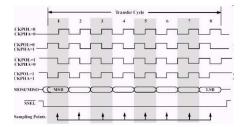

# Clock phase (advanced)

- Two phases and two polarities of clock.

- Four modes.

- Master and selected slave must be in same mode.

- Master must change polarity and phase to communicate with slaves of different numbers.

- Data transmission and latching happen on alternating clock edges.

- Why? Increases implementation flexibility for bus users.

# Timing Diagram

Timing Diagram - Showing Clock polarities and phases

## Pros and cons

#### Pros:

- Fast and easy

- Fast for point-to-point connections

Easily allows streaming/Constant data inflow

- No addressing/Simple to implement

- Full duplex

- Widely supported

#### Cons:

- SS signal makes multiple slaves complicated

- No ack capability

No inherent arbitration

- No flow control

- Four wires

## Uses

- Some serial encoders/decoders, converters, serial LCDs, sensors, etc.

- Pre-SPI serial devices

## Outline

- SPI 4 wire serial bus protocol

- MOSI MISO SS SCLK wires

- Full duplex

Summary

- Multiple slaves, one master

- Best for point-to-point streaming data

- Easily supported

- Serial buses

- UART

- SPI

- I2C

- ADCs and DACs

- Fundamentals

- Operation

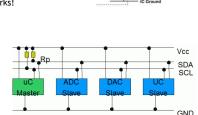

#### I<sup>2</sup>C summary

- Inter integrated circuit bus.

- Two-wire protocol.

- From Philips in early 1980s.

#### I<sup>2</sup>C applications

- Initially in TV sets.

- Common for peripherals from many companies.

- Real-time clocks and temperature sensors on general-purpose computer motherboards.

#### I<sup>2</sup>C technical description

MICHIGAN

#### I<sup>2</sup>C wiring

- SDA: data.

- SCL: clock.

- Open collector.

- Simple interfacing among voltage domains.

- Two-wire serial protocol.

- Addressing.

- Up to 3.4 Mb/s.

- Multi-master, multi-slave.

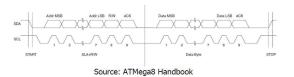

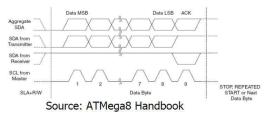

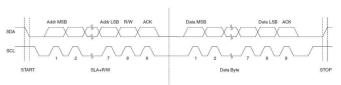

## I<sup>2</sup>C transaction

- Master initiates.

- Start.

- Address.

- Data.

- Ack.

- Stop.

#### I<sup>2</sup>C roles

I<sup>2</sup>C clocking

• Unconventional.

• Quiescent state is high.

• Master pulses low during transmission.

• One advantage of open collector design.

• Slave holds clock low to extend transmission cycle.

- Transmitter/receiver not same as master/slave.

- Master initiates transactions.

- Transmitter sends data on SDA.

- Receiver acks.

- Read: slave is transmitter.

- Write: master is transmitter.

39

41

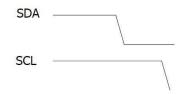

#### I<sup>2</sup>C starting

- MICHIGAN

- Master drives SDA low while SCL remains high.

- During other parts of transactions, SDA changes when SCL is low.

#### I<sup>2</sup>C address

#### I<sup>2</sup>C data

- Sampled on rising SCL.

- 8-bit.

- Write: master transmits, slave acks. •

- Read: slave transmits, master acks.

- Continues until master signals to stop. •

- Sampled on rising SCL.

- 7-bit address. • 8<sup>th</sup> bit

- Low: write.

- High: read.

- Philips/NXP can assign standard addresses for a fee.

• Master allows SDA to go high while SCL high.

• Stops or aborts transactions.

SDA

SCL

I<sup>2</sup>C stopping

43

I<sup>2</sup>C timing diagram

Source: ATMega8 Handbook

45

#### Outline

- Context and review

- Serial buses

- UART

- SPI

- <del>12C</del>

- ADCs and DACs

- Fundamentals

- Operation

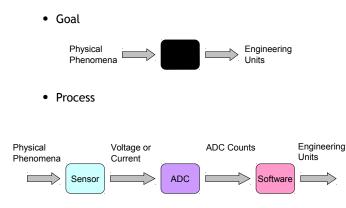

## Many signals effectively analog

46

- At the macroscopic level, many signals have so many possible values they are effectively continuous/analog. - Sound, light, temperature, pressure, voltage, etc.

- Path to digital system

- Source  $\rightarrow$  continuous voltage  $\rightarrow$  discrete value. Transducers: converts one type of energy to another - Electro-mechanical, Photonic, Electrical, ...

- Examples

- Microphone/speaker

- Thermocouples

- Accelerometers

#### Transducers convert one form of energy into another

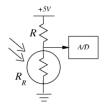

#### Convert light to voltage with a CdS photocell

- $V_{signal} = (+5V) R_{R}/(R + R_{R})$

- Choose R=R<sub>R</sub> at median of range.

- Cadmium Sulfide (CdS).

- Cheap, low current.  $T_{RC} = (R+R_R)^*C_L$  Typically R-50-200kW.

- C~20pF.

So, T<sub>RC</sub>~20-80uS.

- f<sub>RC</sub> ~ 10-50kHz.

Source: Forrest Brewer

Many other common sensors (some digital)

- Force

- Strain gauges foil, conductive ink Conductive rubber Rheostatic fluids \_

- \_

- \_

- Piezorestive (needs bridge)

Piezoelectric films

- Capacitive force

- Sound

- Microphones: current or charge Sonar: usually piezoelectric

- Position

- Switches \_

- Shaft encoders Gyros

- Atmospheric pressure

49

## Many other common sensors (some digital)

- Acceleration

- MEMS \_

- Pendulum

- Monitoring

- Battery energy Motor velocity Temperature \_ \_

- Field

- Antenna

- \_ Magnetic

- Hall effect Flux gate

- Location

- Permittivity

- Dielectric

- Conductivity •

٠

•

Many, many more

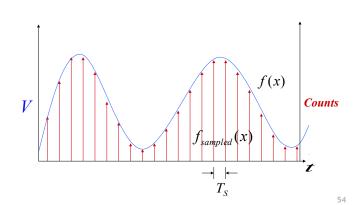

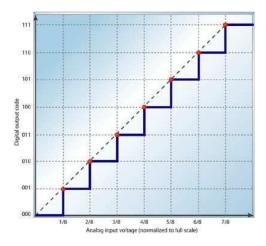

# Digital representation of analog signal

Discretize in time and value. Time series of discrete values

53

#### Choosing the value range

Range Too Small

$V_{r}$

V

•

$V_{r+}$

$V_{r}$

٠

What do the sample values represent?

Some fraction within the range of values

$V_{r+}$

$V_{r}$

Ideal Range

Range Too Big

#### Choosing the value resolution

- Resolution

- Number of discrete values that represent a range of analog values.

- MSP430: 12-bit ADC

- 4096 values

- Range / 4096 = Step

- Quantization Error

How far off discrete value is from actual

- $\frac{1}{2}$  LSB  $\rightarrow$  Range / 8192

Larger range  $\rightarrow$  lower resolution

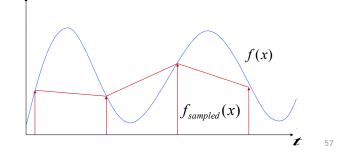

Choosing the temporal resolution

• Too low: we can't reconstruct the signal.

Too high: waste computation, energy, resources.

MICHIGAN

55

#### Shannon-Nyquist sampling theorem

• If a continuous-time signal f(x) contains no frequencies higher than  $f_{\max}$ , it can be completely determined by discrete samples taken at a rate:

$$f_{\text{samples}} > 2 f_{\text{max}}$$

- Example: Samples Simples Max

Humans can process audio signals 20 Hz 20 KHz

Audio CDs: sampled at 44.1 Khz

- Caveat: additional samples can have value if signal contains high-frequency noise.

- Allows low-pass filter to improve accuracy at cost of decreased effective samping rate.

58

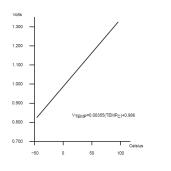

#### Converting between voltages, ADC counts, and engineering units

• Converting: ADC counts  $\rightarrow$  Voltage

• Converting: Voltage → Engineering Units

$V_{\text{TEMP}} = 0.00355(\text{TEMP}_{\text{C}}) + 0.986$ TEMP<sub>C</sub> =  $\frac{V_{\text{TEMP}} - 0.986}{0.00355}$

## A note about sampling and arithmetic

• Common error converting values

$$V_{\text{TEMP}} = N_{\text{ADC}} \times \frac{V_{\prime+} - V_{\prime-}}{4095} \text{ TEMP}_{\text{C}} = \frac{V_{\text{TEMP}} - 0.986}{0.00355}$$

float vtemp = adccount/4095 \* 1.5;

float tempc = (vtemp-0.986)/0.00355; Learn associativity and type conversion rules of ANSI C.

- Fixed point operations

- Overflow and underflow dangers complicate design.

- This is deep. Talk to me if you want to try it.

- Floating point operations

- Often software emulated.Often slow, power-hungry on embedded processors.

# Use anti-aliasing filters on ADC inputs to ensure that Shannon-Nyquist is satisfied

Removes high-frequency components

- (a.k.a. anti-aliasing filter)

Different frequencies are indistinguishable when they

Aliasing

Cond

are sampled.

s filter

#### Do I really need to condition my input signal?

- Often.

- Many ADCs have analog filter built in.

- Those filters typically have a cut-off frequency just above ½ their *maximum* sampling rate.

- Which is great if you are using the maximum sampling rate, less useful if you are sampling at a slower rate.

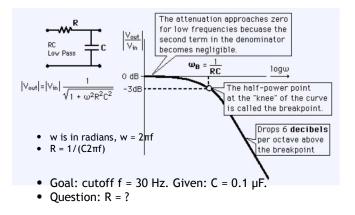

#### Designing the anti-aliasing filter

61

## Oversampling

- Can intentionally introduce or leave high-frequency noise and oversample.

- Reduces quantization error.

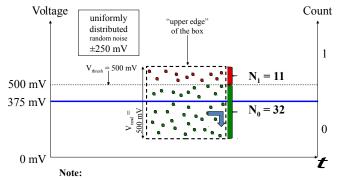

#### Oversampling a 1-bit ADC w/ noise & dithering (cont)

63

$N_1$  is the # of ADC counts that = 1 over the sampling window  $N_0$  is the # of ADC counts that = 0 over the sampling window

#### Lots of other issues

64

- Might need anti-imaging filter.

- Especially during analog signal reconstruction.

- Remove high-f components from stair stepping.

- Cost and power play a role.

- Might be able to avoid ADCs/DACs.

E.g., PWM.

62

#### Outline

- Context and review

- Serial buses

- UART

- <del>SPI</del>

- <del>12C</del>

- ADCs and DACs

- Fundamentals

- Operation

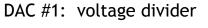

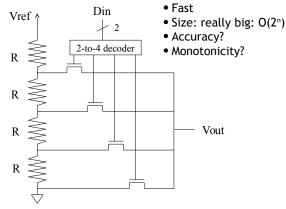

DAC #2: R/2R ladder Vref R R R 2R WW w MW WW-2R 2R 2R 2R Iout D3 (MSB) D2 D1 D0 (LSB)

- Size: small O(n)

- Accuracy?

- Monotonicity? (Consider 0111 -> 1000)

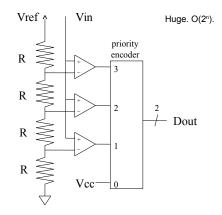

## ADC #1: flash

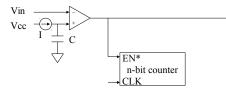

## ADC #2: single-slope integration

- Start: Reset counter, discharge C.

- Charge C at fixed current I until Vc > Vin . How should C, I, n, and CLK be related?

- Final counter value is Dout.

- Slow: conversion may take several milliseconds. • O(2n)

- Good differential linearity (dl/dO)

- Absolute linearity depends on precision of C, I, and clock.

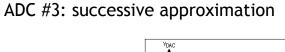

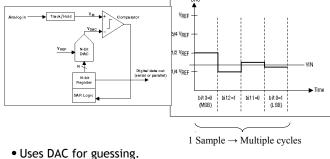

- Faster: O(n)

- Goes from MSB to LSB.

- Not good for high-speed ADCs.

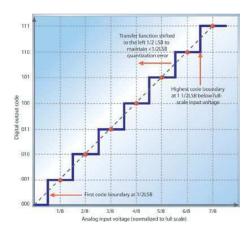

## Errors and ADCs

- Figures and some text from:

- Understanding analog to digital converter specifications. By Len Staller

- http://www.embedded.com/showArticle.jhtml?ar ticleID=60403334

- Key concept here is that the specification provides *worst case* values.

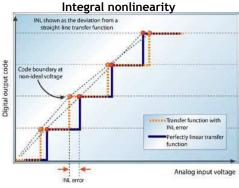

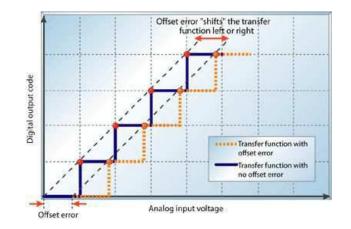

The integral nonlinearity (INL) is the deviation of an ADC's transfer function from a straight line. This line is often a best-fit line among the points in the plot but can also be a line that connects the highest and lowest data points, or endpoints. INL is determined by measuring the voltage at which all code transitions occur and comparing them to the ideal. The difference between the ideal voltage levels at which code transitions occur and the actual voltage is the INL error, expressed in LSBs. INL error at any given point in an ADC's transfer function is the accumulation of all DNL errors of all previous (or lower) ADC codes, hence it's called *integral* nonlinearity.

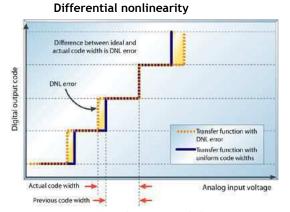

DNL is the worst cases variation of actual step size vs. ideal step size.

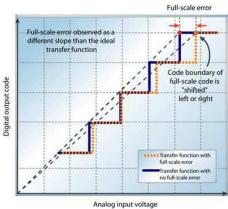

Full-scale error is also sometimes called "gain error"

Full-scale error is the difference between the ideal code transition to the highest output code and the actual transition to the output code when the offset error is zero.

#### Errors

- Errors in a specification are bad.

- So if you have an INL of ±0.25 LSB, you "know" that the device will never have more than 0.25 LSB error from its ideal value.

- That of course assumes you are operating within the specification.

- Temperature, input voltage, input current available, etc.

- Integral nonlinearity and differential nonlinearity are important.

- Should know what full-scale error is.

- Can compensate in software.

- Where is best place to compensate?