|       |     | EECS 373 Exam 1               |

|-------|-----|-------------------------------|

|       | 1,  | Winter '04, Prof. Mark Brehob |

| Name: | Key | uname: <u>ke</u> /            |

|       | 1   |                               |

Sign the honor code:

I have neither given nor received aid on this exam nor observed anyone else doing so.

Scores:

| Section         | Points |

|-----------------|--------|

| Short answer    | /60    |

| Design question | /40    |

| Total           | /100   |

## **NOTES:**

- Open notes. If you don't have your white book with you please contact the proctor you will need it!

- Don't spend too much time on any one problem.

- You have 80 minutes for the exam.

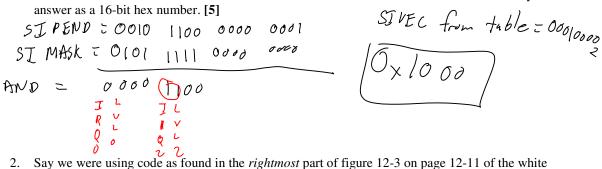

1. If SIPEND=0x2C010000 and SIMASK=0x5F000000 what is the value in SIVEC? Provide your answer as a 16-bit hex number. [5]

2. Say we were using code as found in the *rightmost* part of figure 12-3 on page 12-11 of the white book. If BASE=0x00340000, where would the code for the LVL3 interrupt be located? [5]

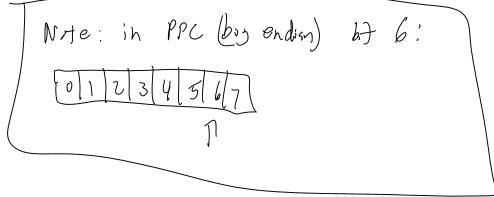

3. Write PowerPC assembly that modifies the byte stored at memory location 0x00001000 so that bit 6 is negated (changed from a zero to a one or visa versa). No other bit in memory should be changed by your code. [10]

5. Write the prologue for a PowerPC assembly function "bob". You are to follow the EABI and use as little memory on the stack as possible. The function "bob" uses registers 4, 5, 30, and 31 but does not modify the condition register. Other than saving the needed GPRs, 8 bytes need to be reserved for local variables. **[10]**

6. For each of the load instructions below, indicate whether or not the instruction causes an unaligned access. Also, list the bus contents for each transaction and the final value held in the register that you've loaded. If there are bits that have undefined values for a given transaction, mark their values as 'X'. Use hexadecimal notation. Assume the register and memory values listed below. [15]

| Register        | Value      |

|-----------------|------------|

| r3              | 0x03100002 |

| Memory Location | Value      |

| 0x03100000      | 0x12345670 |

| 0x03100004      | 0x14151617 |

| 0x03100008      | 0xDEADBEEF |

| 0x0310000C      | 0x0BADBEAD |

| 0x03100010      | 0x00FADDAD |

| 0x03100014      | 0x44556677 |

| 0x03100018      | 0x37337337 |

| 0x0310001C      | 0x27037000 |

Bus contents Could be of more than 6 he form.....

| Aligned?     | Bus contents             | Value in r8 once<br>assembly command is<br>done |

|--------------|--------------------------|-------------------------------------------------|

| $\mathbb{N}$ | XXAD XX XX<br>XX XX BEYX | OX FFFF ADBE                                    |

|              | XX 15 XXXX<br>XXXX 1617  | OX 151617, DE                                   |

|              | Aligned?                 | N XXAD XX XX                                    |

7. The memory locations 0x1000 through 0x1006 have been initialized as shown in the table below and the registers have been initialized so that r1=1, r2=0x1000, and r3=0x01234567. The following code segment is then run.

stw r3, 0(r2) stop r3, 2(r2) stwx r3, r2, r1

After the code segment completes, what are the values in these memory locations? You may ignore any memory location that is written to but not shown in the table. **[10]**

|               | Address     | 0x1000 | 0x1001 | 0x1002      | 0x1003 | 0x1004 | 0x1005 | 0x1006       |

|---------------|-------------|--------|--------|-------------|--------|--------|--------|--------------|

|               | Previous    | A0     | B0     | C0          | D0     | E0     | F0     | A0           |

|               | value (hex) |        |        |             |        |        |        |              |

|               | New value   | οl     | 23     | 67          | 01     | 23     |        |              |

|               | (hex)       | 0 (    |        | $\varphi$ / |        |        | 45     | 47           |

| ( -           | 计           | 61     | 23     | 45          | 67     |        |        |              |

| $\mathcal{I}$ | Å           |        |        | 67          |        |        |        | $( \frown )$ |

| 37            | - &         |        |        | -           | 01     | 23     | 43     | ( )          |

| >"            | ų           |        |        |             |        | 00     |        |              |

## **Design Question**

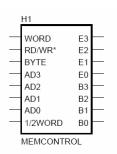

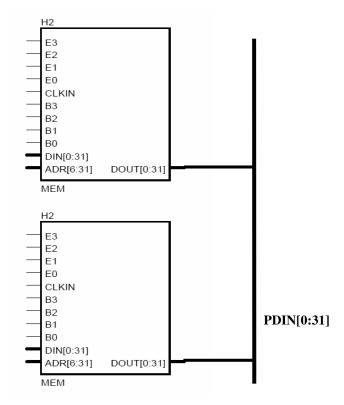

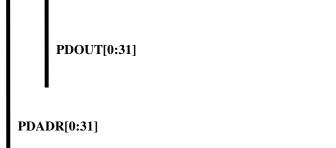

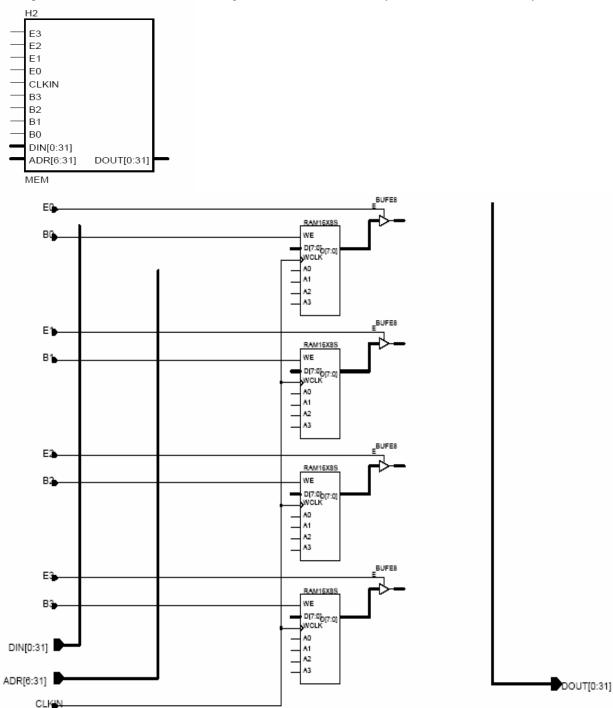

Complete the design of the following MPC823 memory. The memory accommodates byte,  $\frac{1}{2}$  word and word read and write accesses. The memory has a 32-word capacity and is composed of 16 X 8-bit RAM modules. Assume that the memory is in the address space 0x0000 007f to 0x0000 0000.

1) Complete the connections for the following macro. Be sure to label all your bus connections clearly. [10]

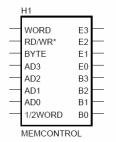

2). You are given two macros that decode A31-A30 and TSIZ[0:1] according to the tables found below (First column is inputs, rest are outputs)

## ADS\_MACRO

| A30, A31 | AD0 | AD1 | AD2 | AD3 |

|----------|-----|-----|-----|-----|

| 0,0      | 1   | 0   | 0   | 0   |

| 0,1      | 0   | 1   | 0   | 0   |

| 1,0      | 0   | 0   | 1   | 0   |

| 1,1      | 0   | 0   | 0   | 1   |

TSIZE\_MACRO

| TSIZ[0:1] | byte | 1/2word | word |

|-----------|------|---------|------|

| 0,0       | 0    | 0       | 1    |

| 0,1       | 1    | 0       | 0    |

| 1,0       | 0    | 1       | 0    |

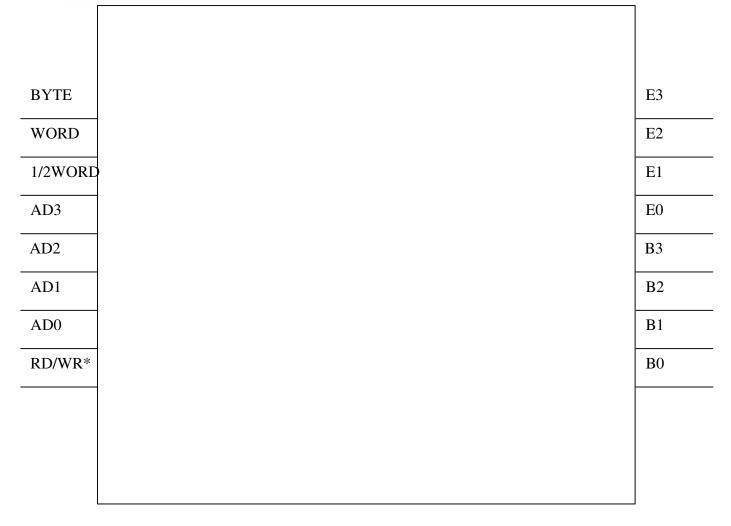

Design a macro to provide the control logic for byte,  $\frac{1}{2}$  word and word read and write access for the proceeding module. The macro should have the following hierarchical connections. Use the space provided below. [20]

3. Now complete the design by connecting the macros. You may need to add logic. You do **NOT** need to worry about: **[10]**

- The generation of TA

- The decoding of the address

- The inputs into the H1 macro. (Just leave them unconnected)

- The CLKIN wire in the H2 macro (Just leave it unconnected)