## EECS 373 – lecture 4

Buses, serial communication and digital design

### Announcements

- I saw very few people in for questions on prelab 3.

Feel free to use my office hours for help as needed.

- Don't put off the prelabs. You certainly don't have time to do them in the lab

- Lab 3

- Lab 3 is a 2 week lab. You will likely need to use open hours a LOT to get this done.

- Ron is holding extra lab hours this week from 4:30-7:30

- We will be arranging to insure you can get into the lab during normal hours. See the website...

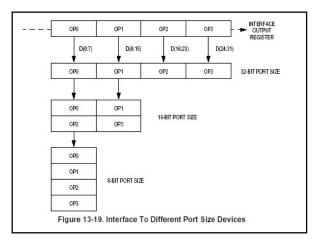

| TRANSFER<br>SIZE | TSIZE<br>[0:1] |   | INTERNAL<br>ADDRESS |     |       | 32-BIT | PORT SIZE   | 16-BIT PORT SIZE |              | 8-BIT<br>PORT<br>SIZE |     |

|------------------|----------------|---|---------------------|-----|-------|--------|-------------|------------------|--------------|-----------------------|-----|

|                  |                |   | A30                 | A31 | D0-D7 | D8-D15 | -D15 D16D23 | D24-D31          | D0-D7 D8-D15 | D0-D7                 |     |

| Byte             | 0              | 1 | 0                   | 0   | OP0   | 18-    |             | _                | OP0          | <u>62</u>             | OP0 |

|                  | 0              | 1 | 0                   | 1   | 120   | OP1    | _22         | _                |              | OP1                   | OP1 |

| 3                | 0              | 1 | 1                   | 0   | -     |        | OP2         | -                | OP2          | -                     | OP2 |

|                  | 0              | 1 | 1                   | 1   | -     |        | -           | OP3              |              | OP3                   | OP3 |

| Half-Word        | 1              | 0 | 0                   | 0   | OP0   | OP1    | -31         | _                | OP0          | OP1                   | OP0 |

|                  | 1              | 0 | 1                   | 0   |       | 18     | OP2         | OP3              | OP2          | OP3                   | OP2 |

| Word             | 0              | 0 | 0                   | 0   | OP0   | OP1    | OP2         | OP3              | OP0          | OP1                   | OP0 |

| TRANSFER<br>SIZE | TSIZE<br>[0:1] |   |     | RNAL<br>RESS | EXTERNAL DATA BUS PATTERN |       |           |         |  |

|------------------|----------------|---|-----|--------------|---------------------------|-------|-----------|---------|--|

|                  |                |   | A30 | A31          | D0D7                      | D8D15 | D16-D23   | D24-D31 |  |

| Byte             | 0              | 1 | 0   | 0 0          | OP0                       | _     |           | -       |  |

|                  | 0              | 1 | 0   | 1            | OP1                       | OP1   |           | _       |  |

|                  | 0              | 1 | 1   | 0            | OP2                       | -     | OP2       | -       |  |

|                  | 0              | 1 | 1   | 1            | OP3                       | OP3   | 8 <u></u> | OP3     |  |

| Half-Word        | 1              | 0 | 0   | 0            | OP0                       | OP1   | 822       |         |  |

|                  | 1              | 0 | 1   | 0            | OP2                       | OP3   | OP2       | OP3     |  |

| Word             | 0              | 0 | 0   | 0            | OP0                       | OP1   | OP2       | OP3     |  |

Last time we discussed:

- Serial communication

- Problems with serial communication

- Want shared clock

- Use different techniques instead.

One was "change if real data stays same"

- Used XOR to decode this one

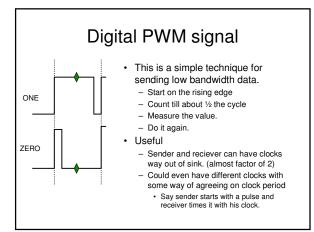

- PWM signal

- Use "duty cycle" to indicate state

- Low bandwidth (why?)

- Did a bit on counters

# Correction

#### USB stuff

- 0 is encoded as a transition, 1 as no transition

Bit stuffing

- If no change for 6 cycles (6 1s), insert a change.

- Assume signal period is 20 local clocks.

- Assume either 30/70 or 70/30 duty cycle +/- 10%

- · Assume signal might have some noise

- · Mr. State machine.

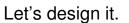

# Now let's design an "analog" version

- Say we want to measure duty cycle...

- Design that.

- Pure FSM may not be the best way to go...

- Time from rising edge to rising edge is about 100 to 1000 cycles

- Min/Max is 10/90 90/10

- Some noise possible.

And one more design problem?