# **Bus Interface Design Problem (35 points total)**

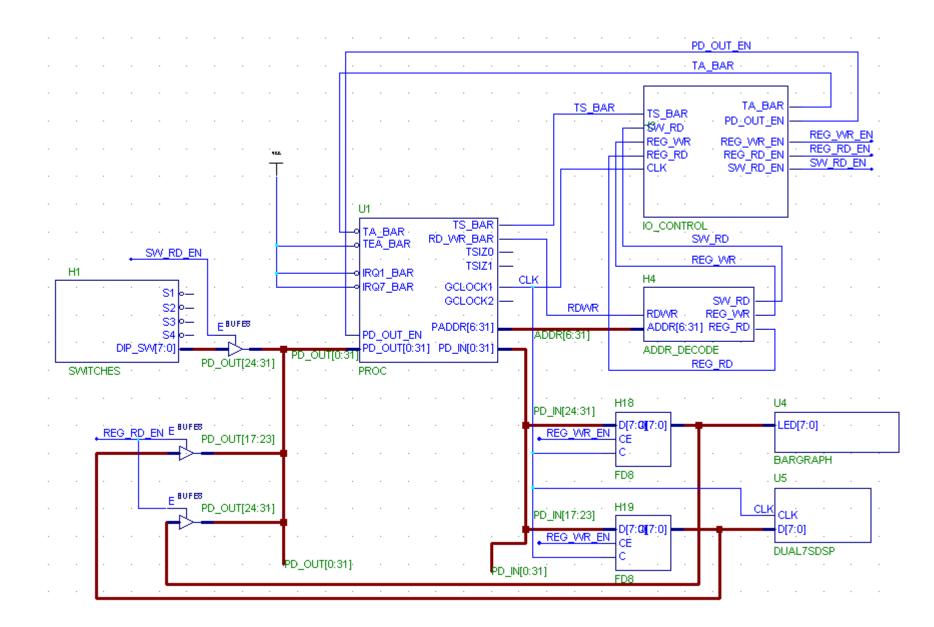

For this problem, you need to complete the bus interface to the dipswitches, Bar Leds and 7-Segment Leds shown in the High Level schematic. The problem is similar to that of lab 3, except we will use a low power FPGA family that performs somewhat slower then the FPGA used in the lab. Be sure to read the timing specifications carefully.

#### **Power PC Timing Specifications**

TA\* and Data Setup: <sup>1</sup>/<sub>4</sub> clock cycle TA\* and Data Hold: <sup>1</sup>/<sub>4</sub> clock cycle

## **FPGA Timing Specifications**

TRI-State Buffer Propagation Delay: negligible LED Register Data Setup: 2 clock cycles LED Register Data Hold: <sup>1</sup>/<sub>4</sub> clock cycle

#### **Memory Map**

Switch Location (Word Addressable): 0x3100000 Bar Led Location (Word Addressable): 0x3200000 7-Segment Display (Word Addressable): 0x3200000

#### **Devices Allowed in the Design**

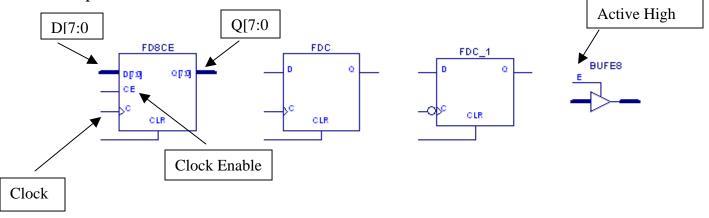

You will be asked to complete various parts of the bus interface design. The following components are allowable.

#### Inverters

AND, NAND, OR, NOR of any size. You may use inverting bubbles on inputs.

## **Timing Study**

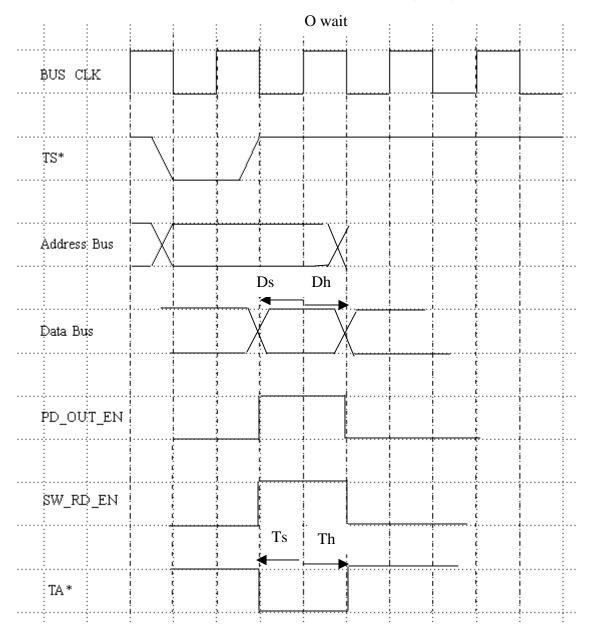

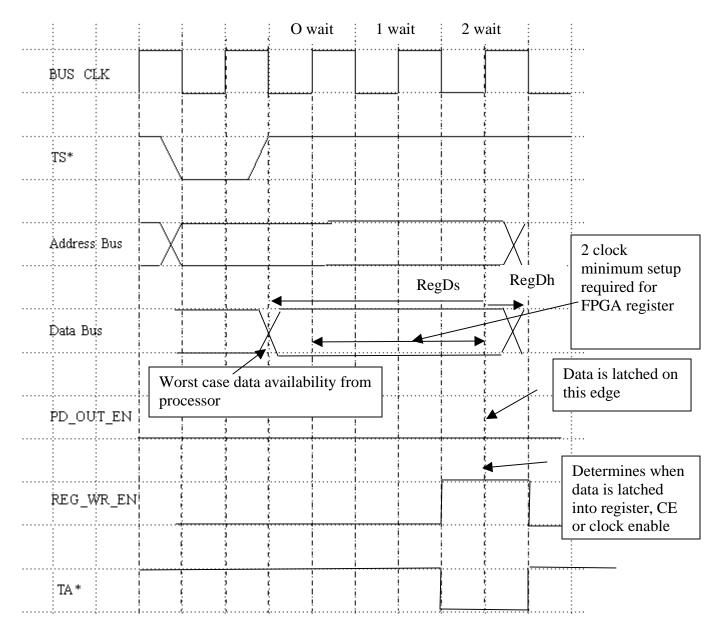

In lab, we discussed that the design process should start with a timing study. We started by addressing the minimum requirements. We then considered a synchronous solution that would meet the minimums with a safety margin.

## Assignment 1 (10 points)

Complete the following read cycle timing diagram for a synchronous solution. You should use **no** more WAIT states then necessary.

Show the TA\*, and processor data setup and hold times **your design will provide**. Illustrate the times as intervals on the timing diagrams.

#### Assignment 2 (10 points)

Complete the following write cycle timing diagram for a synchronous solution. You should use **no** more WAIT states then necessary.

Show the LED registers data setup and hold times **your design will provide**. Illustrate the times as intervals on the timing diagrams.

Complete LED registers connections on the High Level schematic. Be sure to show all the connections clearly.

#### Assignment 3 (5 points)

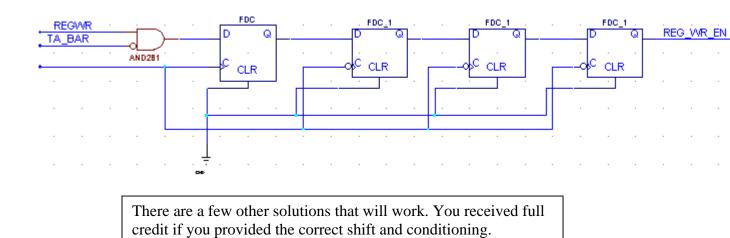

Provide the logic in schematic form in the space below for the **REG\_WR\_EN** signal in the IO control macro. **You DO NOT have to provide logic for the other control signals**. You **DO NOT** have to provide the address decode. Notice it is provided to the macro. Clearly label all signals.

4

#### Assignment 4 (5 points)

In this design, we want to provide a means to read LED registers as well as writing them.

Modify the High Level schematic for the paths and hardware required to implement reading the LED registers. Label all connections clearly. Assume that the BAR led is read on bits 24-31 and the 7-Segment is read on bits 17-23.

#### Assignment 5(5 points)

If the Led registers were upgraded to be byte write addressable:

What input and output control signals do you have to add to the address decoder?

## Input: TSIZ0, TSIZ1 Output: REG\_WR\_byte2, REG\_WR\_byte3

This should really be 0x320000x. Where x = 0b00xx and x is don't care. A31 and A30 need to be decoded for byte addressing. I omitted this in the grading.

Assuming the address 0x3200000 is decoded as AD32 (active high), provide the **Boolean** expressions for the LED registers byte write control signals. Use \* for AND, | for OR and ~ for inversion.

You **do not** have to provide any modifications to the IO\_Control Macro.

#### **REG\_WR\_byte2** =

(A30 \* ~A31 \* TSIZ1 \* ~TSIZ0 \* AD32 \* ~RDWR) | (~A30 \* ~A31 \* ~TSIZ1 \* ~TSIZ0 \* AD32 \* ~RDWR) Provides byte addressing

Maintains Word Addressing

**REG\_WR\_byte3 =**

(A30 \* A31 \* TSIZ1 \* ~TSIZ0 \* AD32 \* ~RDWR) | (~A30 \* ~A31 \* ~TSIZ1 \* ~TSIZ0 \* AD32 \* ~RDWR) **\***

> There are no registers for bytes 0 and 1 so they are not decoded. Half word addressing of the byte 2 and byte 3 register was not asked for, so it is not provided.

> > 5

Assignment 5 (additional space)

## HIGH LEVEL SCHEMATIC