## Midterm — November 3, 2006

Write and sign the honor pledge:

- 1. (2 pts) Print your name on *each and every* sheet.

- 2. (8 pts) Write down the equations for the forward and inverse Discrete Fourier Transform. Indicate which is which. Use the "standard" definitions.

- 3. (2 pts) FPGA technology (component density and speed) has been benefiting from Moore's law. It is now at a point where (the instructor claims) that it will be a major player in DSP applications. This evidenced by the recent introduction of DSP oriented FPGA devices by Xilnx, Altera, Lattice and others. What do the letters FPGA stand for?

- 4. (2 pts) Typically a microcomputer or FPGA is be felt to have been designed for use in doing digital signal processing if it possesses a

instruction.

- 5. (8 pts) A time waveform x(t) is sample at a rate of  $f_s$  for T seconds resulting in a set of N samples.

- (a) How are  $f_s$ , T, and N related (i.e., equation):

- (b) The DFT is taken of the *N* sample values. What are the frequencies, associated with the following values of *k*?

- i. k = 0 Hz.

ii. k = 1 Hz.

iii. k = 2 Hz.

- 6. (2 pts) The TI C5510 divides data memory into pages. The number of 16-bit data words per page is K.

- 7. (2 pts) The size of the C5510 on-chip memory is Kwords.

- 8. (2 pts) The C5510 has on-chip timers.

- 9. (2 pts) The C5510 has McBSP channels.

- 10. (6 pts) The C5510 supports three addresses spaces. These are

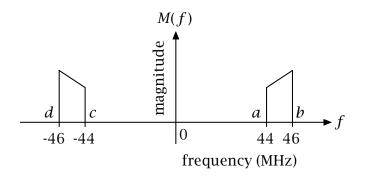

12. (10 pts) A useful aspect of sampling is to alias a bandlimited signal to lower frequencies. This is accomplished by using sample rates lower than or equal to Nyquist.

Sketch and label the spectrum after sampling using the following sampling rates:

| (a) $f_s = 45$ MHz.                                                                                                                             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| a = MHz.                                                                                                                                        |  |  |  |

| b = MHz.                                                                                                                                        |  |  |  |

| $c = \_$ MHz.                                                                                                                                   |  |  |  |

| d = MHz.                                                                                                                                        |  |  |  |

| The Nyquist range is from to MHz.                                                                                                               |  |  |  |

| (b) $f_s = 16$ MHz.                                                                                                                             |  |  |  |

| $a = \_\MHz.$                                                                                                                                   |  |  |  |

| b = MHz.                                                                                                                                        |  |  |  |

| $c = \_$ MHz.                                                                                                                                   |  |  |  |

| d = MHz                                                                                                                                         |  |  |  |

| The Nyquist range is from to MHz.                                                                                                               |  |  |  |

| 13. (4 pts) The C5510 hasbit accumulators.                                                                                                      |  |  |  |

| 14. (2 pts) The C5510 has status registers.                                                                                                     |  |  |  |

| 15. (4 pts) The AIC23 CODEC chip used on the C5510 DSK connects to the C5510 using two McBSP channels, one for setup and one for data transfer. |  |  |  |

| (a) Which McBSP channel is used for setup using the SPI protocol?                                                                               |  |  |  |

| (b) Which McBSP channel is used for moving sample values between the                                                                            |  |  |  |

| AIC23 and the C5510?                                                                                                                            |  |  |  |

| 16. True (T) or false (F) (2 pts each):                                                                                                         |  |  |  |

| The AIC23 only supports two sample rates, these are 8 kHz and 48 kHz.                                                                           |  |  |  |

| One should operate a DSP processor at as slow a clock rate as possible as determined by the application being implemented.                      |  |  |  |

| The TI C compiler generates code for the C5510's floating point unit.                                                                           |  |  |  |

|                                                                                                                                                 |  |  |  |

The C5510 has 32 memory mapped registers.

- The C5510's PLL is used to convert the 20 MHz USB clock to the CPU's 200 clock.

- An advantage of the two's complement number representation is that the same add/sub hardware is used as is with unsigned numbers.

- Two's complement multiplication has the advantage that it can be accomplished using the a multiplier designed to implement unsigned multiplication.

- <u>32-bit fixed point values have the potential to give results more accurate than those obtained using 32-bit floating point.</u>

- \_\_\_\_\_ The C5510 **subc** instruction can be used to implement unsigned division.

- \_\_\_\_\_ FPGAs allow performance increases over DSP devices because they readily support parallel operation.

- It has been stated in the lecture notes that "there must be significant commercial potential" in the class projects.

- The class projects need not make any use of digital signal processing.

- In order to construct a complicated system is is desirable to beak the problem down into smaller manageable pieces. Each subproblem can then be further broken down until the entire system is decomposed into fundamental building blocks.

- All FIR filters have a linear phase response.

- All IIR filters have a linear phase response.

- 17. (8 pts) An EECS 452 project has decided to implement an OFDM modem. The transmitter and receiver use separate DSKs. The oscillators on the two boards are accurate to one part in  $10^6$ . This amount of frequency offset will severely affect the received quadrature-amplitude modulation signal constellation. It is decided that a preamble will be added to each data packet. The preamble will be used to measure phase change over the preamble duration. This will give an extremely accurate measurement of the transmitter/receiver carrier frequency offset,  $\Delta f$ .

The receiver uses sample frequency  $f_s$ .

The measured  $\Delta f$  value will be used to implement a sine/cosine DDS used to generate sample values of  $e^{-j2\pi n\Delta f/f_s}$  where *n* goes from 0, 1, 2, .... These values will multiply the sampled reception values in the data portion of the packet thus correcting for much, if not all, of the frequency offset.

The data portion of the packet contains  $8 \times 256 \times 4$  samples. It is desired to limit the amount of phase change over these samples to  $\Delta\theta$  degrees. Let *N* be the number of bits in the DDS phase accumulator. What is the smallest value of *N* that will allow the phase to be corrected to this level?

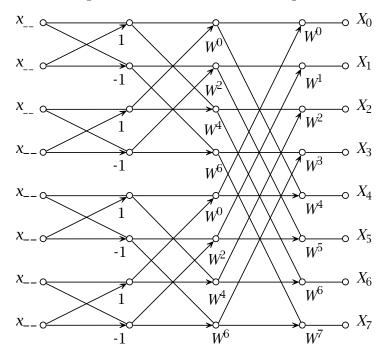

18. (4 pts) For the following decimation-in-time FFT data flow diagram what are the required index values on the input *x* values?

19. (4 pts) Write the equation describing the Fourier Transform Frequency Shifting Theorem.

20. (4 pts) What does the following instruction do?

add \*ar0-<<#16,ac0

21. (4 pts) What does the following instruction do?

rnd(hi(saturate(ac0))),\*ar1+

22. (8 pts) What do the following symbols denote when programming using the TI mnemonic assembler?

| #  |  |

|----|--|

| \$ |  |

| *  |  |

| Q  |  |

## EECS 452 Digital Signal Processing Design Laboratory Fall 2006

23. (6 pts) A waveform is sampled using rate 8000 samples per second.

The alias frequency is Hz.

Two seconds of waveform samples are DFT'd. The frequency step between DFT values is Hz.

If the waveform had been sampled at 16000 Hz and the DFT of two seconds of sampled had been formed, the frequency step between DFT values would have been Hz.

24. (8 pts) Using the C5510 C/C++ system, variables declared as

| char   | use | bits. |

|--------|-----|-------|

| int    | use | bits. |

| long   | use | bits. |

| double | use | bits. |

25. (8 pts) The C5510 C system uses named memory sections to organize data and code. The following named sections are used to contain what?

| .text  |       |

|--------|-------|

| .bss   | <br>1 |

| .cinit | <br>ı |

| .stack | <br>ı |

- 26. (4 pts) A waveform is sampled using a sample rate of 8 kHz. How many samples are required in order to have a frequency spacing of 2 Hz in the DFT of the sample set?

- 27. (8 pts) The C5510 C system uses a data structure referred to as a *stack* hold six types of information. List four.

(a)

| (b) | )  |  |

|-----|----|--|

| (c) | r) |  |

| (d) | l) |  |

28. (2 pts each) Assume a 8-bit word size with bits ordered most significant bit left most (bit 7) and least significant right most (bit 0). What is the

- (a) Q7 unsigned value of 1000 0000?

- (b) Q7 signed value of 1000 0000?

- (c) Q7 unsigned value of 0100 0000?

- (d) Q7 signed value of 0100 0000?

- (e) Q-2 unsigned value of 1000 0000?

- 29. (2 pts) For proper extended-precision arithmetic in the C5510 the status bit, satd, should be set or cleared to prevent the accumulator from saturating during the computations?

- 30. (4 pts) Given the 16-bit hexadecimal value F237

- (a) express its one's complement using hexadecimal.

- (b) express its two's complement using hexadecimal.

- 31. (8 pts) We normally use positional notation when writing binary numbers. Associated with each position is a weight which is a power of two. For the 6-bit binary number  $b_5b_4b_3b_2b_1b_0$  (Q0) where the *b*'s take on values 0 and 1, what is the weight,

- (a) for unsigned values, associated with  $b_2$ ?

- (b) for unsigned values, associated with  $b_5$ ?

- (c) for two's complement values, associated with  $b_2$ ?

- (d) for two's complement values, associated with  $b_5$ ?

- 32. (4 pts) Because addition and subtraction in a fixed point computer use a fixed word size there are two situations where one can have arithmetic overflow. These are

- (a) \_\_\_\_\_

- (b) \_\_\_\_\_

- 33. (4 pts) Assume multiplication of two *B*-bit numbers with the product being placed into a 2*B*-bit accumulator. When not doing fractional multiplication (frct bit = 0) there is no chance of overflow in the result. When frct bit = 1 it is possible to have an overflow. What values will cause this?

- 34. (4 pts) Multiplication causes bit growth. At some point the least significant bits will be discarded. This can be done by simply truncating or we can round then discard bits. What are the names of the two rounding methods discussed?

- (a)

- (b)

- 35. (2 pts) When implementing floating point, which operation, addition or multiplication, is going to be the more difficult to do?

- 36. (5 pts) The arctangent function implemented in class mapped the radian angle range from \_\_\_\_\_\_ to \_\_\_\_\_ into the range from \_\_\_\_\_\_ to \_\_\_\_\_. using units of

- 37. (4 pts) Polynomial approximations for the arctangent, the base 2 logarithm and square root were discussed. The approximation method of choice was \_\_\_\_\_ the approximation.

- 38. (4 pts) In the homework and lab use was made of the MANT::NEXP instruction. As its name suggests this instruction accomplishes two things:

39. (2 pts) The

data trans-

fer protocol is used on the C5510DSK to program/configure AIC23 CODEC device.

40. (8 pts) You are given a digital filter described using a biquadratic transfer function of the form

$$H(z) = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2}}{1 + a_1 z^{-1} + a_2 z^{-2}}$$

and a sample rate of  $f_s$  Hz.

(a) What is the value of H(z) at 0 Hz?

(b) What is the value of H(z) at  $f_s/2$  Hz?

- 41. (8 pts) If \*(0x100)=1, \*(0x101)=2 and \*(0x102)=3, what will be the content of ACO after the following instructions are executed?

- (a) MOV #0x100,AR0

MOV db1(\*AR0),AC0

- (b) MOV #0x101,AR0 MOV dbl(\*AR0),AC0

- 42. (4 pts) Rewrite the following equation using Horner's method/ordering:

$a_4x^4 + a_3x^3 + a_2x^2 + a_1x^1 + a_0 =$

43. (4 pts) A median of a list of *N* 32-bit unsigned integers can be efficiently determined using how many compare operations?

## EECS 452 Digital Signal Processing Design Laboratory

- 44. (2 pts) VHDL and Verilog are \_\_\_\_\_\_ lan-guages.

- 45. (4 pts) "VHDL allows separation of the internal and external of a digital system.

- An \_\_\_\_\_\_ declaration describes the interface of the design to its external environment.

- An body describes the functionality of the design."

- 46. (2 pts) " is a highlevel design methodology in which the design is described by registers and the necessary of functions describing the transfer of data between these registers."

- 47. (6 pts) Given a *B*-bit A/D converter whose output uses the 2's complement number format. The converter is set so that a zero input voltage corresponds to the mid range of the zero output value. The voltage corresponding to the most negative value is  $-V_p$ .

- (a) The most positive output value is .

- (b) The most negative output value is

- (c) The voltage change which precisely produces a change of one count in the A/D output is  $\Delta V =$ .

- 48. (4 pts) In many instances it is useful to have a nonlinear relationship between the voltage at the input of an A/D converter and its output values. This is particulary true in the telephone system where a compression technique called \_\_\_\_\_\_\_ is used with an 8-

bit A/D converter to give a perceptual quality of a \_\_\_\_\_ bit linear A/D converter.

- 49. (2 pts) The filter used at the input of an A/D converter is termed an filter.

- 50. (2 pts) The filter used at the output of a D/A converter is termed an filter.

- 51. (2 pts) Given the *z*-transform of a filter transfer function the associated frequency response can be determined by evaluating the transfer function where in the *z*-plane?

52. (2 pts) A finite response filter uses the current input sample and the M

- 53. (2 pts) An all-pole filter uses the the current input sample and the N

- 54. (4 pts) Write a line of MATLABcode to generate a table, sine\_table of N samples of one period of an unit amplitude sine wave.

- 55. (4 pts) For the filter shown below draw its transposed form.

56. (4 pts) For the above filter what is the *closed form* (i.e., no summations present) of its transfer function, H(z), when all of the *b* values equal 1?

- 57. (4 pts) Using the notation in the notes write the transfer function of a biquad filter section.

- 58. (8 pts) A set of measurements is made in order to estimate the group delay though a reasonably broad band measurement system.

- Hz phase (degrees)

- 1000 -120

- 1250 90

- 1500 -60

- 1750 150

What is the group delay? Hint: plot the data then think about it.

- 59. Let  $x(t) = 3\sin(2\pi f_{c1}t) + 2\sin(2\pi f_{c2}t)$  where  $f_{c1} = 800$  Hz and  $f_{c2} = 1200$  Hz. We sample the signal at  $f_s = 2500$  Hz.

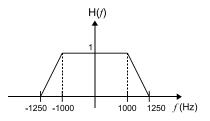

- (a) (2 pts) Before we sample the signal, we pass it through an anti-alias filter. The filter response looks like the following

Can this filter prevent aliasing?

(b) (6 pts) Next we take N = 100 samples at the anti-alias filter output, and take a *N*-point DFT using the "non-standard" definition by multiplying the forward DFT with 1/N. What does the spectrum looks like? Specify the magnitude of the DFT and the range AND the resolution in frequency that can be observed. Is there any leakage?

60. (8 pts) The CORDIC algorithm can be used to calculate arctangents. The brief description of the algorithm is as the following.

Consider  $z = x + jy = re^{j\theta}$ .

The component values of z' = x' + jy' after rotating z = x + jy by angle  $\beta$ :

$$z' = x' + jy' = x\cos(\beta) - y\sin(\beta) + j[x\sin(\beta) + y\cos(\beta)]$$

We can write

$$x'' = \frac{x'}{\cos(\beta)} = x - y \tan(\beta)$$

$$y'' = \frac{y'}{\cos(\beta)} = y + x \tan(\beta)$$

It is clear that the angle associate with x'' + jy'' is exactly the same as the angle of x' + jy'. The magnitude differs however.

Let x = 2 and y = 4. Apply CORDIC to rotate 4 times. What is the resulting approximation to  $\tan^{-1}(y/x)$ ?

| $\beta_0 = \tan^{-1}(1)$   | 0.7845 (rad) |

|----------------------------|--------------|

| $\beta_1 = \tan^{-1}(1/2)$ | 0.4636 (rad) |

| $\beta_2 = \tan^{-1}(1/4)$ | 0.2450 (rad) |

| $\beta_3 = \tan^{-1}(1/8)$ | 0.1244 (rad) |

Hint: don't forget how the rotations change when  $\beta$  is negative.

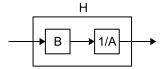

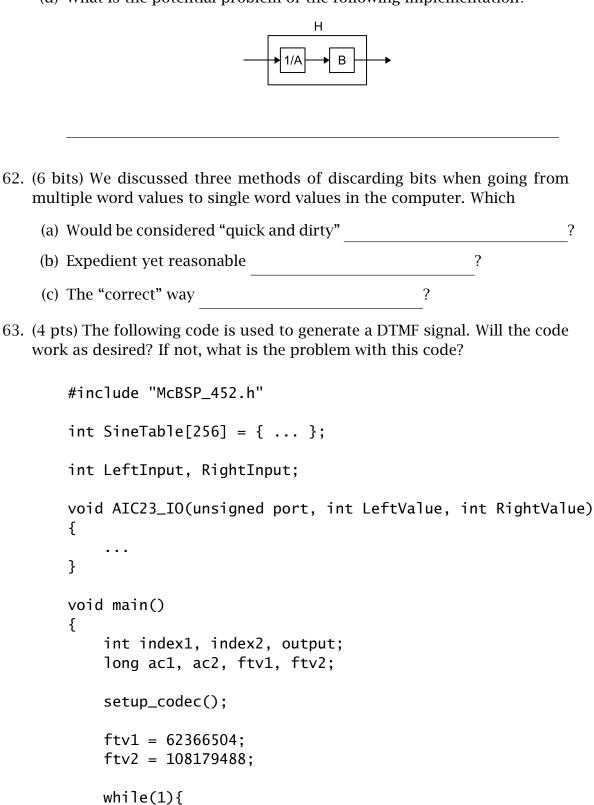

61. (8 pts) Given a filter response  $H(z) = \frac{B(z)}{A(z)}$ .

(a) What is the impact of the poles of H(z) on the signal?

- (b) What is the impact of the zeros of H(z) on the signal?

- (c) What is the potential problem of the following implementation?

(d) What is the potential problem of the following implementation?

```

Fall 2006

```

```

ac1 = ac1 + ftv1;

ac2 = ac2 + ftv2;

index1 = ac1 >> (32-8);

index2 = ac2 >> (32-8);

output = SineTable[index1] + SineTable[index2];

AIC23_I0(2,output,RightInput);

}

```

64. (2 pts) In the lab exercises with our own interrupt support, what is the reason for the following error message when building the project

error: can't allocate vectors?

What is the work around to solve this problem?

65. (2 pts) In lab 7, if we input a sine wave at 25000 where will it show up (in Hz) on the output display?

66. (4 pts) When changing the clock rate of C5510 by modifying the divide and multiply factors in the CLKMD register, how do we determine when the clock rate has actually changed to the desired one and ready for our task?