# C55x v3.x CPU

# Reference Guide

Literature Number: SWPU073E June 2009

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

# **Read This First**

#### About This Manual

This manual describes the architecture, registers, and operation of the fixed-point TMS320C55x<sup>™</sup> digital signal processor (DSP) CPU.

#### About This Maual Release

This release is updated with the 3.x Revision of the TMS320C55x DSP. Information not affected by the revision remains identical to the previous manual. The main new features of this revision are:

- The 23-bit linear data addressing feature, which affects only the indirect addressing mode and the circular addressing mode. All other addressing modes or I/O space addressing mode remain the same as in the previous manual. All information on this feature is in Chapter 6.

- Data read bus extension to 32-bit (BB bus). It introduces the new double coefficient indirect addressing mode. All information on this feature is in Chapter 1.

- Program bus extension to 32-bit (PB bus) and IBQ size enlarged to 128 bytes. Instruction decoder can now accept 8 bytes of program code from the instruction buffer queue. All information on this feature is in Chapter 1.

#### How to Use This Manual

#### Chapter 1 CPU Architecture

This chapter describes the CPU architecture of the TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSP.

#### Chapter 2 CPU Registers

This chapter describes the main registers in the C55x<sup>™</sup> DSP CPU.

#### Chapter 3 Memory and I/O Space

This chapter describes the unified data/program space and the I/O space in the TMS320C55x™ DSP.

#### Chapter 4 Stack Operation

This chapter introduces the two stacks located on each TMS320C55 $x^{TM}$  (C55 $x^{TM}$ ) DSP.

#### **Chapter 5** Interrupt and Reset Operation

This chapter describes the available interrupts of the TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSP, how some of them can be blocked through software, and how all of them are handled by the CPU.

#### Chapter 6 Addressing Modes

This chapter describes the modes available for addressing the data space (including CPU registers) and the I/O space of the TMS320C55 $x^{TM}$  (C55 $x^{TM}$ ) DSP.

#### **Notational Conventions**

This document uses the following conventions.

- The device number TMS320C55x is often abbreviated as C55x.

- Active-low signals are indicated with an overbar (for example, RESET).

- Program listings, program examples, and interactive displays are shown in a special typeface.

- In most cases, hexadecimal numbers are shown with the suffix h. For example, the following number is a hexadecimal 40 (decimal 64):

40h

Similarly, binary numbers usually are shown with the suffix b. For example, the following number is the decimal number 4 shown in binary form:

0100b

| П | Bits and signals a | are sometimes | referenced with | the following | notations: |

|---|--------------------|---------------|-----------------|---------------|------------|

|   |                    |               |                 |               |            |

| Notation      | Description                  | Example                                                                 |

|---------------|------------------------------|-------------------------------------------------------------------------|

| Register(n-m) | Bits n through m of Register | AC0(15–0) represents the 16 least significant bits of the register AC0. |

| Bus[n:m]      | Signals n through m of Bus   | A[21:1] represents signals 21 through 1 of the external address bus.    |

#### The following terms are used to name portions of data:

| Term   | Description            | Example                                 |

|--------|------------------------|-----------------------------------------|

| LSB    | Least significant bit  | In AC0(15–0), bit 0 is the LSB.         |

| MSB    | Most significant bit   | In AC0(15-0), bit 15 is the MSB.        |

| LSByte | Least significant byte | In AC0(15-0), bits 7-0 are the LSByte.  |

| MSByte | Most significant byte  | In AC0(15-0), bits 15-8 are the MSByte. |

| LSW    | Least significant word | In AC0(31-0), bits 15-0 are the LSW.    |

| MSW    | Most significant word  | In AC0(31-0), bits 31-16 are the MSW.   |

#### Related Documentation From Texas Instruments

The following books describe the TMS320C55x devices and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477-8924. When ordering, please identify the book by its title and literature number.

**TMS320C55x Technical Overview** (literature number SPRU393). This overview is an introduction to the TMS320C55x<sup>™</sup> digital signal processors (DSPs), the latest generation of fixed-point DSPs in the TMS320C5000<sup>™</sup> DSP platform. Like the previous generations, this processor is optimized for high performance and low-power operation. This book describes the CPU architecture, low-power enhancements, and embedded emulation features.

**TMS320C55x DSP Peripherals Reference Guide** (literature number SPRU317) describes the peripherals, interfaces, and related hardware that are available on TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSPs. It also describes how you can use software (idle configurations) to turn on or off individual portions of the DSP, so that you can manage power consumption.

- C55x CPU Algebraic Instruction Set Reference Guide (literature number SWPU068) describes the TMS320C55x<sup>™</sup> CPU algebraic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the mnemonic instruction set.

- C55x CPU Mnemonic Instruction Set Reference Guide (literature number SWPU067) describes the TMS320C55x™ CPU mnemonic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the algebraic instruction set.

- **TMS320C55x Optimizing C Compiler User's Guide** (literature number SPRU281) describes the TMS320C55x<sup>™</sup> C Compiler. This C compiler accepts ANSI standard C source code and produces assembly language source code for TMS320C55x devices.

- TMS320C55x Assembly Language Tools User's Guide (literature number SPRU280) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for TMS320C55x™ devices.

- **TMS320C55x Programmer's Guide** (literature number SPRU376) describes ways to optimize C and assembly code for the TMS320C55x<sup>™</sup> DSPs and explains how to write code that uses special features and instructions of the DSP.

#### **Trademarks**

TMS320C54x, C54x, TMS320C55x, and C55x are trademarks of Texas Instruments.

# **Contents**

| 1 | CPU | Archite | cture                                                | 1-1  |

|---|-----|---------|------------------------------------------------------|------|

|   | 1.1 | Overvi  | iew of the CPU Architecture                          | 1-2  |

|   |     | 1.1.1   | Internal Data and Address Buses                      |      |

|   |     | 1.1.2   | Memory Interface Unit                                |      |

|   |     | 1.1.3   | Instruction Buffer Unit (I Unit)                     |      |

|   |     | 1.1.4   | Program Flow Unit (P Unit)                           |      |

|   |     | 1.1.5   | Address-Data Flow Unit (A Unit)                      |      |

|   |     | 1.1.6   | Data Computation Unit (D Unit)                       |      |

|   | 1.2 | Instruc | ction Buffer Unit (I Unit)                           |      |

|   |     | 1.2.1   | Instruction Buffer Queue                             |      |

|   |     | 1.2.2   | Instruction Decoder                                  |      |

|   | 1.3 | Progra  | am Flow Unit (P Unit)                                | 1-8  |

|   |     | 1.3.1   | Program-Address Generation and Program-Control Logic |      |

|   |     | 1.3.2   | P-Unit Registers                                     |      |

|   | 1.4 | Addres  | ss-Data Flow Unit (A Unit)                           | 1-10 |

|   |     | 1.4.1   | Data-Address Generation Unit (DAGEN)                 |      |

|   |     | 1.4.2   | A-Unit Arithmetic Logic Unit (A-Unit ALU)            |      |

|   |     | 1.4.3   | A-Unit Registers                                     | 1-11 |

|   | 1.5 | Data C  | Computation Unit (D Unit)                            |      |

|   |     | 1.5.1   | Shifter                                              | 1-13 |

|   |     | 1.5.2   | D-Unit Arithmetic Logic Unit (D-Unit ALU)            | 1-13 |

|   |     | 1.5.3   | Two Multiply-and-Accumulate Units (MACs)             | 1-14 |

|   |     | 1.5.4   | D-Unit Bit Manipulation Unit (D-Unit BIT)            | 1-14 |

|   |     | 1.5.5   | D-Unit Registers                                     | 1-15 |

|   | 1.6 | Addres  | ss Buses and Data Buses                              | 1-16 |

|   | 1.7 | Instruc | ction Pipeline                                       | 1-20 |

|   |     | 1.7.1   | Pipeline Phases                                      | 1-20 |

|   |     | 1.7.2   | Pipeline Protection                                  | 1-23 |

| 2 | CPU | Registe | ers                                                  | 2-1  |

|   | 2.1 | Alphab  | betical Summary of Registers                         | 2-2  |

|   | 2.2 | Memo    | ry-Mapped Registers                                  | 2-4  |

|   | 2.3 | Accum   | nulators (AC0–AC3)                                   | 2-9  |

|   | 2.4 |         | tion Registers (TRN0, TRN1)                          |      |

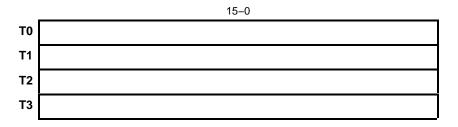

|   | 2.5 | Tempo   | prary Registers (T0-T3)                              | 2-11 |

|   | 2.6 | Regist  | ters Used to Address Data Space and I/O Space        | 2-12 |

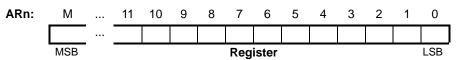

|   |      | 2.6.1   | Auxiliary Registers (XAR0–XAR7 / AR0–AR7)                                  | 2-12 |

|---|------|---------|----------------------------------------------------------------------------|------|

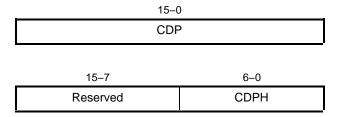

|   |      | 2.6.2   | Coefficient Data Pointer (XCDP / CDP)                                      | 2-14 |

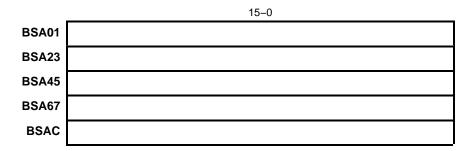

|   |      | 2.6.3   | Circular Buffer Start Address Registers (BSA01, BSA23, BSA45, BSA67, BSAC) | 2-15 |

|   |      | 2.6.4   | Circular Buffer Size Registers (BK03, BK47, BKC)                           |      |

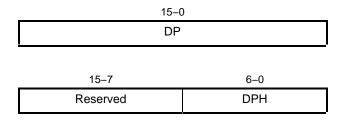

|   |      | 2.6.5   | Data Page Register (XDP / DP)                                              |      |

|   |      | 2.6.6   | Peripheral Data Page Register (PDP)                                        |      |

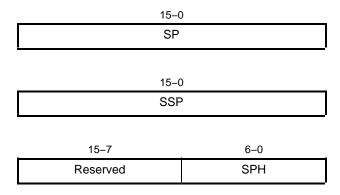

|   |      | 2.6.7   | Stack Pointers (XSP / SP, XSSP / SSP)                                      |      |

|   | 2.7  | Prograi | m Flow Registers (PC, RETA, CFCT)                                          |      |

|   |      | 2.7.1   | Context Bits Stored in CFCT                                                |      |

|   | 2.8  | Registe | ers For Managing Interrupts                                                | 2-24 |

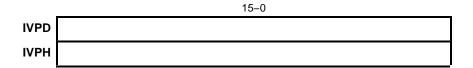

|   |      | 2.8.1   | Interrupt Vector Pointers (IVPD, IVPH)                                     | 2-24 |

|   |      | 2.8.2   | Interrupt Flag Registers (IFR0, IFR1)                                      | 2-25 |

|   |      | 2.8.3   | Interrupt Enable Registers (IER0, IER1)                                    | 2-28 |

|   |      | 2.8.4   | Debug Interrupt Enable Registers (DBIER0, DBIER1)                          | 2-31 |

|   | 2.9  | Registe | ers for Controlling Repeat Loops                                           | 2-35 |

|   |      | 2.9.1   | Single-Repeat Registers (RPTC, CSR)                                        | 2-35 |

|   |      | 2.9.2   | Block-Repeat Registers (BRC0-1, BRS1, RSA0-1, REA0-1)                      | 2-35 |

|   | 2.10 | Status  | Registers (ST0_55–ST3_55)                                                  | 2-38 |

|   |      | 2.10.1  | ST0_55 Bits                                                                | 2-40 |

|   |      |         | ST1_55 Bits                                                                |      |

|   |      |         | ST2_55 Bits                                                                |      |

|   |      | 2.10.4  | ST3_55 Bits                                                                | 2-58 |

| 3 | Memo | ory and | I/O Space                                                                  | 3-1  |

|   | 3.1  | Memor   | y Map                                                                      | 3-2  |

|   | 3.2  | Prograi | m Space                                                                    | 3-3  |

|   |      | 3.2.1   | Byte Addresses (24 Bits)                                                   | 3-3  |

|   |      | 3.2.2   | Instruction Organization in Program Space                                  | 3-3  |

|   |      | 3.2.3   | Alignment of Fetches From Program Space                                    | 3-4  |

|   | 3.3  | Data S  | pace                                                                       | 3-5  |

|   |      | 3.3.1   | Word Addresses (23 Bits)                                                   | 3-5  |

|   |      | 3.3.2   | Data Types                                                                 |      |

|   |      | 3.3.3   | Data Organization in Data Space                                            | 3-7  |

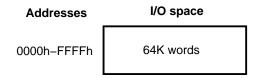

|   | 3.4  |         | ace                                                                        |      |

|   | 3.5  | Boot Lo | pader                                                                      | 3-8  |

| 4 |      |         | ion                                                                        |      |

|   | 4.1  |         | tack and System Stack                                                      |      |

|   | 4.2  |         | Configurations                                                             |      |

|   | 4.3  |         | eturn Versus Slow Return                                                   |      |

|   | 4.4  |         | atic Context Switching                                                     |      |

|   |      | 4.4.1   | Fast-Return Context Switching for Calls                                    |      |

|   |      | 4.4.2   | Fast-Return Context Switching for Interrupts                               | 4-9  |

|   |       | 4.4.3    | Slow-Return Context Switching for Calls                               | 4-9  |

|---|-------|----------|-----------------------------------------------------------------------|------|

|   |       | 4.4.4    | Slow-Return Context Switching for Interrupts                          | 4-10 |

| 5 | Inter | rupt and | d Reset Operation                                                     | 5-1  |

|   | 5.1   | -        | uction to the Interrupts                                              |      |

|   | 5.2   |          | pt Vectors and Priorities                                             |      |

|   | 5.3   |          | able Interrupts                                                       |      |

|   |       | 5.3.1    | Bit and Registers Used To Enable Maskable Interrupts                  |      |

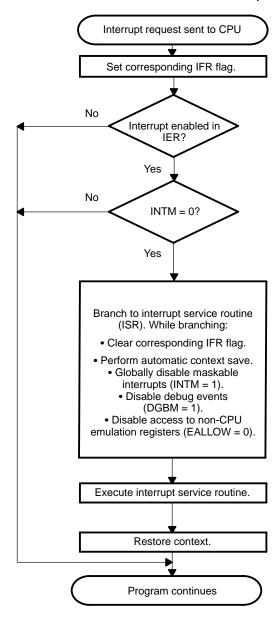

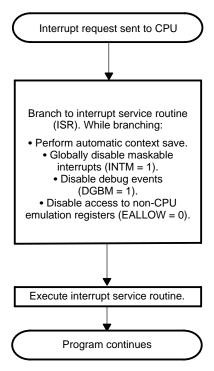

|   |       | 5.3.2    | Standard Process Flow for Maskable Interrupts                         |      |

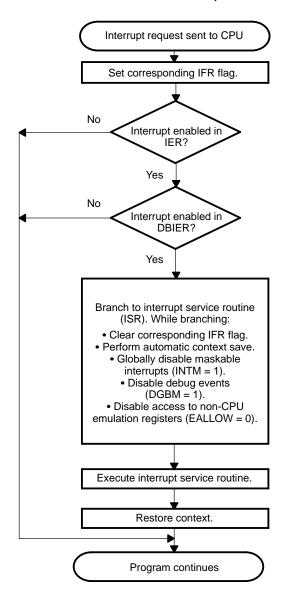

|   |       | 5.3.3    | Process Flow for Time-Critical Interrupts                             |      |

|   | 5.4   | Nonma    | askable Interrupts                                                    |      |

|   |       | 5.4.1    | Standard Process Flow for Nonmaskable Interrupts                      |      |

|   | 5.5   | DSP R    | Reset                                                                 |      |

|   |       | 5.5.1    | DSP Hardware Reset                                                    | 5-22 |

|   |       | 5.5.2    | Software Reset                                                        | 5-22 |

| 6 | Addr  | essina   | Modes                                                                 | 6-1  |

|   | 6.1   |          | uction to the Addressing Modes                                        |      |

|   | 6.2   |          | ute Addressing Modes                                                  |      |

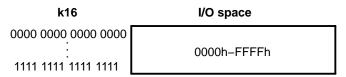

|   |       | 6.2.1    | k16 Absolute Addressing Mode                                          |      |

|   |       | 6.2.2    | k23 Absolute Addressing Mode                                          |      |

|   |       | 6.2.3    | I/O Absolute Addressing Mode                                          |      |

|   | 6.3   | Direct   | Addressing Modes                                                      | 6-7  |

|   |       | 6.3.1    | DP Direct Addressing Mode                                             |      |

|   |       | 6.3.2    | SP Direct Addressing Mode                                             | 6-10 |

|   |       | 6.3.3    | Register-Bit Direct Addressing Mode                                   | 6-11 |

|   |       | 6.3.4    | PDP Direct Addressing Mode                                            | 6-12 |

|   | 6.4   | Indired  | ct Addressing Modes                                                   | 6-13 |

|   |       | 6.4.1    | AR Indirect Addressing Mode                                           | 6-14 |

|   |       | 6.4.2    | Dual AR Indirect Addressing Mode                                      | 6-25 |

|   |       | 6.4.3    | CDP Indirect Addressing Mode                                          | 6-28 |

|   |       | 6.4.4    | Coefficient Indirect Addressing Mode                                  | 6-31 |

|   |       | 6.4.5    | Addressing Data Memory                                                | 6-35 |

|   |       | 6.4.6    | Addressing Data Memory With Absolute Addressing Modes                 | 6-35 |

|   |       | 6.4.7    | Addressing Data Memory With Direct Addressing Modes                   |      |

|   |       | 6.4.8    | Addressing Data Memory With Indirect Addressing Modes                 | 6-37 |

|   | 6.5   | Addres   | ssing Memory-Mapped Registers                                         |      |

|   |       | 6.5.1    | Addressing MMRs With the k16 and k23 Absolute Addressing Modes        | 6-60 |

|   |       | 6.5.2    | Addressing MMRs With the DP Direct Addressing Mode                    | 6-61 |

|   |       | 6.5.3    | Addressing MMRs With Indirect Addressing Modes                        |      |

|   | 6.6   | Restric  | ctions on Accesses to Memory-Mapped Registers                         | 6-83 |

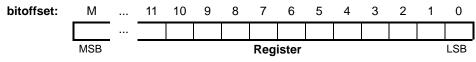

|   | 6.7   | Addres   | ssing Register Bits                                                   |      |

|   |       | 6.7.1    | Addressing Register Bits With the Register-Bit Direct Addressing Mode |      |

|   |       | 6.7.2    | Addressing Register Bits With Indirect Addressing Modes               | 6-85 |

| 6.8   | Addres  | sing I/O Space                                             | . 6-99 |

|-------|---------|------------------------------------------------------------|--------|

|       | 6.8.1   | Addressing I/O Space With the I/O Absolute Addressing Mode | . 6-99 |

|       | 6.8.2   | Addressing I/O Space With the PDP Direct Addressing Mode   | 6-100  |

|       | 6.8.3   | Addressing I/O Space With Indirect Addressing Modes        | 6-100  |

| 6.9   | Restric | tions on Accesses to I/O Space                             | 6-111  |

| 6.10  | Circula | r Addressing                                               | 6-112  |

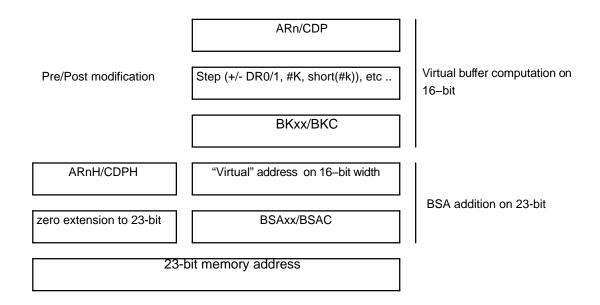

|       | 6.10.1  | Configuring AR0–AR7 and CDP for Circular Addressing        | 6-113  |

|       | 6.10.2  | Circular Buffer Implementation                             | 6-113  |

|       | 6.10.3  | TMS320C54x DSP Compatibility                               | 6-116  |

| Index |         | Ir                                                         | ıdex-1 |

# **Figures**

| 1–1  | CPU Diagram                                                        | 1-2 |

|------|--------------------------------------------------------------------|-----|

| 1–2  | Instruction Buffer Unit (I Unit) Diagram                           |     |

| 1–3  | Program Flow Unit (P Unit) Diagram                                 |     |

| 1–4  | Address-Data Flow Unit (A Unit) Diagram                            |     |

| 1–5  | Data Computation Unit (D Unit) Diagram                             |     |

| 1–6  | First Segment of the Pipeline (Fetch Pipeline)                     |     |

| 1–7  | Second Segment of the Pipeline (Execution Pipeline)                |     |

| 2–1  | Accumulators                                                       |     |

| 2–2  | Transition Registers                                               |     |

| 2–3  | Temporary Registers                                                |     |

| 2–4  | Extended Auxiliary Registers and Their Parts                       |     |

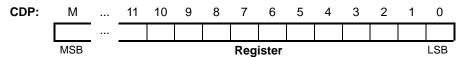

| 2–5  | Extended Coefficient Data Pointer and Its Parts                    |     |

| 2–6  | Circular Buffer Start Address Registers                            |     |

| 2–7  | Circular Buffer Size Registers                                     |     |

| 2–8  | Extended Data Page Register and Its Parts                          |     |

| 2–9  | Peripheral Data Page Register                                      |     |

| 2–10 | Extended Stack Pointers                                            |     |

| 2–11 | Interrupt Vector Pointers                                          |     |

| 2–12 | Interrupt Flag Registers                                           |     |

| 2–13 | Interrupt Enable Registers                                         |     |

| 2–14 | Debug Interrupt Enable Registers                                   |     |

| 2–15 | Single-Repeat Registers                                            |     |

| 2–16 | Status Registers                                                   |     |

| 3–1  | -Memory Map                                                        |     |

| 4–1  | Extended Stack Pointers                                            |     |

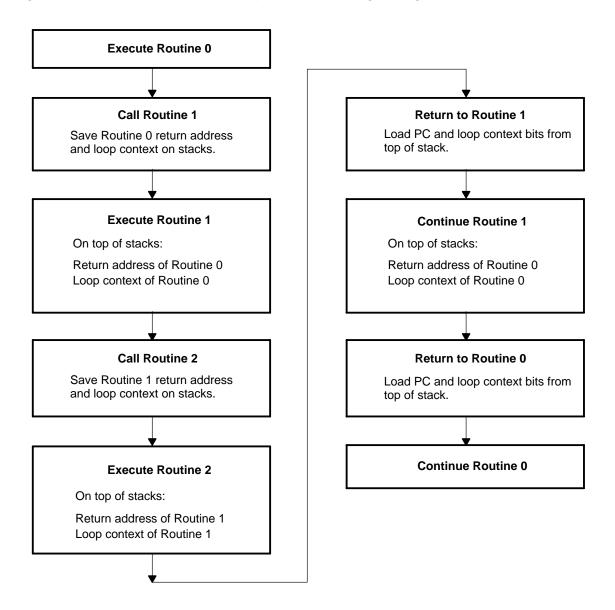

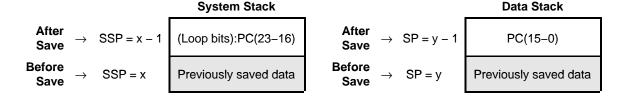

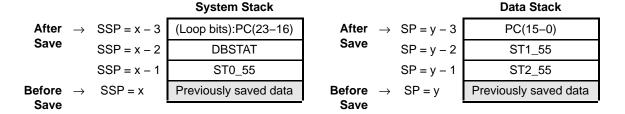

| 4–2  | Return Address and Loop Context Passing During Slow-Return Process |     |

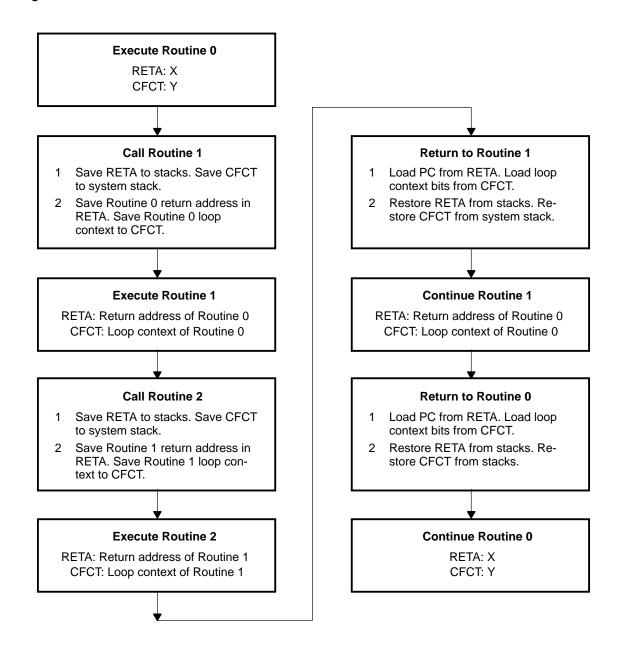

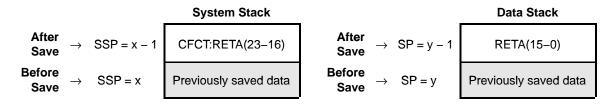

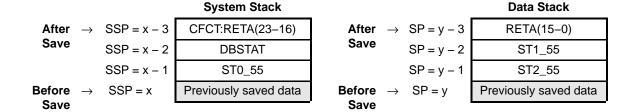

| 4–3  | Use of RETA and CFCT in Fast-Return Process                        |     |

| 5–1  | Standard Process Flow for Maskable Interrupts                      |     |

| 5–2  | Process Flow for Time-Critical Interrupts                          |     |

| 5–3  | Standard Process Flow for Nonmaskable Interrupts                   |     |

| 6–1  | k16 Absolute Addressing Mode                                       |     |

| 6–2  | k23 Absolute Addressing Mode                                       |     |

| 6–3  | I/O Absolute Addressing Mode                                       |     |

| 6–4  | DP Direct Addressing Mode                                          |     |

| 6–5  | SP Direct Addressing Mode                                          |     |

| 6–6  | Register-Bit Direct Addressing Mode                                |     |

| 6–7  | PDP Direct Addressing Mode                                     | 6-12  |

|------|----------------------------------------------------------------|-------|

| 6–8  | Accessing Data Space With the AR Indirect Addressing Mode      | 6-15  |

| 6–9  | Accessing Register Bit(s) With the AR Indirect Addressing Mode | 6-15  |

| 6–10 | Accessing I/O Space With the AR Indirect Addressing Mode       | 6-16  |

| 6–11 | Accessing Data Space With the CDP Indirect Addressing Mode     | 6-29  |

| 6–12 | Accessing Register Bits With the CDP Indirect Addressing Mode  | 6-29  |

| 6–13 | Accessing I/O Space With the CDP Indirect Addressing Mode      | 6-30  |

| 6–14 | Circular Buffer Computation in 23-bit                          | 6-115 |

# **Tables**

| 1–1  | Instructions Performed in D-Unit BIT Module                                                                | 1-14          |

|------|------------------------------------------------------------------------------------------------------------|---------------|

| 1–2  | Functions of the Address and Data Buses                                                                    | 1-16          |

| 1–3  | Bus Usage By Access Type                                                                                   | 1-17          |

| 1-4  | Examples to Illustrate Execution Pipeline Activity                                                         | 1-22          |

| 2–1  | Alphabetical Summary of Registers                                                                          | 2-2           |

| 2–2  | Memory-Mapped Registers                                                                                    | 2-4           |

| 2–3  | Extended Auxiliary Registers and Their Parts                                                               | 2-13          |

| 2–4  | Extended Coefficient Data Pointer and Its Parts                                                            | 2-15          |

| 2–5  | Circular Buffer Start Address Registers and The Associated Pointers                                        | 2-16          |

| 2–6  | Circular Buffer Size Registers and The Associated Pointers                                                 | 2-17          |

| 2–7  | Extended Data Page Register and Its Parts                                                                  | 2-18          |

| 2–8  | Stack Pointer Registers                                                                                    | 2-20          |

| 2–9  | Program Flow Registers                                                                                     | 2-22          |

| 2–10 | Vectors and the Formation of Vector Addresses                                                              | 2-25          |

| 2–11 | Block-Repeat Register Descriptions                                                                         | 2-37          |

| 2–12 | Categories of Branch Instructions                                                                          | 2-62          |

| 2–13 | Minimum Number of Instruction Cycles Required Between an MPNMC-Update Instruction and a Branch Instruction | 2 <b>-</b> 62 |

| 3–1  | Byte Load and Byte Store Instructions                                                                      |               |

| 4–1  | Stack Pointer Registers                                                                                    | 4-3           |

| 4–2  | Stack Configurations                                                                                       | 4-4           |

| 5–1  | Interrupt Vectors Sorted By ISR Number                                                                     | 5-4           |

| 5–2  | Interrupt Vectors Sorted By Priority                                                                       | 5-6           |

| 5–3  | Steps in the Standard Process Flow for Maskable Interrupts                                                 | 5-11          |

| 5–4  | Steps in the Process Flow for Time-Critical Interrupts                                                     | 5-13          |

| 5–5  | Steps in the Standard Process Flow for Nonmaskable Interrupts                                              | 5-16          |

| 5–6  | Effects of a Reset on CPU Registers                                                                        | 5-17          |

| 6–1  | Syntax Elements                                                                                            | 6-3           |

| 6–2  | Absolute Addressing Modes                                                                                  | 6-4           |

| 6–3  | DSP Mode (ARMS = 0) Operands for the AR Indirect Addressing Mode                                           | 6-17          |

| 6–4  | Control Mode (ARMS = 1) Operands for the AR Indirect Addressing Mode                                       | 6-22          |

| 6–5  | Summary of Indirect Operands                                                                               | 6-24          |

| 6–6  | Dual AR Indirect Operands                                                                                  |               |

| 6–7  | CDP Indirect Operands                                                                                      | 6-30          |

| 6–8  | Instruction Syntax                                                                                         |               |

| 6–9  | Coefficient/Double Coefficient Indirect Operands                                                           |               |

| 6–10 | *abs16(#k16) Used For Data-Memory Access              | 6-36  |

|------|-------------------------------------------------------|-------|

| 6–11 | (#k23) Used For Data-Memory Access                    | 6-36  |

| 6–12 | @Daddr Used For Data-Memory Access                    | 6-37  |

| 6–13 | *SP(offset) Used For Data-Memory Access               | 6-37  |

| 6-14 | Choosing an Indirect Operand For a Data Memory Access | 6-38  |

| 6–15 | *abs16(#k16) Used For Memory-Mapped Register Access   | 6-61  |

| 6–16 | *(#k23) Used For Memory-Mapped Register Access        | 6-61  |

| 6–17 | @Daddr Used For Memory-Mapped Register Access         | 6-62  |

| 6–18 | Indirect Operands For Memory-Mapped Register Accesses | 6-64  |

| 6–19 | @bitoffset Used For Register-Bit Access               | 6-84  |

| 6-20 | Indirect Operands For Register-Bit Accesses           | 6-86  |

| 6-21 | *port(#k16) or port(#k16) Used For I/O-Space Access   | 6-99  |

| 6-22 | @Poffset Used For I/O-Space Access                    | 6-100 |

| 6-23 | Indirect Operands For I/O-Space Accesses              | 6-101 |

| 6-24 | Illegal I/O Access Operands                           | 6-111 |

# **Chapter 1**

# **CPU Architecture**

This chapter describes the CPU architecture of the TMS320C55 $x^{TM}$  (C55 $x^{TM}$ ) DSP. It gives conceptual details about the four functional units of the CPU and about the buses that carry instructions and data. It also describes the parallel phases of the instruction pipeline and the pipeline protection mechanism (which prevents read and write operations from happening out of the intended order).

| Topi | C Page                               |

|------|--------------------------------------|

| 1.1  | Overview of the CPU Architecture 1-2 |

| 1.2  | Instruction Buffer Unit (I Unit) 1-6 |

| 1.3  | Program Flow Unit (P Unit)           |

| 1.4  | Address-Data Flow Unit (A Unit)      |

| 1.5  | Data Computation Unit (D Unit) 1-12  |

| 1.6  | Address Buses and Data Buses 1-16    |

| 1.7  | Instruction Pipeline 1-20            |

|      |                                      |

### 1.1 Overview of the CPU Architecture

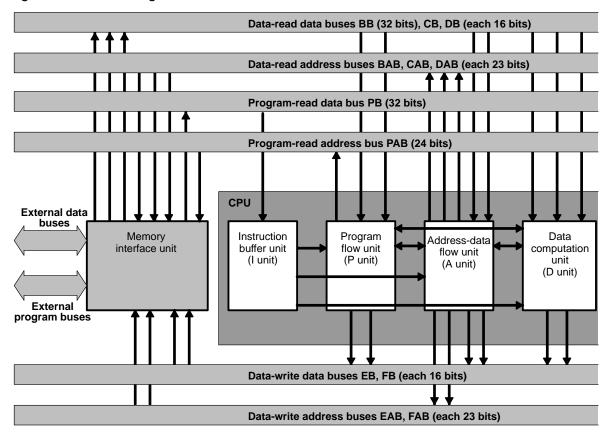

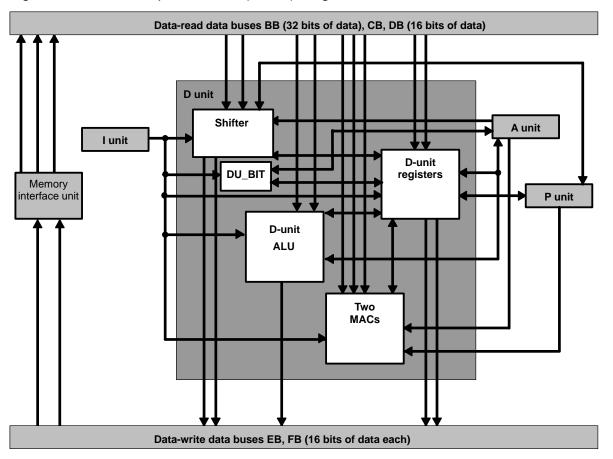

Figure 1–1 shows a conceptual block diagram of the CPU. Sections 1.1.1 through 1.1.6 describe the buses and units represented in the figure.

Figure 1-1. CPU Diagram

#### 1.1.1 Internal Data and Address Buses

The buses shown in Figure 1–1 are:

Data-Read Data Buses (BB, CB, DB).BB carries 32-bit data; CB and DB carry 16-bit data from data space or I/O space to functional units of the CPU.

The 32-bit BB bus only carries data from internal memory to the D unit (primarily to the dual multiply-and-accumulate (MAC) unit). BB is not connected to external memory. Specific instructions enable you to use BB, CB, and DB to read four operands at the same time.

#### Note:

BB and BAB are not connected to external memory. If an instruction fetches an operand using BB or BAB, the operand must be in internal memory. Inadvertent use of an external memory address generates a bus-error interrupt.

CB and DB feed data to the P unit, the A unit, and the D unit. Instructions that read two operands at once use both CB and DB. Instructions that perform single read operations use DB.

Data-Read Address Buses (BAB, CAB, DAB). These three buses carry 23-bit word data addresses to the memory interface unit, which then fetches the data from memory and transfers the requested values to the data-read data buses. All data-space addresses are generated in the A unit.

BAB carries addresses for data that is carried from internal memory to the CPU on BB.

CAB carries addresses for data that is carried to the CPU on CB.

DAB carries addresses for data that is carried to the CPU on only DB or both CB and DB.

- Program-Read Data Bus (PB). PB carries 32 bits (4 bytes) of program code at a time to the I unit, where instructions are decoded.

- Program-Read Address Bus (PAB). PAB carries the 24-bit byte program address of the program code that is carried to the CPU by PB.

- Data-Write Data Buses (EB, FB). These two buses carry 16-bit data from functional units of the CPU to data space or I/O space.

EB and FB receive data from the P unit, the A unit, and the D unit. Instructions that write two 16-bit values to memory at once use both EB and FB. Instructions that perform single write operations use EB.

Data-Write Address Buses (EAB, FAB). These two buses carry 23-bit addresses to the memory interface unit, which then receives the values driven on the data-write data buses. All data-space addresses are generated in the A unit.

EAB carries addresses for data that is carried to memory on only EB or both EB and FB.

FAB carries addresses for data that is carried to memory on FB.

### 1.1.2 Memory Interface Unit

The memory interface mediates all data transfers between the CPU and program/data space or I/O space.

### 1.1.3 Instruction Buffer Unit (I Unit)

During each CPU cycle, the I unit receives 4 bytes of program code into its instruction buffer queue and decodes 1 to 8 bytes of code that were previously received in the queue. The I unit then passes data to the P unit, the A unit, and the D unit for the execution of instructions. For example, any constants that were encoded in instructions (for loading registers, providing shift counts, identifying bit numbers, etc.) are isolated in the I unit and passed to the appropriate unit.

The instruction buffer queue is emptied whenever the CPU branches to a new location.

The instruction buffer queue is loaded (but not necessarily full) for single-repeat and local-repeat operations.

# 1.1.4 Program Flow Unit (P Unit)

The P unit generates all program-space addresses and sends them out on PAB. It also controls the sequence of instructions by directing operations such as hardware loops, branches, and conditional execution.

## 1.1.5 Address-Data Flow Unit (A Unit)

The A unit contains all the logic and registers necessary to generate the dataspace addresses and send them out on BAB, CAB, and DAB. It also contains a 16-bit arithmetic logic unit (ALU) that can perform arithmetical, logical, shift, and saturation operations.

# 1.1.6 Data Computation Unit (D Unit)

The D unit contains the primary computational units of the CPU:

- A 40-bit barrel shifter that provides a shift range of –32 to 31.

- A 40-bit arithmetic logic unit (ALU) that can perform arithmetical, logical, rounding, and saturation operations.

- A bit manipulation unit that performs specific bit manipulation operations.

- A pair of multiply-and-accumulate units (MACs) that can perform a 17-bit multiplication and a 40-bit addition or subtraction in a single cycle.

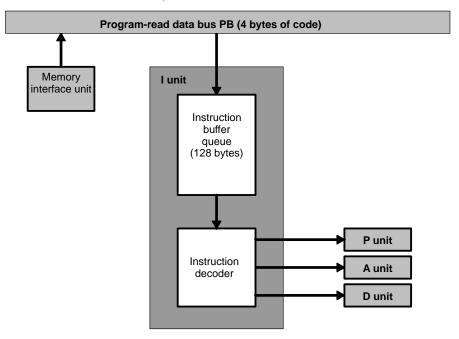

# 1.2 Instruction Buffer Unit (I Unit)

The I unit receives program code into its instruction buffer queue and decodes instructions. The I unit then passes data to the P unit, the A unit, and the D unit for the execution of instructions. Figure 1–2 shows a conceptual block diagram of the I unit. Sections 1.2.1 and 1.2.2 describe the main parts of the I unit.

Figure 1–2. Instruction Buffer Unit (I Unit) Diagram

# 1.2.1 Instruction Buffer Queue

The CPU fetches 32 bits at a time from program memory. The program-read data bus (PB) carries these 32 bits from memory to the instruction buffer queue. The queue can hold up to 128 bytes of undecoded instructions. When the CPU is ready to decode instructions, 8 bytes are transferred from the queue to the instruction decoder.

In addition to helping with the pipelining of instructions, the queue enables:

- The execution of a block of code stored in the queue. (The queue is used in conjunction with the local repeat instruction. The local repeat instructing size is 128 bytes to fit within the IBQ.)

- Speculative fetching of instructions while a condition is being tested for one of the following instructions:

- Conditional branch

- Conditional call

- Conditional return

#### 1.2.2 Instruction Decoder

In the decode phase of the instruction pipeline, the instruction decoder accepts 8 bytes of program code from the instruction buffer queue and decodes those bytes. The instruction decoder:

- Identifies instruction boundaries so that it can decode 8-, 16-, 24-, 32-, 40-, and 64-bit instructions

- Determines whether the CPU has been instructed to execute two instructions in parallel.

- Sends decoded execution commands and immediate values to the program flow unit (P unit), the address-data flow unit (A unit), and the data computation unit (D unit)

Certain instructions enable writing of immediate values directly to memory or I/O space by way of a dedicated data path.

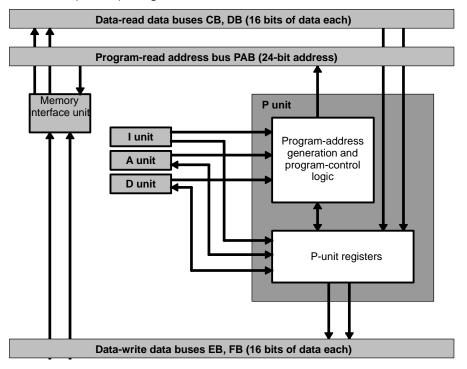

# 1.3 Program Flow Unit (P Unit)

The P unit generates all program-space addresses. It also controls the sequence of instructions. Figure 1–3 shows a conceptual block diagram of the P unit. Sections 1.3.1 and 1.3.2 describe the main parts of the P unit.

Figure 1–3. Program Flow Unit (P Unit) Diagram

# 1.3.1 Program-Address Generation and Program-Control Logic

The program-address generation logic is responsible for generating 24-bit addresses for fetches from program memory. Normally, it generates sequential addresses. However, for instructions that require reads from nonsequential addresses, the program-address generation logic can accept immediate data from the I unit and register values from the D unit. Once an address is generated, it is carried to memory by the program-read address bus (PAB).

The program control logic accepts immediate values from the I unit and test results from the A unit or the D unit, and performs the following actions:

- Tests whether a condition is true for a conditional instruction and communicates the result to the program-address generation logic

- Initiates interrupt servicing when an interrupt is requested and properly enabled

- Controls the repetition of a single instruction preceded by a single-repeat instruction, or a block of instructions preceded by a block-repeat instruction. You can implement three levels of loops by nesting a block-repeat operation within another block-repeat operation and including a single-repeat operation in either or both of the repeated blocks. All repeat operations are interruptible.

- Manages instructions that are executed in parallel. Parallelism within the C55x DSP enables the execution of program-control instructions at the same time as data processing instructions.

# 1.3.2 P-Unit Registers

The P unit contains and uses the registers listed in the following table. Access to the program flow registers is limited. You cannot read from or write to PC. You can access RETA and CFCT only with the following syntaxes:

MOV dbl(Lmem), RETA

MOV RETA, dbl(Lmem)

All the other registers can be loaded with immediate values (from the I unit) and can communicate bidirectionally with data memory, I/O space, the A-unit registers, and the D-unit registers.

#### **Program Flow Registers**

PC Program counter

RETA Return address register

CFCT Control flow context register

#### **Block-Repeat Registers**

BRC0, BRC1 Block-repeat counters 0 and 1

BRS1 BRC1 save register

RSA0, RSA1 Block-repeat start address registers 0 and 1 REA0, REA1 Block-repeat end address registers 0 and 1

#### Single-Repeat Registers

RPTC Single-repeat counter

CSR Computed single-repeat register

#### **Interrupt Registers**

IFR0, IFR1 Interrupt flag registers 0 and 1

IER0, IER1 Interrupt enable registers 0 and 1

DBIER0, DBIER1 Debug interrupt enable registers 0 and 1

**Status Registers**

ST0\_55-ST3\_55 Status registers 0, 1, 2, and 3

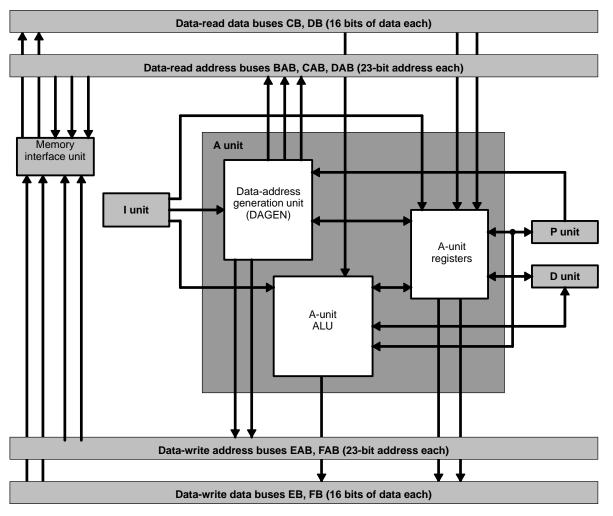

# 1.4 Address-Data Flow Unit (A Unit)

The A unit contains all the logic and registers necessary to generate the dataspace and I/O space addresses. It also contains an arithmetic logic unit (ALU) that can perform arithmetical, logical, shift, and saturation operations. Figure 1–4 shows a conceptual block diagram of the A unit. Sections 1.4.1 through 1.4.3 describe the main parts of the A unit.

Figure 1-4. Address-Data Flow Unit (A Unit) Diagram

### 1.4.1 Data-Address Generation Unit (DAGEN)

DAGEN generates all addresses for reads from or writes to data space and I/O space. In doing so, it can accept immediate values from the I unit and register values from the A unit. The P unit indicates to DAGEN whether to use linear or circular addressing for an instruction that uses an indirect addressing mode.

### 1.4.2 A-Unit Arithmetic Logic Unit (A-Unit ALU)

The A unit contains a 16-bit ALU that accepts immediate values from the I unit and communicates bidirectionally with memory, I/O space, the A-unit registers, the D-unit registers, and the P-unit registers. The A-unit ALU performs the following actions:

- Performs additions, subtractions, comparisons, Boolean logic operations, signed shifts, logical shifts, and absolute value calculations

- Tests, sets, clears, and complements A-unit register bits and memory bits

- Modifies and moves register values

- Rotates register values

- Moves certain results from the shifter to an A-unit register

# 1.4.3 A-Unit Registers

The A unit contains and uses the registers listed in the following table. All of these registers can accept immediate data from the I unit and can accept data from or provide data to the P-unit registers, the D-unit registers, and data memory. Within the A unit, the registers have bidirectional connections with DAGEN and the A-unit ALU.

#### **Data Page Registers**

DPH, DP Data page registers

PDP Peripheral data page register

**Pointers**

CDPH, CDP Coefficient data pointer registers

SPH, SP, SSP Stack pointer registers

XAR0–XAR7 Auxiliary registers

**Circular Buffer Registers**

BK03, BK47, BKC Circular buffer size registers

BSA01, BSA23, BSA45, BSA67, BSAC Circular buffer start address registers

**Temporary Registers**

T0–T3 Temporary registers 0, 1, 2, and 3

# 1.5 Data Computation Unit (D Unit)

The D unit contains the primary computational units of the CPU. Figure 1–5 shows a conceptual block diagram of the D unit. Sections 1.5.1 through 1.5.5 describe the main parts of the D unit.

Figure 1-5. Data Computation Unit (D Unit) Diagram

#### 1.5.1 Shifter

The D-unit shifter accepts immediate values from the I unit and communicates bidirectionally with memory, I/O space, the A-unit registers, the D-unit registers, and the P-unit registers. In addition, it supplies shifted values to the D-unit ALU (as an input for further calculation) and to the A-unit ALU (as a result to be stored in an A-unit register). The shifter performs the following actions:

- Shifts 40-bit accumulator values up to 31 bits to the left or up to 32 bits to the right. The shift count can be read from one of the temporary registers (T0–T3) or it can be supplied as a constant in the instruction.

- Shifts 16-bit register, memory, or I/O-space values up to 31 bits to the left or up to 32 bits to the right. The shift count can be read from one of the temporary registers (T0–T3) or it can be supplied as a constant in the instruction.

- Shifts 16-bit immediate values up to 15 bits to the left. You supply the shift count as a constant in the instruction.

- Rotates register values

- Rounds and/or saturates accumulator values before they are stored to data memory

- Performs additions and subtractions for some instructions that include shifting

For C54x DSP-compatible mode (C54CM=1), the overflow detection is only performed for the final operation of a calculation. For C55x-DSP-native mode (C54CM=0), the overflow detection is performed on each operation (shifting, rounding, and addition/subtraction).

# 1.5.2 D-Unit Arithmetic Logic Unit (D-Unit ALU)

The CPU contains a 40-bit ALU in the D unit that accepts immediate values from the I unit and communicates bidirectionally with memory, I/O space, the A-unit registers, the D-unit registers, and the P-unit registers. In addition, it receives results from the shifter. The D-unit ALU performs the following actions:

- Performs additions, subtractions, comparisons, rounding, saturation, Boolean logic operations, and absolute value calculations

- Performs two arithmetical operations simultaneously when a dual 16-bit arithmetic instruction is executed

- Tests, sets, clears, and complements D-unit register bits

- Moves register values

## 1.5.3 Two Multiply-and-Accumulate Units (MACs)

Two MACs support multiplication and addition/subtraction. In a single cycle each MAC can perform a 17-bit ×17-bit multiplication (fractional or integer) and a 40-bit addition or subtraction with optional 32-/40-bit saturation. The accumulators (which are D-unit registers) receive all the results of the MACs.

The MACs accept immediate values from the I unit; accept data values from memory, I/O space, and the A-unit registers; and communicate bidirectionally with the D-unit registers and the P-unit registers. Status register bits (in the P unit) are affected by MAC operations.

Overflow detection is only performed for the final operation of a calculation.

### 1.5.4 D-Unit Bit Manipulation Unit (D-Unit BIT)

In order to simplify D-Unit ALU, and D-Unit shifter modules, the D unit contains a small module that performs unique bit manipulation operations done by specific instructions listed in table Table 1–1.

- Normalizes accumulator values

- Extracts and expands bit fields, and performs bit counting

Table 1–1. Instructions Performed in D-Unit BIT Module

| Instructions Syntax             |                                         |

|---------------------------------|-----------------------------------------|

| DRx = exp(ACx)                  | Exponent of ACx register                |

| ACy = mant(ACx), DRx = exp(ACx) | Mantissa of the ACx register            |

| dst = field_expand(ACx, k16)    | Field bit manipulation                  |

| dst = field_extract(ACx, k16)   | Field bit manipulation                  |

| DRx = count(ACx, ACy, TCx)      | Bit field counting                      |

| TCx = bit(src, Baddr)           | Bit manipulation on the src that can be |

| bit(src, pair(Baddr))           | ACx register or ARx registers.          |

| cbit(src, Baddr)                | Baddr is the register bit address       |

| bit(src, Baddr) = #0            |                                         |

| bit(src, Baddr) = #1            |                                         |

## 1.5.5 D-Unit Registers

The D unit contains and uses the registers listed in the following table. All of these registers can accept immediate data from the I unit and can accept data from and provide data to the P-unit registers, the A-unit registers, and data memory. Within the D unit, the registers have bidirectional connections with the shifter, the D-unit ALU, and the MACs.

#### Accumulators

AC0-AC3 Accumulators 0, 1, 2, and 3

#### **Transition Registers**

TRN0, TRN1 Transition registers 0 and 1

### 1.6 Address Buses and Data Buses

The CPU is supported by one 32-bit program bus (PB), four 16-bit data buses (CB, DB, EB, FB), one 32-bit data bus (BB), one 24-bit address bus (PAB), and five 23-bit address buses (BAB, CAB, DAB, EAB, FAB). This parallel bus structure enables up to a 32-bit program read, four 16-bit data reads, and two 16-bit data writes per CPU clock cycle. Table 1–2 describes the functions of the 12 buses, and Table 1–3 shows which bus or buses are used for a given access type.

Table 1–2. Functions of the Address and Data Buses

| Bus(es)  | Width        | Function                                                                                                                                                                                                                                                                                                           |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAB      | 24 bits      | The program-read address bus (PAB) carries a 24-bit byte address for a read from program space.                                                                                                                                                                                                                    |

| РВ       | 32 bits      | The program-read data bus (PB) carries 4 bytes (32 bits) of program code from program memory to the CPU.                                                                                                                                                                                                           |

| CAB, DAB | 23 bits each | Each of these data-read address buses carries a 23-bit word address. DAB carries an address for a read from data space or I/O space. CAB carries a second address during dual data reads (see Table 1–3).                                                                                                          |

| CB, DB   | 16 bits each | Each of these data-read data buses carries a 16-bit data value to the CPU. DB carries a value from data space or from I/O-space. CB carries a second value during long data reads and dual data reads (see Table 1–3).                                                                                             |

| BAB      | 23 bits      | This data-read address bus carries a 23-bit word address for a coefficient read. Many instructions that use the coefficient indirect addressing mode use BAB to reference coefficient data values (and use BB to carry the data values).                                                                           |

| BB       | 32 bits      | This data-read data bus carries a 32-bit coefficient data value from internal memory to the CPU. BB is not connected to external memory. Data carried by BB is addressed using BAB.                                                                                                                                |

|          |              | Specific instructions use BB, CB, and DB to provide, in one cycle, three or four16-bit operands to the CPU, using the coefficient indirect addressing mode, or the double coefficient indirect addressing mode. The operand fetched via BB must be in a memory bank other than the bank(s) accessed via CB and DB. |

| EAB, FAB | 23 bits each | Each of these data-write address buses carries a 23-bit word address. EAB carries an address for a write to data space or I/O space. FAB carries a second address during dual data writes (see Table 1–3).                                                                                                         |

| EB, FB   | 16 bits each | Each of these data-write data buses carries a 16-bit data value from the CPU. EB carries a value to data space or to I/O-space. FB carries a second value during long data writes and dual data writes (see Table 1–3).                                                                                            |

### Note:

In the event of a dual data write to the same address, the result is undefined.

Table 1-3. Bus Usage By Access Type

| Access Type       | Address Bus(es) | Data Bus(es) | Description                                                                                                                                                                                                                                     |  |

|-------------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Instruction fetch | PAB             | РВ           | 32-bit read from program space                                                                                                                                                                                                                  |  |

| Single data read  | DAB             | DB           | 16-bit read from data memory                                                                                                                                                                                                                    |  |

| Single MMR read   | DAB             | DB           | 16-bit read from a memory-mapped register (MMR)                                                                                                                                                                                                 |  |

| Single I/O read   | DAB             | DB           | 16-bit read from I/O space                                                                                                                                                                                                                      |  |

| Single data write | EAB             | EB           | 16-bit write to data memory                                                                                                                                                                                                                     |  |

| Single MMR write  | EAB             | EB           | 16-bit write to a memory-mapped register (MMR)                                                                                                                                                                                                  |  |

| Single I/O write  | EAB             | EB           | 16-bit write to I/O space                                                                                                                                                                                                                       |  |

| Long data read    | DAB             | CB, DB       | 32-bit read from data memory                                                                                                                                                                                                                    |  |

| Long MMR read     | DAB             | CB, DB       | 32-bit read from one 32-bit MMR or two adjacent 16-bit MMRs                                                                                                                                                                                     |  |

| Long data write   | EAB             | EB, FB       | 32-bit write to data memory                                                                                                                                                                                                                     |  |

| Long MMR write    | EAB             | EB, FB       | 32-bit write to one 32-bit MMR or two adjacent 16-bit MMRs                                                                                                                                                                                      |  |

| Dual read         | CAB, DAB        | CB, DB       | Two simultaneous 16-bit reads from data space.                                                                                                                                                                                                  |  |

|                   |                 |              | <ul> <li>The first operand read uses DAB and DB. This read can be from data memory, from an MMR, or from I/O space.</li> <li>The second operand read uses CAB and CB. This read must be from data memory.</li> </ul>                            |  |

| Dual write        | EAB, FAB        | EB, FB       | Two simultaneous 16-bit writes:                                                                                                                                                                                                                 |  |

|                   |                 |              | <ul> <li>The first operand write uses uses FAB and FB.         This write must be to data memory.     </li> <li>The second operand write uses EAB and EB.         This write can be to data memory, to an MMR, or to I/O space.     </li> </ul> |  |

Table 1–3. Bus Usage By Access Type (Continued)

| Access Type                       | Address Bus(es) | Data Bus(es) | Description                                                                                                                                     |

|-----------------------------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Single data read                  | DAB, EAB        | DB, EB       | The following two operations happen in parallel:                                                                                                |

| Single data write                 |                 |              | <ul><li>Single data read: 16-bit read from data memory<br/>(uses DAB and DB)</li></ul>                                                          |

|                                   |                 |              | <ul><li>Single data write: 16-bit write to data memory<br/>(uses EAB and EB)</li></ul>                                                          |

| Long data read                    | DAB, EAB        | CB, DB, EB,  | The following two operations happen in parallel:                                                                                                |

| Long data write                   |                 | FB           | Long data read: 32-bit read from data memory (uses DAB, CB, and DB)                                                                             |

|                                   |                 |              | Long data write: 32-bit write to data memory (uses EAB, EB, and FB)                                                                             |

| Single data read                  | DAB, BAB        | DB, BB       | The following two operations happen in parallel:                                                                                                |

| Coefficient data<br>read          |                 |              | <ul><li>Single data read: 16-bit read from data space<br/>(uses DAB and DB)</li></ul>                                                           |

|                                   |                 |              | Coefficient data read: 16-bit read from <i>internal</i> memory using the coefficient indirect addressing mode (uses BAB and BB)                 |

| Single data read                  | DAB, BAB        | DB, BB       | The following two operations happen in parallel:                                                                                                |

| Double coeffi-<br>cient data read |                 |              | <ul><li>Single data read: 16-bit read from data space<br/>(uses DAB and DB)</li></ul>                                                           |

|                                   |                 |              | Double coefficient data read: 32-bit read from<br>internal memory using the double coefficient<br>indirect addressing mode (uses BAB and BB)    |

| Dual data read                    | CAB, DAB, BAB   | CB, DB, BB   | The following two operations happen in parallel:                                                                                                |

| Coefficient data read             |                 |              | Dual data read: Two simultaneous 16-bit reads from data space. The first operand read uses DAB and DB. The second operand read uses CAB and CB. |

|                                   |                 |              | Coefficient data read: 16-bit read from internal<br>memory using the coefficient indirect address-<br>ing mode (uses BAB and BB)                |

Table 1–3. Bus Usage By Access Type (Continued)

| Access Type                       | Address Bus(es) | Data Bus(es) | Description                                                                                                                                     |

|-----------------------------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Dual data read                    | CAB, DAB, BAB   | CB, DB, BB   | The following two operations happen in parallel:                                                                                                |

| Double coeffi-<br>cient data read |                 |              | Dual data read: Two simultaneous 16-bit reads from data space. The first operand read uses DAB and DB. The second operand read uses CAB and CB. |

|                                   |                 |              | Double coefficient data read: 32-bit read from<br>internal memory using the double coefficient in-<br>direct addressing mode (uses BAB and BB)  |

# 1.7 Instruction Pipeline

The C55x DSP CPU uses instruction pipelining. Section 1.7.1 introduces the pipeline, and section 1.7.2 describes how the CPU prevents conflicts that might otherwise occur in the pipeline.

### 1.7.1 Pipeline Phases

The C55x DSP instruction pipeline is a protected pipeline that has two decoupled segments:

- The first segment, referred to as the *fetch pipeline*, fetches 32-bit instruction packets from memory, places them in the instruction buffer queue (IBQ), and then feeds the second pipeline segment with 64-bit instruction packets. The fetch pipeline is illustrated in Figure 1–6.

- The second segment, referred to as the *execution pipeline*, decodes instructions and performs data accesses and computations. The execution pipeline is illustrated in Figure 1–7. Table 1–4 provides examples to help you understand the activity in the key phases of the execution pipeline.

Figure 1–6. First Segment of the Pipeline (Fetch Pipeline)

|            | ——— Tir    | ne —  |           |

|------------|------------|-------|-----------|

| Prefetch 1 | Prefetch 2 | Fetch | Predecode |

| (PF1)      | (PF2)      | (F)   | (PD)      |

| Pipeline<br>Phase | Description                                                                                                     |

|-------------------|-----------------------------------------------------------------------------------------------------------------|

| PF1               | Present program address to memory.                                                                              |

| PF2               | Wait for memory to respond.                                                                                     |

| F                 | Fetch an instruction packet from memory and place it in the IBQ.                                                |

| PD                | Pre-decode instructions in the IBQ (identify where instructions begin and end; identify parallel instructions). |

Figure 1–7. Second Segment of the Pipeline (Execution Pipeline)

|                                        |                 |                   | ——— Tin           | ne ———      |                |              | <b></b>        |

|----------------------------------------|-----------------|-------------------|-------------------|-------------|----------------|--------------|----------------|

| Decode<br>(D)                          | Address<br>(AD) | Access 1<br>(AC1) | Access 2<br>(AC2) | Read<br>(R) | Execute<br>(X) | Write<br>(W) | Write+<br>(W+) |

| Note: Only for memory write operations |                 |                   |                   |             |                |              |                |

| Pipeline<br>Phase | Description                                                                                                                                                                                                                                                                          |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D                 | Read six bytes from the instruction buffer queue.                                                                                                                                                                                                                                    |  |  |

|                   | Decode an instruction pair or a single instruction.                                                                                                                                                                                                                                  |  |  |

|                   | Dispatch instructions to the appropriate CPU functional units.                                                                                                                                                                                                                       |  |  |

|                   | Read STx_55 bits associated with data address generation:  ST1_55(CPL) ST2_55(ARnLC)  ST2_55(ARMS) ST2_55(CDPLC)                                                                                                                                                                     |  |  |

| AD                | Read/modify registers involved in data address generation. For example:  - ARx and T0 in *ARx+(T0)  - BK03 if AR2LC = 1  - SP during pushes and pops  - SSP, same as for SP if in the 32-bit stack mode                                                                              |  |  |

|                   | <ul> <li>Perform operations that use the A-unit ALU. For example:         <ul> <li>Arithmetic using AADD instruction</li> <li>Swapping A-unit registers with a SWAP instruction</li> <li>Writing constants to A-unit registers (BKxx, BSAxx, BRCx, CSR, etc.)</li> </ul> </li> </ul> |  |  |

|                   | Decrement ARx for the conditional branch instruction that branches on ARx not zero.                                                                                                                                                                                                  |  |  |

|                   | (Exception) Evaluate the condition of the XCC instruction (execute(AD-unit) attribute in the algebraic syntax).                                                                                                                                                                      |  |  |

| AC1               | For memory read operations, send addresses on the appropriate CPU address buses.                                                                                                                                                                                                     |  |  |

| AC2               | Allow one cycle for memories to respond to read requests.                                                                                                                                                                                                                            |  |  |

| R                 | Read data from memory and MMR-addressed registers.                                                                                                                                                                                                                                   |  |  |

|                   | Read A-unit registers when executing specific D-unit instructions that "prefetch" A-unit registers in the R phase rather than reading them in the X phase.                                                                                                                           |  |  |

|                   | Evaluate the conditions of conditional instructions. Most but not all condition evaluation is performed in the R phase. Exceptions are marked with "(Exception)" in this table.                                                                                                      |  |  |

Figure 1–7. Second Segment of the Pipeline (Execution Pipeline) (Continued)

| Pipeline<br>Phase | Description                                                                                                                                                                                                                            |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Х                 | Read/modify registers that are not MMR-addressed.                                                                                                                                                                                      |

|                   | Read/modify individual register bits.                                                                                                                                                                                                  |

|                   | Set conditions.                                                                                                                                                                                                                        |

|                   | (Exception) Evaluate the condition of the XCCPART instruction (execute(D-unit) attribute in the algebraic syntax), unless the instruction is conditioning a write to memory (in this case, the condition is evaluated in the R phase). |

|                   | (Exception) Evaluate the condition of the RPTCC instruction.                                                                                                                                                                           |

| W                 | Write data to MMR-addressed registers or to I/O space<br>(peripheral registers).                                                                                                                                                       |

|                   | Write data to memory. From the perspective of the CPU, the write operation is finished in this pipeline phase.                                                                                                                         |

| W+                | Write data to memory. From the perspective of the memory, the<br>write operation is finished in this pipeline phase.                                                                                                                   |

Table 1-4. Examples to Illustrate Execution Pipeline Activity

| Example Syntax    | Pipeline Explanation                                                                   |

|-------------------|----------------------------------------------------------------------------------------|

| AMOV #k23, XARx   | XARx is initialized with a constant in the AD phase.                                   |

| MOV #k, ARx       | ARx is not MMR-addressed. ARx is initialized with a constant in the X phase.           |

| MOV #k, mmap(ARx) | ARx is MMR-addressed. ARx is initialized with a constant in the W phase.               |

| AADD #k, ARx      | With this special instruction, ARx is initialized with a constant in the AD phase.     |

| MOV #k, *ARx+     | The memory write happens in the W+ phase.                                              |

| MOV *ARx+, AC0    | ARx is read and updated in the AD phase. AC0 is loaded in the X phase.                 |

| ADD #k, ARx       | ARx is read at the beginning of the X phase and is modified at the end of the X phase. |

| ADD ACy, ACx      | ACx and ACy read and write activity occurs in the X phase.                             |

Table 1–4. Examples to Illustrate Execution Pipeline Activity (Continued)

| Example Syntax                             | Pipeline Explanation                                                                                                                                      |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV mmap(ARx), ACx                         | ARx is MMR-addressed and so is read in the R phase. ACx is modified in the X phase.                                                                       |

| MOV ARx, ACx                               | ARx is not MMR-addressed and so is read in the X phase. ACx is modified in the X phase.                                                                   |

| BSET CPL                                   | The CPL bit is set in the X phase.                                                                                                                        |

| PUSH, POP, RET or<br>AADD #K8, SP          | SP is read and modified in the AD phase. SSP is also affected if the 32-bit stack mode is selected.                                                       |

| XCCPART overflow(ACx)<br>   MOV *AR1+, AC1 | The condition is evaluated in the X phase.<br>Note: AR1 is incremented regardless of whether<br>the condition is true.                                    |

| XCCPART overflow(ACx)<br>   MOV AC1, *AR1+ | The condition is evaluated in the R phase because it conditions a write to memory.  Note: AR1 is incremented regardless of whether the condition is true. |

| XCC overflow(ACx)<br>   MOV *AR1+, AC1     | The condition is evaluated in the AD phase.<br>Note: AR1 is incremented only if the condition is true.                                                    |

## 1.7.2 Pipeline Protection

Multiple instructions are executed simultaneously in the pipeline, and different instructions perform modifications to memory, I/O-space, and register values during different phases of completion. In an unprotected pipeline, this could lead to pipeline conflicts—reads and writes at the same location happening out of the intended order. However, the C55x DSP pipeline has a mechanism that automatically protects against pipeline conflicts. The pipeline-protection mechanism adds inactive cycles between instructions that would cause conflicts.

Most pipeline-protection cycles are inserted based on two rules:

- If an instruction is supposed to write to a location but a previous instruction has not yet read from that location, extra cycles are inserted so that the read occurs first.

- If an instruction is supposed to read from a location but a previous instruction has not yet written to that location, extra cycles are inserted so that the write occurs first.

## Note:

The pipeline-protection mechanism cannot prevent pipeline conflicts between two instructions that are executed in parallel.

## Chapter 2

# **CPU Registers**

This chapter describes the main registers in the C55x<sup>™</sup> DSP CPU. Section 2.1 lists the registers in alphabetical order, and section 2.2 shows the addresses for the memory-mapped registers. The other sections contain additional details about the CPU registers.

| Topi | c Page                                                  | • |

|------|---------------------------------------------------------|---|

| 2.1  | Alphabetical Summary of Registers                       |   |

| 2.2  | Memory-Mapped Registers 2-4                             | Ļ |

| 2.3  | Accumulators (AC0-AC3)                                  | ) |