# TMS320C5515/14/05/04 DSP External Memory Interface (EMIF)

# **User's Guide**

Literature Number: SPRUGU6 March 2010

# **Contents**

|     | rnal N/- | mony Interface (EMIE)                                               |

|-----|----------|---------------------------------------------------------------------|

|     |          | mory Interface (EMIF)                                               |

| 1.1 |          |                                                                     |

|     | 1.1.1    | Purpose of the External Memory Interface                            |

|     |          | Features                                                            |

|     |          | Functional Block Diagram                                            |

| 1.2 |          | ecture                                                              |

|     | 1.2.1    | Clock Control                                                       |

|     | 1.2.2    | EMIF Requests                                                       |

|     | 1.2.3    | Memory Map                                                          |

|     | 1.2.4    | Signal Descriptions                                                 |

|     | 1.2.5    | Pin Multiplexing                                                    |

|     | 1.2.6    | SDRAM Controller and Interface                                      |

|     | 1.2.7    | Asynchronous Controller and Interface                               |

|     | 1.2.8    | BYTEMODE Bits of The EMIF System Control Register                   |

|     | 1.2.9    | Data Bus Parking                                                    |

|     | 1.2.10   | • • • • • • • • • • • • • • • • • • • •                             |

|     | 1.2.11   | -,                                                                  |

|     | 1.2.12   |                                                                     |

|     | 1.2.13   |                                                                     |

|     | 1.2.14   |                                                                     |

|     | 1.2.15   |                                                                     |

|     | 1.2.16   | Power Management                                                    |

|     | 1.2.17   | Emulation Considerations                                            |

|     |          | CPU Instruction Pipeline Considerations                             |

| 1.3 | Interfa  | cing the EMIF to Mobile SDRAM                                       |

|     | 1.3.1    | Hardware Interface                                                  |

|     | 1.3.2    | SW Configuration                                                    |

| 1.4 | Regist   | ers                                                                 |

|     | 1.4.1    | Revision Register (REV)                                             |

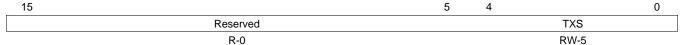

|     | 1.4.2    | Status Register (STATUS)                                            |

|     | 1.4.3    | Asynchronous Wait Cycle Configuration Registers (AWCCR1 and AWCCR2) |

|     | 1.4.4    | SDRAM Configuration Registers (SDCR1 and SDCR2)                     |

|     | 1.4.5    | SDRAM Refresh Control Register (SDRCR)                              |

|     | 1.4.6    | Asynchronous Configuration Registers (ACSnCR1 and ACSnCR2)          |

|     | 1.4.7    | SDRAM Timing Registers (SDTIMR1 and SDTIMR2)                        |

|     | 1.4.8    | SDRAM Self Refresh Exit Timing Register (SDSRETR)                   |

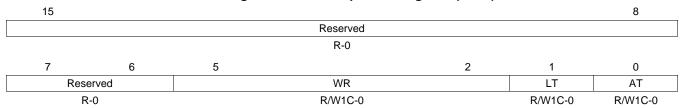

|     | 1.4.9    | Interrupt Raw Register (EIRR)                                       |

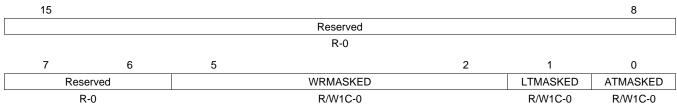

|     | 1.4.10   | Interrupt Mask Register (EIMR)                                      |

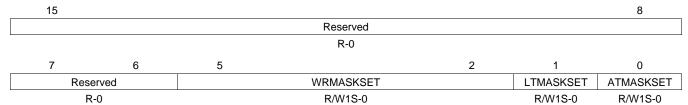

|     | 1.4.11   | Interrupt Mask Set Register (EIMSR)                                 |

|     | 1.4.12   |                                                                     |

|     | 1.4.13   |                                                                     |

|     | 1.4.14   | ,                                                                   |

|     |          |                                                                     |

|     | 1.4.15   | Page Mode Control Registers (PAGEMODCTRL1) and (PAGEMODCTRL2)       |

| 1.4.17 | NAND Flash 4-Bit ECC Load Register (NAND4BITECCLOAD)        | 82 |

|--------|-------------------------------------------------------------|----|

| 1.4.18 | NAND Flash 4-Bit ECC Register 1 (NAND4BITECC1)              | 82 |

| 1.4.19 | NAND Flash 4-Bit ECC Register 2 (NAND4BITECC2)              | 82 |

| 1.4.20 | NAND Flash 4-Bit ECC Register 3 (NAND4BITECC3)              | 82 |

| 1.4.21 | NAND Flash 4-Bit ECC Register 4 (NAND4BITECC4)              | 83 |

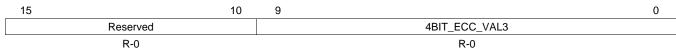

| 1.4.22 | NAND Flash 4-Bit ECC Register 5 (NAND4BITECC5)              | 84 |

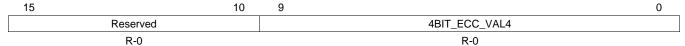

| 1.4.23 | NAND Flash 4-Bit ECC Register 6 (NAND4BITECC6)              | 84 |

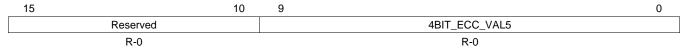

| 1.4.24 | NAND Flash 4-Bit ECC Register 7 (NAND4BITECC7)              | 84 |

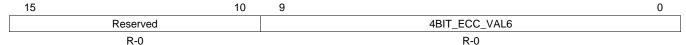

| 1.4.25 | NAND Flash 4-Bit ECC Register 8 (NAND4BITECC8)              | 84 |

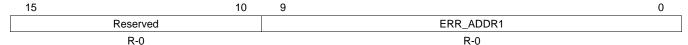

| 1.4.26 | NAND Flash 4-Bit ECC Error Address Register 1 (NANDERRADD1) | 85 |

| 1.4.27 | NAND Flash 4-Bit ECC Error Address Register 2 (NANDERRADD2) | 86 |

| 1.4.28 | NAND Flash 4-Bit ECC Error Address Register 3 (NANDERRADD3) | 86 |

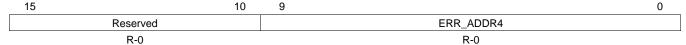

| 1.4.29 | NAND Flash 4-Bit ECC Error Address Register 4 (NANDERRADD4) | 86 |

| 1.4.30 | NAND Flash 4-Bit ECC Error Value Register 1 (NANDERRVAL1)   | 86 |

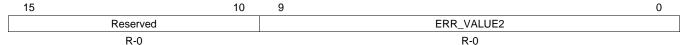

| 1.4.31 | NAND Flash 4-Bit ECC Error Value Register 2 (NANDERRVAL2)   | 87 |

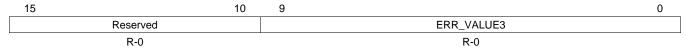

| 1.4.32 | NAND Flash 4-Bit ECC Error Value Register 3 (NANDERRVAL3)   | 88 |

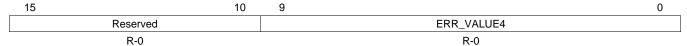

| 1.4.33 | NAND Flash 4-Bit ECC Error Value Register 4 (NANDERRVAL4)   | 88 |

|        |                                                             |    |

# **List of Figures**

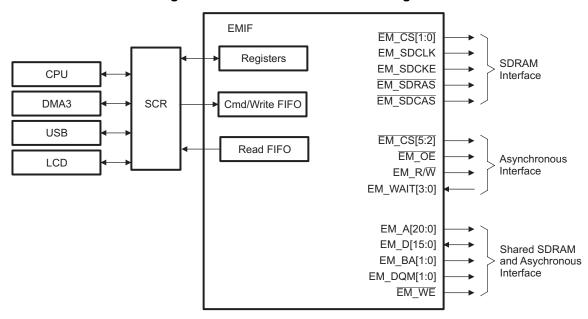

| 1-1.  | EMIF Functional Block Diagram                                        | 14 |

|-------|----------------------------------------------------------------------|----|

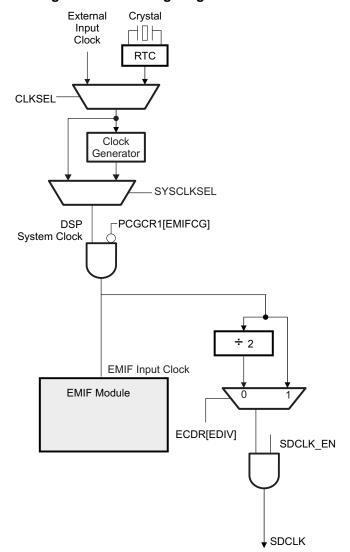

| 1-2.  | Clocking Diagram for the EMIF                                        | 15 |

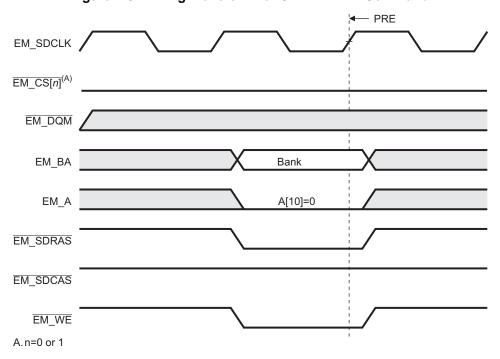

| 1-3.  | Timing Waveform for SDRAM PRE Command                                | 19 |

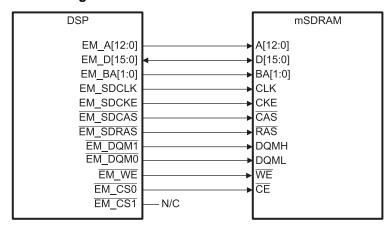

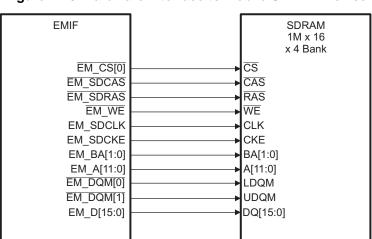

| 1-4.  | EMIF to mSDRAM Connection                                            | 20 |

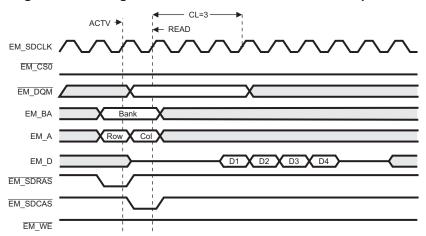

| 1-5.  | Timing Waveform for Basic SDRAM Read Operation                       | 26 |

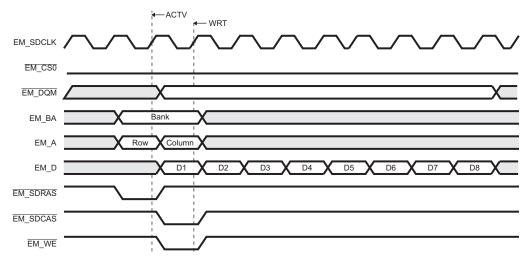

| 1-6.  | Timing Waveform for Basic SDRAM Write Operation                      | 27 |

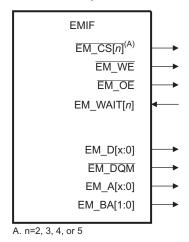

| 1-7.  | EMIF Asynchronous Interface                                          | 31 |

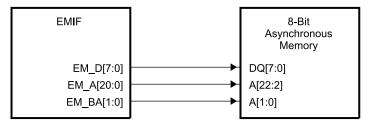

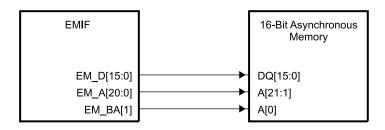

| 1-8.  | Connecting Data and Address Bus to Asynchronous Memory Devices       | 32 |

| 1-9.  | Common Asynchronous Interface                                        | 32 |

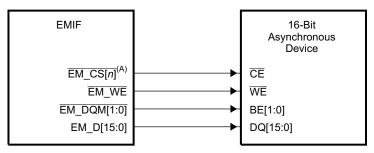

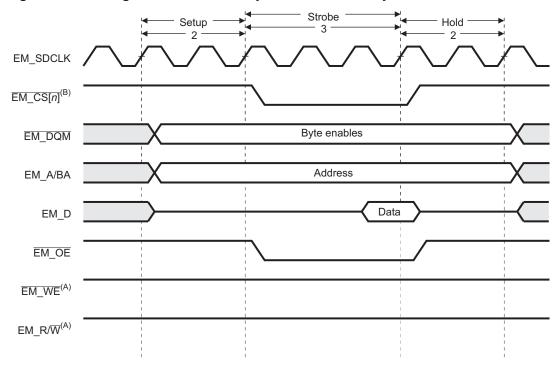

| 1-10. | Timing Waveform of an Asynchronous Read Cycle in Normal Mode         | 36 |

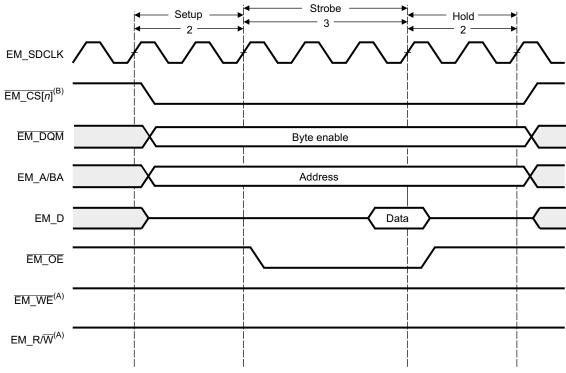

| 1-11. | Timing Waveform of an Asynchronous Write Cycle in Normal Mode        | 38 |

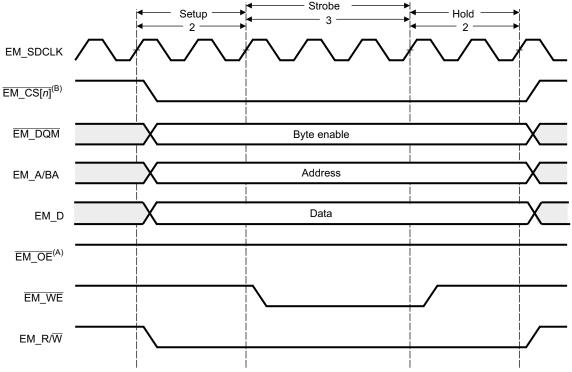

| 1-12. | Timing Waveform of an Asynchronous Read Cycle in Select Strobe Mode  | 40 |

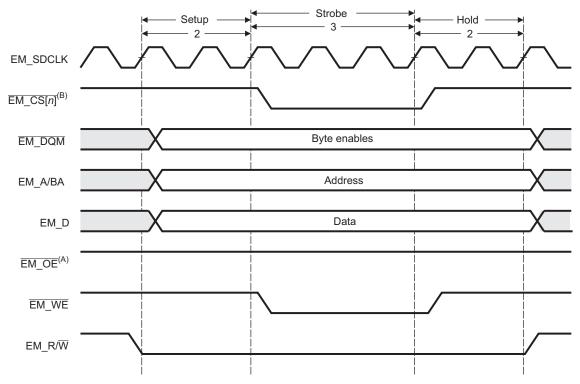

| 1-13. | Timing Waveform of an Asynchronous Write Cycle in Select Strobe Mode | 41 |

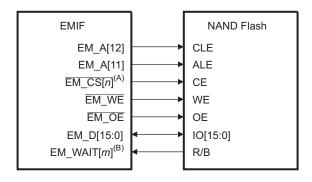

| 1-14. | EMIF to NAND Flash Interface                                         | 43 |

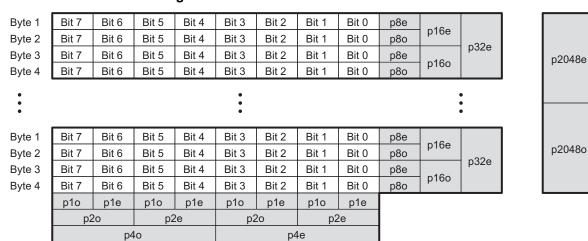

| 1-15. | ECC Value for 8-Bit NAND Flash                                       | 45 |

| 1-16. | Hardware Interface to Mobile SDRAM Device                            | 54 |

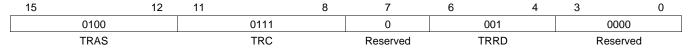

| 1-17. | SDTIMR1 Contents                                                     | 55 |

| 1-18. | SDTIMR2 Contents                                                     | 55 |

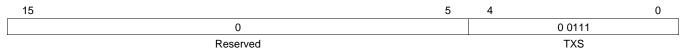

| 1-19. | SDRETR Contents                                                      | 55 |

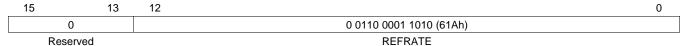

| 1-20. | SDRCR Contents                                                       | 56 |

| 1-21. | SDCR1 Contents                                                       | 56 |

| 1-22. | SDCR2 Contents                                                       | 57 |

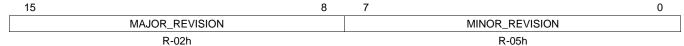

| 1-23. | Revision Register (REV)                                              | 60 |

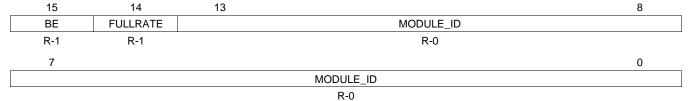

| 1-24. | Status Register (STATUS)                                             | 60 |

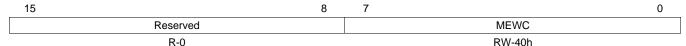

| 1-25. | Asynchronous Wait Cycle Configuration Register 1 (AWCCR1)            | 61 |

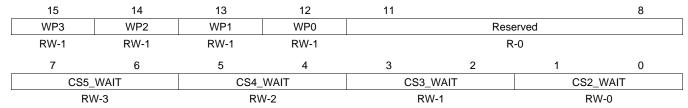

| 1-26. | Asynchronous Wait Cycle Configuration Register 2 (AWCCR2)            | 61 |

| 1-27. | SDRAM Configuration Register 1 (SDCR1)                               | 63 |

| 1-28. | SDRAM Configuration Register 2 (SDCR2)                               | 63 |

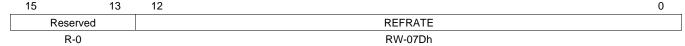

| 1-29. | SDRAM Refresh Control Register (SDRCR)                               | 66 |

| 1-30. | Asynchronous CS2 Configuration Register 1 (ACS2CR1)                  | 66 |

| 1-31. | Asynchronous CS2 Configuration Register 2 (ACS2CR2)                  | 66 |

| 1-32. | Asynchronous CS3 Configuration Register 1 (ACS3CR1)                  | 66 |

| 1-33. | Asynchronous CS3 Configuration Register 2 (ACS3CR2)                  | 67 |

| 1-34. | Asynchronous CS4 Configuration Register 1 (ACS4CR1)                  | 67 |

| 1-35. | Asynchronous CS4 Configuration Register 2 (ACS4CR2)                  | 67 |

| 1-36. | Asynchronous CS5 Configuration Register 1 (ACS5CR1)                  |    |

| 1-37. | Asynchronous CS5 Configuration Register 2 (ACS5CR2)                  | 67 |

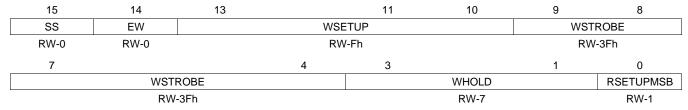

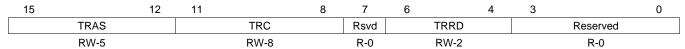

| 1-38. | SDRAM Timing Register 1 (SDTIMR1)                                    | 69 |

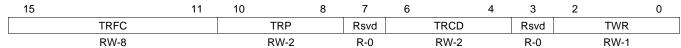

| 1-39. | SDRAM Timing Register 1 (SDTIMR2)                                    | 69 |

| 1-40. | ,                                                                    | 70 |

| 1-41. |                                                                      | 71 |

| 1-42. | Interrupt Mask Register (EIMR)                                       | 72 |

| 1-43. | Interrupt Mask Set Register (EIMSR)                                  | 73 |

| 1-44. | Interrupt Mask Clear Register (EIMCR)                                | 74 |

| 1-45. |                                                                      | 74 |

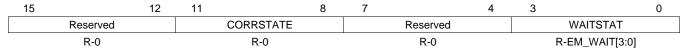

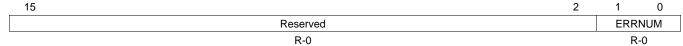

| 1-46. | NAND Flash Status Register 1 (NANDFSR1)                              | 76 |

| 1-47. | NAND Flash Status Register 2 (NANDFSR2)                              | 76 |

| 1-48. | Page Mode Control Register 1 (PAGEMODCTRL1)                 | 78 |

|-------|-------------------------------------------------------------|----|

| 1-49. | Page Mode Control Register 2 (PAGEMODCTRL2)                 | 78 |

| 1-50. | NAND Flash CSn 1-Bit ECC Register 1 (NCSnECC1)              | 80 |

| 1-51. | NAND Flash CSn 1-Bit ECC Register 2 (NCSnECC2)              | 80 |

| 1-52. | NAND Flash 4-Bit ECC Load Register (NAND4BITECCLOAD)        | 82 |

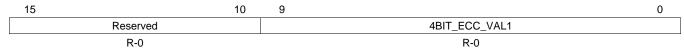

| 1-53. | NAND Flash 4-Bit ECC Load Register 1 (NAND4BITECC1)         | 82 |

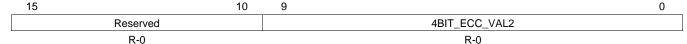

| 1-54. | NAND Flash 4-Bit ECC Register 2 (NAND4BITECC2)              | 82 |

| 1-55. | NAND Flash 4-Bit ECC Register 3 (NAND4BITECC3)              | 83 |

| 1-56. | NAND Flash 4-Bit ECC Register 4 (NAND4BITECC4)              | 83 |

| 1-57. | NAND Flash 4-Bit ECC Register 5 (NAND4BITECC5)              | 84 |

| 1-58. | NAND Flash 4-Bit ECC Register 6 (NAND4BITECC6)              | 84 |

| 1-59. | NAND Flash 4-Bit ECC Register 7 (NAND4BITECC7)              | 84 |

| 1-60. | NAND Flash 4-Bit ECC Register 8 (NAND4BITECC8)              | 85 |

| 1-61. | NAND Flash 4-Bit ECC Error Address Register 1 (NANDERRADD1) | 85 |

| 1-62. | NAND Flash 4-Bit ECC Error Address Register 2 (NANDERRADD2) | 86 |

| 1-63. | NAND Flash 4-Bit ECC Error Address Register 3 (NANDERRADD3) | 86 |

| 1-64. | NAND Flash 4-Bit ECC Error Address Register 4 (NANDERRADD4) | 86 |

| 1-65. | NAND Flash 4-Bit ECC Error Value Register 1 (NANDERRVAL1)   | 87 |

| 1-66. | NAND Flash 4-Bit ECC Error Value Register 2 (NANDERRVAL2)   | 87 |

| 1-67. | NAND Flash 4-Bit ECC Error Value Register 3 (NANDERRVAL3)   | 88 |

| 1-68  | NAND Flash 4-Bit FCC Fror Value Register 4 (NANDERRVAL4)    | 88 |

## **List of Tables**

| 1-1.  | EMIF Memory Map                                                                                 | 16 |

|-------|-------------------------------------------------------------------------------------------------|----|

| 1-2.  | EMIF Pins Used to Access Both SDRAM and Asynchronous Devices                                    | 16 |

| 1-3.  | EMIF Pins Specific to SDRAM                                                                     | 17 |

| 1-4.  | EMIF Pins Specific to Asynchronous Devices                                                      | 17 |

| 1-5.  | EMIF SDRAM Commands                                                                             | 18 |

| 1-6.  | Truth Table for SDRAM Commands                                                                  | 19 |

| 1-7.  | Description of Bit Fields in SDRAM Configuration Registers (SDCR1 and SDCR2)                    | 20 |

| 1-8.  | Description of Bit Fields in SDRAM Refresh Control Register (SDRCR)                             | 21 |

| 1-9.  | Description of Bit Fields in SDRAM Timing Registers (SDTIMR1 and SDTIMR2)                       | 21 |

| 1-10. | Description of Bit Fields in SDRAM Self Refresh Exit Timing Register (SDSRETR)                  | 21 |

| 1-11. | Extended Mode Register Settings During Auto-Init Sequence                                       | 21 |

| 1-12. | Mode Register Settings During Auto-Init Sequence                                                |    |

| 1-13. | Refresh Urgency Levels                                                                          | 23 |

| 1-14. | Mapping of Logical Address to SDRAM Address (IBANK_POS = 0)                                     | 28 |

| 1-15. | Mapping of Logical Address to SDRAM Address (IBANK_POS = 1)                                     | 29 |

| 1-16. | Normal Mode vs. Select Strobe Mode                                                              | 31 |

| 1-17. | Description of the Asynchronous CSn Configuration Registers (ACSnCR1 and ACSnCR2)               | 33 |

| 1-18. | Description of the Asynchronous Wait Cycle Configuration Registers (AWCCR1 and AWCCR2)          | 34 |

| 1-19. | Description of the EMIF Interrupt Mask Set Register (EIMSR)                                     | 34 |

| 1-20. | Description of the EMIF Interrupt Mask Clear Register (EIMCR)                                   | 34 |

| 1-21. | Asynchronous Read Operation in Normal Mode                                                      | 35 |

| 1-22. | Asynchronous Write Operation in Normal Mode                                                     | 36 |

| 1-23. | Asynchronous Read Operation in Select Strobe Mode                                               | 39 |

| 1-24. | Asynchronous Write Operation in Select Strobe Mode                                              | 40 |

| 1-25. | Description of the NAND Flash Control Register (NANDFCR)                                        | 42 |

| 1-26. | CPU and DMA Address to EMIF Address Pin Mapping                                                 | 43 |

| 1-27. | Effect of BYTEMODE Bits on EMIF Accesses                                                        | 48 |

| 1-28. | Interrupt Monitor and Control Bit Fields                                                        | 52 |

| 1-29. | Partial Pipeline Diagram of Consecutive Instructions That Write and Read at Different Addresses | 53 |

| 1-30. | NOP Instructions Inserted in the Code of Figure 1–3 to Make the Write Occur Before the Read     | 53 |

| 1-31. | SDTIMR1 and SDTIMR2 Field Calculations                                                          | 55 |

| 1-32. | SDSRETR Field Calculations                                                                      | 55 |

| 1-33. | SDRCR Field Calculations                                                                        | 56 |

| 1-34. | SDCR1 and SDCR2 Field Calculations                                                              | 56 |

| 1-35. | EMIF Register Values for Micron MT48H4M16LF-8 Mobile SDRAM Device                               | 57 |

| 1-36. | EMIF Registers                                                                                  | 58 |

| 1-37. | EMIF System Registers                                                                           | 59 |

| 1-38. | Revision Register (REV) Field Descriptions                                                      | 60 |

| 1-39. | Status Register (STATUS) Field Descriptions                                                     | 60 |

| 1-40. | Asynchronous Wait Cycle Configuration Register 1 (AWCCR1) Field Descriptions                    |    |

| 1-41. | Asynchronous Wait Cycle Configuration Register 2 (AWCCR2) Field Descriptions                    |    |

| 1-42. | SDRAM Configuration Register 1 (SDCR1) Field Descriptions                                       | 63 |

| 1-43. | SDRAM Configuration Register 2 (SDCR2) Field Descriptions                                       | 64 |

| 1-44. | SDRAM Refresh Control Register (SDRCR) Field Descriptions                                       |    |

| 1-45. | Asynchronous CSn Configuration Register 1 (ACSnCR1) Field Descriptions                          |    |

| 1-46. | Asynchronous CSn Configuration Register 2 (ACSnCR2) Field Descriptions                          |    |

| 1-47. | SDRAM Timing Register 1 (SDTIMR1) Field Descriptions                                            | 69 |

| 1-48. | SDRAM Timing Register 1 (SDTIMR2) Field Descriptions                           | 69         |

|-------|--------------------------------------------------------------------------------|------------|

| 1-49. | SDRAM Self Refresh Exit Timing Register (SDSRETR) Field Descriptions           | 70         |

| 1-50. | Interrupt Raw Register (EIRR) Field Descriptions                               | 71         |

| 1-51. | Interrupt Mask Register (EIMR) Field Descriptions                              | 72         |

| 1-52. | Interrupt Mask Set Register (EIMSR) Field Descriptions                         | 73         |

| 1-53. | Interrupt Mask Clear Register (EIMCR) Field Descriptions                       | 74         |

| 1-54. | NAND Flash Control Register (NANDFCR) Field Descriptions                       | 74         |

| 1-55. | NAND Flash Status Register 1 (NANDFSR1) Field Descriptions                     | 76         |

| 1-56. | NAND Flash Status Register 2 (NANDFSR2) Field Descriptions                     | 77         |

| 1-57. | Page Mode Control Register 1 (PAGEMODCTRL1) Field Descriptions                 | 78         |

| 1-58. | Page Mode Control Register 2 (PAGEMODCTRL2) Field Descriptions                 | <b>7</b> 9 |

| 1-59. | NAND Flash CSn 1-Bit ECC Register 1 (NCSnECC1) Field Descriptions              | 80         |

| 1-60. | NAND Flash CSn 1-Bit ECC Register 2 (NCSnECC2) Field Descriptions              | 81         |

| 1-61. | NAND Flash 4-Bit ECC Load Register (NAND4BITECCLOAD) Field Descriptions        | 82         |

| 1-62. | NAND Flash 4-Bit ECC Load Register 1 (NAND4BITECC1) Field Descriptions         | 82         |

| 1-63. | NAND Flash 4-Bit ECC Register 2 (NAND4BITECC2) Field Descriptions              | 82         |

| 1-64. | NAND Flash 4-Bit ECC Register 3 (NAND4BITECC3) Field Descriptions              | 83         |

| 1-65. | NAND Flash 4-Bit ECC Register 4 (NAND4BITECC4) Field Descriptions              | 83         |

| 1-66. | NAND Flash 4-Bit ECC Register 5 (NAND4BITECC5) Field Descriptions              | 84         |

| 1-67. | NAND Flash 4-Bit ECC Register 6 (NAND4BITECC6) Field Descriptions              | 84         |

| 1-68. | NAND Flash 4-Bit ECC Register 7 (NAND4BITECC7) Field Descriptions              | 84         |

| 1-69. | NAND Flash 4-Bit ECC Register 8 (NAND4BITECC8) Field Descriptions              | 85         |

| 1-70. | NAND Flash 4-Bit ECC Error Address Register 1 (NANDERRADD1) Field Descriptions | 85         |

| 1-71. | NAND Flash 4-Bit ECC Error Address Register 2 (NANDERRADD2) Field Descriptions | 86         |

| 1-72. | NAND Flash 4-Bit ECC Error Address Register 3 (NANDERRADD3) Field Descriptions | 86         |

| 1-73. | NAND Flash 4-Bit ECC Error Address Register 4 (NANDERRADD4) Field Descriptions | 86         |

| 1-74. | NAND Flash 4-Bit ECC Error Value Register 1 (NANDERRVAL1) Field Descriptions   | 87         |

| 1-75. | NAND Flash 4-Bit ECC Error Value Register 2 (NANDERRVAL2) Field Descriptions   | 87         |

| 1-76. | NAND Flash 4-Bit ECC Error Value Register 3 (NANDERRVAL3) Field Descriptions   | 88         |

| 1-77  | NAND Flash 4-Bit FCC Fror Value Register 4 (NANDERRVAL4) Field Descriptions    | 88         |

### Read This First

#### **About This Manual**

This document describes the operation of the external memory interface (EMIF). The purpose of the EMIF is to provide a means to connect to a variety of external asynchronous devices including NOR Flash, NAND Flash, and SRAM.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320C5515/14/05/04 Digital Signal Processor (DSP) Digital Signal Processor (DSP). Copies of these documents are available on the internet at <a href="http://www.ti.com">http://www.ti.com</a>.

- <u>SWPU073</u> TMS320C55x 3.0 CPU Reference Guide. This manual describes the architecture, registers, and operation of the fixed-point TMS320C55x digital signal processor (DSP) CPU.

- <u>SPRU652</u> TMS320C55x DSP CPU Programmer's Reference Supplement. This document describes functional exceptions to the CPU behavior.

- SPRUFO1A TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Inter-Integrated Circuit (I2C) Peripheral User's Guide. This document describes the inter-integrated circuit (I2C) peripheral in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The I2C peripheral provides an interface between the device and other devices compliant with Phillips Semiconductors Inter-IC bus (I2C-bus) specification version 2.1 and connected by way of an I2C-bus. This document assumes the reader is familiar with the I2C-bus specification.

- SPRUFO2 TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Timer/Watchdog Timer User's Guide. This document provides an overview of the three 32-bit timers in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The 32-bit timers of the device are software programmable timers that can be configured as general-purpose (GP) timers. Timer 2 can be configured as a GP, a Watchdog (WD), or both simultaneously.

- SPRUFO3 TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Serial Peripheral Interface (SPI) User's Guide. This document describes the serial peripheral interface (SPI) in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The SPI is a high-speed synchronous serial input/output port that allows a serial bit stream of programmed length (1 to 32 bits) to be shifted into and out of the device at a programmed bit-transfer rate. The SPI supports multi-chip operation of up to four SPI slave devices. The SPI can operate as a master device only.

- SPRUFO4 TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) General-Purpose Input/Output (GPIO) User's Guide. This document describes the general-purpose input/output (GPIO) on the TMS320C5515/14/05/04/VC05/VC04 digital signal processor (DSP) devices. The GPIO peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an input, you can detect the state of an internal register. When configured as an output you can write to an internal register to control the state driven on the output pin.

- SPRUFO5 TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Universal Asynchronous Receiver/Transmitter (UART) User's Guide. This document describes the universal asynchronous receiver/transmitter (UART) peripheral in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The UART performs serial-to-parallel conversions on data received from a peripheral device and parallel-to-serial conversion on data received from the CPU.

- SPRUFP1 TMS320C5515/05/VC05 Digital Signal Processor (DSP) Successive Approximation (SAR) Analog to Digital Converter (ADC) User's Guide. This document provides an overview of the Successive Approximation (SAR) Analog to Digital Converter (ADC) on the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The SAR is a 10-bit ADC using a switched capacitor architecture which converts an analog input signal to a digital value.

- SPRUFP3 TMS320C5515/05/VC05 Digital Signal Processor (DSP) Liquid Crystal Display Controller (LCDC) User's Guide. This document describes the liquid crystal display controller (LCDC) in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The LCD controller includes a LCD Interface Display Driver (LIDD) controller.

- SPRUGU6— TMS320C5515/14/05/04 DSP External Memory Interface (EMIF) User's Guide. This document describes the operation of the external memory interface (EMIF) in the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. The purpose of the EMIF is to provide a means to connect to a variety of external devices.

Submit Documentation Feedback

# External Memory Interface (EMIF)

This document describes the operation of the External Memory Interface (EMIF) in the Digital Signal Processor (DSP).

Topic Page

| 1.1 | Introduction                         | 12 |

|-----|--------------------------------------|----|

| 1.2 | Architecture                         | 14 |

| 1.3 | Interfacing the EMIF to Mobile SDRAM | 54 |

| 1.4 | Registers                            | 58 |

Introduction www.ti.com

#### 1.1 Introduction

#### 1.1.1 Purpose of the External Memory Interface

The purpose of the EMIF is to provide a means to connect to a variety of external asynchronous devices including:

- NOR Flash, NAND Flash, and SRAM

- · Mobile single data rate (SDR) SDRAM and SDRAM devices

NOTE: Non-mobile SDRAM can be supported under certain circumstances. The C5504/05/14/15 always use mobile SDRAM initialization but are able to support SDRAM memories that ignore the BA0 and BA1 pins for the *load mode register* command. During the mobile SDRAM initialization, the device issues the *load mode register* initialization command to two different addresses that differ in only the BA0 and BA1 address bits. These registers are the Extended Mode register and the Mode register. The extended mode register exists only in mSDRAM and not in non-mSDRAM. If a non-mobile SDRAM memory ignores bits BA0 and BA1, the second loaded register value overwrites the first, leaving the desired value in the mode register and the non-mobile SDRAM will work with the device.

Section 1.3 contains examples of connecting the EMIF to mobile SDRAM devices.

#### 1.1.2 Features

The EMIF has the following features:

- Supports asynchronous devices (e.g., RAM, ROM, NOR Flash).

- Up to 8 MB asynchronous address range over 4 chip selects.

- Supports 8 and 16-bit data bus widths.

- Programmable cycle timings for each chip select.

- Page mode for NOR Flash.

- Supports extended wait cycles.

- Supports select strobe mode.

- Supports NAND Flash on 4 asynchronous chip selects.

- Supports 8 and 16-bit data bus widths.

- Programmable cycle timings for each chip select.

- Supports 1-bit ECC for 8 and 16-bit NAND Flash.

- Supports 4-bit ECC for 8-bit and 16-bit NAND Flash.

- Does not perform error correction.

www.ti.com Introduction

- Supports mobile SDR SDRAM devices.

- 8MB SDRAM address range over two chip select spaces.

- 16-bit data bus width.

- Supports CAS latencies of 2 and 3 (4 not supported).

- Supports 1, 2, and 4 internal banks.

- Supports 256, 512, 1024, 2048-word page sizes.

- Supports 4 and 8 burst lengths (1 and 2 not supported).

- Supports sequential burst type (interleave burst type not supported).

- SDRAM auto initialization from reset or configuration change.

- Bank interleaving across both the chip selects.

- Self refresh and pre-charge power down modes for low power.

- Partial array self-refresh and temperature controlled self refresh modes for low power in mobile SDR.

- Temperature controlled self-refresh is only supported for mobile SDR having on-chip temperature sensor.

- Supports prioritized refresh.

- Programmable SDRAM refresh rate and backlog counter.

- Programmable SDRAM timing parameters.

- Auto pre-charge not supported for better bank interleaving performance.

- Clock Suspend not supported for SDR SDRAM.

#### 1.1.3 Functional Block Diagram

Figure 1-1 illustrates a high-level view of the EMIF and its connections within the device. The CPU and DMA controller access the EMIF through a switched central resource. Section 1.2.3 describes the EMIF external pins and summarizes their purpose when interfacing with external devices.

Figure 1-1. EMIF Functional Block Diagram

#### 1.2 Architecture

This section provides details about the architecture and operation of the EMIF. Both SDRAM and asynchronous interface are covered, along with other system-related topics such as clock control and pin multiplexing.

#### 1.2.1 Clock Control

As shown in Figure 1-2, the clock generator receives either the real-time clock (RTC) or a signal from an external clock source and produces the DSP system clock. This clock is used by the DSP CPU and peripherals. The EMIF input clock is used to source the interface clock in synchronous mode and to generate the access cycles in asynchronous mode. The SDCLK can be generated from the EMIF CLK or a divide by two version of the EMIF CLK through EMIF Clock Divide Register (ECDR) register.

The C5515/14/05/04 has limitations to the clock frequency on the EM\_SDCLK pin (driven by SDCLK) based on the  $\text{CV}_{\text{DD}}$  and  $\text{DV}_{\text{DDEMIF}}$ .

- When CV<sub>DD</sub> = 1.3 V, and DV<sub>DDEMIF</sub> = 3.3 V, 2.75 V, or 2.5 V, the maximum clock frequency on the EM\_SDCLK pin is limited to 100 MHz (EM\_SDCLK ≤ 100 MHz). Therefore, if SYSCLK ≤ 100 MHz, the EM\_SDCLK can be configured either as SYSCLK or SYSCLK/2, but if SYSCLK > 100 MHz, the EM\_SDCLK must be configured as SYSCLK/2.

- When CV<sub>DD</sub> = 1.05 V, and DV<sub>DDEMIF</sub> = 3.3 V, 2.75 V, or 2.5 V, the maximum clock frequency on the EM\_SDCLK pin is limited to 60 MHz (EM\_SDCLK ≤ 60 MHz). Therefore, if SYSCLK ≤ 60 MHz, the EM\_SDCLK can be configured as either SYSCLK or SYSCLK/2, but if SYSCLK > 60 MHz, the EM\_SDCLK must be configured as SYSCLK/2.

- When DV<sub>DDEMIF</sub> = 1.8 V, regardless of the CV<sub>DD</sub> voltage, the clock frequency on the EM\_SDCLK pin must be configured as SYSCLK/2.

The device includes logic which can be used to gate the clock to its on-chip peripherals, including the EMIF. The input clock to the EMIF can be enabled and disabled through the peripheral clock gating configuration register 1 (PCGCR1).

Figure 1-2. Clocking Diagram for the EMIF

#### 1.2.2 EMIF Requests

Different modules within the DSP can make requests to the EMIF. These requests consist of accesses to SDRAM memory, asynchronous memory, and EMIF registers. Because the EMIF can process only one request at a time, a switch central resource (SCR) exists within the DSP to provide prioritized requests from the different sources to the EMIF.

- 1. CPU (peripheral register access)

- 2. CPU (data access)

- 3. CPU (instruction fetch)

- 4. DMA Controller 3

- 5. USB

- 6. LCD

If a request is submitted to the EMIF from two or more sources simultaneously, the SCR will arbitrate between the difference sources using a round-robin approach. Upon completion of a request, the SCR again evaluates the pending requests and forwards the next pending request to the EMIF.

When the EMIF receives a request, it may or may not be immediately processed. In some cases, the EMIF will perform one or more auto refresh cycles before processing the request. For details on the internal arbitration of the EMIF between performing requests and performing auto refresh cycles, see Section 1.2.10.

#### **CAUTION**

The EMIF does not support constant addressing mode. All request serviced by the EMIF must use a linear (incrementing) addressing mode.

#### 1.2.3 Memory Map

External memory is divided into several chip select spaces. On the device CPU, DMA controller 3 (DMA3) and USB and LCD can access external memory. The starting address for each of the chip select spaces in external memory is different from the point-of-view of these modules. The memory map as seen by these modules are shown in Table 1-1.

Table 1-1. EMIF Memory Map

| DSP Memory<br>Map | Size (Bytes)      | CPU Start Word<br>Address | DMA3 Start Byte<br>Address | USB Start Byte<br>Address | LCD Start Byte<br>Address |

|-------------------|-------------------|---------------------------|----------------------------|---------------------------|---------------------------|

| EMIF CS0          | 8M <sup>(1)</sup> | 02 8000h                  | 0100 0000h                 | 0100 0000h                | 0100 0000h                |

| EMIF CS2          | 4M                | 40 0000h                  | 0200 0000h                 | 0200 0000h                | 0200 0000h                |

| EMIF CS3          | 2M                | 60 0000h                  | 0300 0000h                 | 0300 0000h                | 0300 0000h                |

| EMIF CS4          | 1M                | 70 0000h                  | 0400 0000h                 | 0400 0000h                | 0400 0000h                |

| EMIF CS5 (2)      | 1M                | 78 0000h                  | 0500 0000h                 | 0500 0000h                | 0500 0000h                |

<sup>&</sup>lt;sup>(1)</sup> This is an approximate value.

#### 1.2.4 Signal Descriptions

Table 1-2 describes the EMIF pins that are used to interface to external devices.

Table 1-2. EMIF Pins Used to Access Both SDRAM and Asynchronous Devices

| Pin(s)      | Туре         | Description                                                                                                                                                                                                                                                                                                |

|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EM_A[20:0]  | Output       | EMIF address bus. When interfacing to an SDRAM device, these pins are primarily used to provide the row and column address to the SDRAM. When interfacing to an asynchronous device, these pins are used in conjunction with the EM_BA[1:0] pins to form the address that is sent to the device.           |

| EM_D[15:0]  | Input/Output | EMIF data bus.                                                                                                                                                                                                                                                                                             |

| EM_BA[1:0]  | Output       | When interfacing to an SDRAM device, these pins are used to provide the bank address inputs to the SDRAM. When interfacing to an asynchronous device, these pins are used in conjunction with the EM_A[20:0] pins to form the address that is sent to the device.                                          |

| EM_DQM[1:0] | Output       | Active-low byte enables. When interfacing to SDRAM, these pins are connected to the $\overline{\text{DQM}}$ pins of the SDRAM to individually enable/disable each of the bytes in a data access. When interfacing to an asynchronous device, these pins are connected to byte enables.                     |

| EM_WE       | Output       | Active-low write enable. When interfacing to SDRAM, this pin is connected to the WE pin of the SDRAM and is used to send commands to the device. When interfacing to an asynchronous device, this pin provides a signal that is active-low during the strobe period of an asynchronous write access cycle. |

When MP/MC = 0 the upper 128K bytes of EMIF CS5 is used for ROM data.

| Table 1-3. El | MIF Pins | Specific to | SDRAM |

|---------------|----------|-------------|-------|

|---------------|----------|-------------|-------|

| Pin(s)     | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EM_CS[1:0] | Output | Active-low chip select pin for SDRAM devices. This pin is connected to the chip-select pin of the attached SDRAM device and is used for enabling/disabling commands. By default, the EMIF keeps this SDRAM chip select active, even if the EMIF is not interfaced with an SDRAM device. This pin is deactivated when accessing the asynchronous memory bank and is reactivated on completion of the asynchronous assess. |

| EM_SDRAS   | Output | Active-low row address strobe pin. This pin is connected to the RAS pin of the attached SDRAM device and is used for sending commands to the device.                                                                                                                                                                                                                                                                     |

| EM_SDCAS   | Output | Active-low column address strobe pin. This pin is connected to the CAS pin of the attached SDRAM device and is used for sending commands to the device.                                                                                                                                                                                                                                                                  |

| EM_SDCKE   | Output | Clock enable pin. This pin is connected to the CKE pin of the attached SDRAM device and is used for issuing the SELF REFRESH command which places the device in self refresh mode.                                                                                                                                                                                                                                       |

| EM_SDCLK   | Output | SDRAM clock pin. This pin is connected to the CLK pin of the attached SDRAM device.                                                                                                                                                                                                                                                                                                                                      |

#### Table 1-4. EMIF Pins Specific to Asynchronous Devices

| Pin(s)       | Туре   | Description                                                                                                                                                                                                                                                   |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EM_CS[5:2]   | Output | Active-low chip select pins for asynchronous devices. These pins are meant to be connected to the chip-select pins of the attached asynchronous device. These pins are active only during accesses to the asynchronous memory.                                |

| EM_OE        | Output | Active-low pin enable for asynchronous devices. This pin provides a signal which is active-low during the strobe period of an asynchronous read access cycle.                                                                                                 |

| EM_R/W       | Output | Active-low read/write select pin. This pin is high for the duration of an asynchronous read access cycle and low for the duration of an asynchronous write cycle.                                                                                             |

| EM_WAIT[3:0] | Input  | Wait input with programmable polarity / NAND Flash ready input. An asynchronous device can extend the strobe period of an access cycle by asserting the wait input pins. When connected to NAND flash devices these pins function as NAND Flash ready inputs. |

#### 1.2.5 Pin Multiplexing

The EMIF address pins EM\_A[20:15] are multiplexed with GPIO pins GPIO[26:21]. The external bus selection register (EBSR) controls the functionality of these pins. For more details on this register, see the device-specific data manual.

#### 1.2.6 SDRAM Controller and Interface

The EMIF can gluelessly interface to mobile SDR SDRAM devices and supports such features as self refresh mode and prioritized refresh. In addition, it provides flexibility through programmable parameters such as the refresh rate, CAS latency, and many SDRAM timing parameters. The following sections include details on how to interface and properly configure the EMIF to perform read and write operations to externally connected SDR SDRAM devices. The SDCLK\_EN bit must be set in the Clock Configuration register 1 (CCR1) 0x1C1E to turn on the SDRAM clock.

Non-mobile SDRAM can be supported under certain circumstances. The C5504/05/14/15 always use mobile SDRAM initialization but are able to support SDRAM memories that ignore the BA0 and BA1 pins for the *load mode register* command. During the mobile SDRAM initialization, the device issues the *load mode register* initialization command to two different addresses that differ in only the BA0 and BA1 address bits. These registers are the Extended Mode register and the Mode register. The extended mode register exists only in mSDRAM and not in non-mSDRAM. If a non-mobile SDRAM memory ignores bits BA0 and BA1, the second loaded register value overwrites the first, leaving the desired value in the mode register and the non-mobile SDRAM will work with device.

#### 1.2.6.1 SDRAM Commands

The EMIF supports the SDRAM commands described in Table 1-5. Table 1-6 shows the truth table for the SDRAM commands, and an example timing waveform of the PRE command is shown in Figure 1-3. The address pin EM\_A[10] is pulled low in this example to deactivate only the bank specified by the EM\_BA[1:0] pins.

**Table 1-5. EMIF SDRAM Commands**

| Command    | Description                                                                                                                                                                                                                                                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRE        | Pre-charge command. Depending on the value of EM_A[10], the PRE command either deactivates the open row in all banks $(EM_A[10] = 1)$ or only the bank specified by the $EM_BA[1:0]$ pins $(EM_A[10] = 0)$ .                                                                           |

| ACTV       | Activate command. The ACTV command activates the selected row in a particular bank for the current access.                                                                                                                                                                             |

| READ       | Read command. The READ command outputs the starting column address and signals the SDRAM to begin the burst read operation. Address EM_A[10] is always pulled low to avoid auto pre-charge. This allows for better bank interleaving performance.                                      |

| WRT        | Write command. The WRT command outputs the starting column address and signals the SDRAM to begin the burst write operation. Address EM_A[10] is always pulled low to avoid auto pre-charge. This allows for better bank interleaving performance.                                     |

| ВТ         | Burst-terminate command. The BT command is used to truncate the current read or write burst request.                                                                                                                                                                                   |

| LMR        | Load mode register command. The LMR command sets the mode register of the attached SDRAM devices and is only issued during the SDRAM initialization sequence described in Section 1.2.6.4.                                                                                             |

| REFR       | Auto-refresh command. The REFR command signals the SDRAM to perform an auto refresh according to its internal address.                                                                                                                                                                 |

| SLFR       | Self-refresh command. The self refresh command places the SDRAM into self-refresh mode, during which it provides its own clock signal and auto refresh cycles.                                                                                                                         |

| NOP        | No operation command. The NOP command is issued during all cycles in which one of the above commands is not issued.                                                                                                                                                                    |

| POWER DOWN | Power-down command. The POWER DOWN command signals the SDRAM to deactivate its input and output buffers, excluding CKE. The EMIF closes (pre-charge) all internal banks of the SDRAM prior to issuing the POWER DOWN command, therefore, the EMIF only supports pre-charge power down. |

| SDRAM<br>Pins: | CKE      | cs       | RAS      | CAS      | WE    | BA[1:0]    | A[12:11]    | A[10]    | A[9:0]    |

|----------------|----------|----------|----------|----------|-------|------------|-------------|----------|-----------|

| EMIF<br>Pins:  | EM_SDCKE | EM_CS[n] | EM_SDRAS | EM_SDCAS | EM_WE | EM_BA[1:0] | EM_A[12:11] | EM_A[10] | EM_A[9:0] |

| PRE            | Н        | L        | L        | Н        | L     | Bank/X     | Х           | L/H      | Х         |

| ACTV           | Н        | L        | L        | Н        | Н     | Bank       | Row         | Row      | Row       |

| READ           | Н        | L        | Н        | L        | Н     | Bank       | Column      | L        | Column    |

| WRT            | Н        | L        | Н        | L        | L     | Bank       | Column      | L        | Column    |

| ВТ             | Н        | L        | Н        | Н        | L     | Х          | Х           | Х        | Х         |

| LMR            | Н        | L        | L        | L        | L     | Х          | Mode        | Mode     | Mode      |

| REFR           | Н        | L        | L        | L        | Н     | Х          | Х           | Х        | Х         |

| SLFR           | L        | L        | L        | L        | Н     | Х          | Х           | Х        | Х         |

| NOP            | Н        | L        | Н        | Н        | Н     | Х          | Х           | Х        | Х         |

Table 1-6. Truth Table for SDRAM Commands

Figure 1-3. Timing Waveform for SDRAM PRE Command

#### 1.2.6.2 Interfacing to Mobile SDRAM

The EMIF supports a glueless interface to mobile SDRAM devices with the following characteristics:

- Pre-charge bit is A[10]

- The number of column address bits is 8, 9,10, or 11

- The number of row address bits is less than or equal to 14

- The number of internal banks is 1, 2, or 4

Figure 1-4 shows an interface between the EMIF and a single mobile SDRAM device. The mobile SDRAM device can be connected to either EM\_CS0 or EM\_CS1, however the proper external memory address must be used to activate the correct chip select pin. For more details, see Section 1.2.6.11. Note that when operated in SDRAM mode, the EMIF bus is always 16 bits wide.

Figure 1-4. EMIF to mSDRAM Connection

#### 1.2.6.3 SDRAM Configuration Registers

The operation of the EMIF's SDRAM interface is controlled by programming the appropriate configuration registers. This section describes the purpose and function of each configuration register, but Section 1.4 should be referenced for a more detailed description of each register, including the default registers values and bit-field positions. The following tables list the main SDRAM configuration registers, along with a description of each of their programmable fields.

NOTE: Writing to SDCR1 or the lower byte of SDCR2 causes the EMIF to abandon whatever it is currently doing and trigger the SDRAM initialization procedure described in Section 1.2.6.4.

Table 1-7. Description of Bit Fields in SDRAM Configuration Registers (SDCR1 and SDCR2)

| Parameter | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR        | This bit controls entering and exiting of the Self-Refresh mode. The field should be written using a byte-write to the upper byte of SDCR2 to avoid triggering the SDRAM initialization sequence.                                                                                                                                                                                                                                                                                                                                                                      |

| PD        | This bit controls entering and exiting of the Power down mode. The field should be written using a byte-write to the upper byte of SDCR2 to avoid triggering the SDRAM initialization sequence. If both SR and PD bits are set, the EMIF will go into Self Refresh. See Section 1.2.6.4                                                                                                                                                                                                                                                                                |

| PDWR      | Perform refreshes during Power Down. Writing a 1 to this bit will cause the EMIF to exit the power down state and issue an AUTO REFRESH command every time Refresh May level is set.                                                                                                                                                                                                                                                                                                                                                                                   |

| CL        | CAS latency. This field defines the number of clock cycles between when an SDRAM issues a READ command and when the first piece of data appears on the bus. The value in this field is sent to the attached SDRAM device via the LOAD MODE REGISTER command during the SDRAM initialization procedure as described in Section 1.2.6.4. Only values of 2h (CAS latency = 2) and 3h (CAS latency = 3) are supported and should be written to this field. A 1 must be simultaneously written to the BIT11_9LOCK bit field of SDCR1 in order to write to the CL bit field. |

| IBANK     | <ul> <li>Number of Internal SDRAM Banks. This field defines the number of banks inside the attached SDRAM devices in the following way:</li> <li>When IBANK = 0, 1 internal bank is used</li> <li>When IBANK = 1h, 2 internal banks are used</li> <li>When IBANK = 2h, 4 internal banks are used</li> <li>This field value affects the mapping of logical addresses to SDRAM row, column, and bank addresses.</li> </ul>                                                                                                                                               |

| PAGESIZE  | <ul> <li>Page Size. This field defines the internal page size of the attached SDRAM devices in the following way:</li> <li>When PAGESIZE = 0, 256-word pages are used</li> <li>When PAGESIZE = 1h, 512-word pages are used</li> <li>When PAGESIZE = 2h, 1024-word pages are used</li> <li>When PAGESIZE = 3h, 2048-word pages are used</li> <li>This field value affects the mapping of logical addresses to SDRAM row, column, and bank addresses.</li> </ul>                                                                                                         |

Table 1-8. Description of Bit Fields in SDRAM Refresh Control Register (SDRCR)

| Parameter | Description                                                                                                                                                                                                                                                                                                                                                          |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFRATE   | Refresh Rate. This field controls the rate at which attached SDRAM devices will be refreshed. The equation below can be used to determine the required value of REFRATE for an SDRAM device: REFRATE <= f <sub>EM_SDCLK</sub> / (Required SDRAM Refresh Rate). More information about the operation of the SDRAM refresh controller can be found in Section 1.2.6.6. |

Table 1-9. Description of Bit Fields in SDRAM Timing Registers (SDTIMR1 and SDTIMR2)

| Parameter | Description                                                                                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T_RFC     | SDRAM Timing Parameters. These fields configure the EMIF to comply with the AC timing constraints                                                               |

| T_RP      | and to more efficiently schedule its operations. More details about each of these parameters can be                                                             |

| T_RCD     | found in the register description in section 4. These parameters should be set to satisfy the corresponding timing requirements found in the SDRAM's datasheet. |

| T_WR      | Corresponding unling requirements lound in the ODITAIN'S datasheet.                                                                                             |

| T_RAS     |                                                                                                                                                                 |

| T_RC      |                                                                                                                                                                 |

| T_RRD     |                                                                                                                                                                 |

Table 1-10. Description of Bit Fields in SDRAM Self Refresh Exit Timing Register (SDSRETR)

| Parameter | Description                                                                                                                                                                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T_XS      | Self Refresh Exit Parameter. The T_XS field of this register informs the EMIF about the minimum number of EM_SDCLK cycles required between exiting Self Refresh and issuing any command. This parameter should be set to satisfy the t <sub>XSR</sub> value for the attached SDRAM device. |

#### 1.2.6.4 Mobile SDRAM Auto-Initialization Sequence

The EMIF automatically performs an mobile SDRAM initialization sequence, regardless of whether it is interfaced to an SDRAM device. No memory accesses to the SDRAM and asynchronous interfaces are performed until this auto-initialization is complete. The auto-initialization sequence is performed by the EMIF when either of the following two events occur:

- The EMIF is taken out of reset. See Section 1.2.12 for more information on EMIF reset.

- A write is performed to SDRAM configuration register 1 (SDCR1) or the least significant byte of SDRAM configuration register 2 (SDCR2). In either of these cases the EMIF starts from step 2 below, without waiting for the eight SDRAM refresh intervals.

An SDRAM initialization sequence consists of the following steps:

- 1. The EMIF drives EM\_SDCKE high and begins continuously issuing NOP commands.

- 2. After eight SDRAM refresh intervals, the EMIF issues a PRE command with EM\_A[10] held high to indicate all banks. The SDRAM refresh interval is as defined by the REFRATE field in the SDRAM refresh control register (SDRCR).

- After eight REFR commands, the EMIF issues an LMR command to the extended mode register with

the settings as described in Table 1-11. (This step is needed for mobile SDRAM; because the chip

does not have a pin to select if mobile SDRAM or SDRAM is used, this command is always sent during

initialization. Therefore, SDRAM support is limited to memories that can handle this extra initialization

command.)

- 4. The EMIF issues another LMR command, this time to the mode register with the settings as described in Table 1-12.

- 5. Finally, the EMIF performs an auto refresh cycle (see Section 1.2.6.6).

Table 1-11. Extended Mode Register Settings During Auto-Init Sequence

| Mode Register Bit | Mode Register Field | Init Value  | Description                                                                                                                           |

|-------------------|---------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 15-7              | Reserved            | 00h         | Reserved                                                                                                                              |

| 6-5               | Drive Strength      | SDRAM_DRIVE | Sets the drive strength of the memory data pins. The setting for these bits is taken from the SDRAM_DRIVE bits of the SDCR2 register. |

Table 1-11. Extended Mode Register Settings During Auto-Init Sequence (continued)

| Mode Register Bit | Mode Register Field                           | Init Value | Description                                                                                                                                                |

|-------------------|-----------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-3               | Internal Temperature Compensated Self-Refresh | 0h         | Specifies the maximum case temperature for self-refresh interval adjustment.                                                                               |

| 2-0               | Partial Array Self-Refresh                    | PASR       | Specifies the amount of memory that will be refreshed during a SLFR command. The setting for these bits is taken from the PASR bits of the SDCR2 register. |

Table 1-12. Mode Register Settings During Auto-Init Sequence

| Mode Register Bit | Mode Register Field     | Init Value | Description                                                                                                                                     |

|-------------------|-------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:10             | Reserved                | 00h        | Reserved.                                                                                                                                       |

| 9                 | Write Burst Mode        | 0h         | Specifies the write burst mode. This bit is set to 0 to indicate the burst type setting specified by bits 2-0 applies to both reads and writes. |

| 8-7               | Standard Operating Mode | 0h         | Selects standard operating mode.                                                                                                                |

| 6-4               | CAS Latency             | CL         | Specifies the CAS latency. The value for these bits is taken from the CL bits of the SDCR1 register.                                            |

| 3                 | Burst Type              | 0h         | Specifies the burst type. This bit is set to 0 to indicate sequential bursts.                                                                   |

| 2-0               | Burst Length            | 3h         | Specifies the burst length. These bits are set to 3 to indicate a burst length of 8.                                                            |

#### 1.2.6.5 SDRAM Configuration Procedure

The EMIF automatically performs the mSDRAM initialization sequence described in Section 1.2.6.4. However, you must follow the procedure listed below before performing any SDRAM requests.

The steps in the initialization procedure are as follows:

- 1. Turn SD clock on by writing 0x0001 to Clock Configuration Register 1 (CCR1) [0x1C1Eh].

- 2. Program SDTIMR1, SDTIMR2, and SDSRETR to satisfy the timing requirements for the attached SDRAM device. The timing parameters should be taken from the SDRAM datasheet.

- 3. Program the REFRATE field of SDRCR such that the following equation is satisfied: (REFRATE x 8) / (f<sub>EM\_SDCLK</sub>) > 100 microseconds or 200 microseconds, depending on the power-up constraint specified by the SDRAM memory. The SDRAM power-up constraint specifies that 200 microseconds (sometimes 100 microseconds) should exist between receiving stable VDD and CLK and the issuing of a PRE command. For example, an EM\_SDCLK frequency of 100 MHz would require setting REFRATE to 1251 (4E3h) or higher to meet a 100 microseconds constraint.

- 4. Program SDCR1 and SDCR2 to match the characteristics of the attached SDRAM device. This will cause the auto-initialization sequence in Section 1.2.6.4 to be re-run with the new value of REFRATE.

- 5. Perform a read from the SDRAM to guarantee that step 3 will occur after the initialization process has completed. Alternatively, wait for 200 microseconds.

- 6. Finally, program the REFRATE field to match that of the attached device's refresh interval. See Section 1.2.6.6.2 for details on determining the appropriate value.

After following the above procedure, the EMIF is ready to perform accesses to the attached SDRAM device. See Section 1.3 for an example of configuring the SDRAM interface.

**NOTE:** You must follow the steps in Section 1.2.13 before starting the steps outlined in this section.

#### 1.2.6.6 SDRAM Refresh Controller

An SDRAM device requires that each of its rows be refreshed at a minimum required rate. The EMIF can meet this constraint by performing auto refresh cycles at or above this required rate. An auto refresh cycle consists of issuing a PRE command to all banks of the SDRAM device followed by issuing a REFR command. To inform the EMIF of the required rate for performing auto refresh cycles, the REFRATE field of the SDRAM Refresh Control Register (SDRCR) must be programmed. The EMIF will use this value along with two internal counters to automatically perform auto refresh cycles at the required rate. The auto refresh cycles cannot be disabled, even if the EMIF is not interfaced with an SDRAM. The remainder of this section details the EMIF's refresh scheme and provides an example for determining the appropriate value to place in the REFRATE field of SDRCR.

#### 1.2.6.6.1 EMIF Refresh Scheme

The EMIF uses two counters to schedule REFR command: a 13-bit decrementing refresh interval counter and a 4-bit refresh backlog counter. The interval counter is loaded with the REFRATE field value at reset. The interval counter decrements by one each cycle until it reaches zero at which point it reloads from REFRATE and restarts decrementing. The counter also reloads and restarts decrementing whenever the REFRATE field is updated.

The refresh backlog counter records the number of REFR commands the EMIF currently has outstanding. The backlog counter increments by one each time the interval counter reloads (unless it has reached its maximum value of 15). The backlog counter decrements by one each time the EMIF issues a REFR command (unless it is already at zero).

The EMIF uses the refresh backlog counter to determine the urgency with which an auto refresh cycle should be performed. The four levels of urgency are described in Table 1-13. This refresh scheme allows the required refreshes to be performed with minimal impact on memory access requests.

| Urgency Level   | Refresh Backlog<br>Counter Range | Action Taken                                                                                                                                                                                                       |

|-----------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Refresh May     | 1-3                              | An auto-refresh cycle is performed only if the EMIF has no requests pending and none of the SDRAM banks are open.                                                                                                  |

| Refresh Release | 4-7                              | An auto-refresh cycle is performed if the EMIF has no requests pending, regardless of whether any SDRAM banks are open.                                                                                            |

| Refresh Need    | 8-11                             | An auto-refresh cycle is performed at the completion of the current access unless there are read requests pending.                                                                                                 |

| Refresh Must    | 12-15                            | Multiple auto-refresh cycles are performed at the completion of the current access until the Refresh Release urgency level is reached. At that point, the EMIF can begin servicing any new read or write requests. |

Table 1-13. Refresh Urgency Levels

The refresh counters do not operate when SDRAM has been put into self-refresh mode.

The EMIF issues REFR commands within auto refresh cycles. An auto refresh cycle consists of issuing an REFR command and waiting T\_RFC (see the SDRAM timing register 2) cycles before re-checking the refresh levels. If the Refresh Release level is not reached, the EMIF starts another auto refresh cycle, otherwise it returns to the idle state.

#### 1.2.6.6.2 Determining the Appropriate Value for the REFRATE Field

The value that should be programmed into the refresh-rate (REFRATE) field of SDRCR can be calculated by using the frequency of the EM\_SDCLK signal ( $f_{EM\_SDCLK}$ ) and the required refresh rate of the SDRAM ( $f_{Refresh}$ ).

The following formula can be used to calculate REFRATE:

$REFRATE \le f_{EM\_SDCLK} / f_{Refresh}$

The SDRAM datasheet often communicates the required SDRAM Refresh Rate in terms of the number of REFR commands required in a given time interval. The required SDRAM Refresh Rate in the formula above can be therefore be calculated by dividing the number of required cycles per time interval ( $n_{cycles}$ ) by the time interval given in the datasheet ( $t_{Refresh\ Period}$ ):

$f_{Refresh} = n_{cycles} / t_{Refresh Period}$

Combining these formulas, the value that should be programmed into the REFRATE field can be computed as:

REFRATE  $\leq f_{EM SDCLK} \times t_{Refresh Period} / n_{cycles}$

The following example illustrates calculating the value of REFRATE. Given that:

- f<sub>EM SDCLK</sub> = 100 MHz

- t<sub>Refresh Period</sub> = 64 ms (required refresh interval of the SDRAM)

- n<sub>cycles</sub> = 8192 (number of cycles in a refresh interval for the SDRAM)

REFRATE can be calculated as:

REFRATE ≤ 100 MHz × 64 ms/8192

**REFRATE ≤ 781.25**

REFRATE = 782 cycles = 30Eh cycles

#### 1.2.6.7 Self Refresh Mode

To reduce the power consumption of the SDRAM device, you can request the EMIF to issue a SLRF command by setting the SR bit of SDCR2 to 1. When this bit is set, the EMIF will continue normal operation until all outstanding memory access requests have been serviced and the SDRAM refresh backlog has been cleared.

**NOTE:** The SR bit should be set and cleared using a byte-write to the upper byte of the SDCR2 to avoid triggering the SDRAM initialization sequence. The BYTEMODE bits in the EMIF system control register can be used to limit writes to EMIF registers to the upper or lower byte. See Section 1.2.8 for more details.

While in the self-refresh state, the EMIF continues to service asynchronous bank requests and register accesses as normal with one caveat: the EMIF will not park the data bus following a read to asynchronous memory while in the self-refresh state; instead, the EMIF tri-states the data bus. Therefore, it is not recommended to perform asynchronous read operations while the EMIF is in the self-refresh state in order to prevent floating inputs on the data bus. More information about data bus parking can be found in Section 1.2.9.

The EMIF will come out of the self-refresh state if the SR bit is cleared or an SDRAM access is requested while in the self-refresh state and T\_RAS + 1 cycles have elapsed since the SLFR command was issued. The value of T\_RAS is taken from SDRAM timing register 2. The EMIF exits from the self-refresh state by driving EM\_SDCKE high, waiting T\_XS + 1 cycles, and performing an auto refresh cycle. The value for T\_XS is taken from the SDRAM self refresh exit timing register.

While in self-refresh mode, the SDRAM device consumes a minimal amount of power while performing its own refresh cycles. The SDRAM device should also be placed into self-refresh mode when changing the frequency of EM\_SDCLK. If the frequency of EM\_SDCLK changes while the SDRAM is not in self-refresh mode, the memory must be re-initialized following the procedure described in Section 1.2.6.5.

To use partial array self-refresh for mobile SDRAM, the PASR bits in the SDCR2 register must be appropriately programmed. The EMIF performs bank interleaving when IBANK\_POS = 0 in SDCR2. Since the SDRAM is partially refreshed during partial array self refresh, it is recommended that IBANK\_POS be set to 1 for software ease. If IBANK\_POS is set to 0, it is the responsibility of software to move critical data into the banks that are going to be refreshed during partial array self-refresh.

#### 1.2.6.8 Power Down Mode

To support low power modes, the EMIF can be requested to issue a POWER DOWN command to the SDRAM by setting the PD bit in SDCR2. When this bit is set, the EMIF will continue normal operation until all outstanding memory access requests have been serviced and the SDRAM refresh backlog has been cleared. At this point the EMIF will enter the power down state.

Upon entering this state, the EMIF will issue a POWER DOWN command (same as a NOP command but driving EM\_SDCKE low on the same cycle). The EMIF then maintains EM\_SDCKE low until it exits the power down state.

Since the EMIF services the refresh backlog before it enters the power down state, all internal banks of the SDRAM are closed (pre-charged) prior to issuing the POWER DOWN command. Therefore, the EMIF only supports pre-charge power down. The EMIF does not support active power down where internal banks of the SDRAM are open (active) before the POWER DOWN command is issued.

During the power down state, the EMIF services the SDRAM, asynchronous memory, and register accesses as normal, returning to the power down state upon completion.

The PDWR bit in the SDRAM configuration register indicates whether the EMIF should perform refreshes in power down state. If the PDWR bit is set, the EMIF exits power down state every time the Refresh Must level is reached, it performs REFR commands to the SDRAM, and then it returns back to the power down state. This evenly distributes the refreshes to the SDRAM in power down state. If the PDWR bit is not set, the EMIF does not perform any refreshes to the SDRAM. Therefore the data integrity of the SDRAM is not guaranteed upon power down exit if the PDWR bit is not set.

If the PD bit is cleared while in the power down state, the EMIF will come out of the power down state. To exit the power down state the EMIF drives EM\_SDCKE high and enters its idle state.

#### 1.2.6.9 SDRAM Read Operation

When the EMIF receives a read request to SDRAM, it performs one or more read access cycles. A read access cycle begins with the issuing of the ACTV command to select the desired bank and row of the SDRAM device. After the row has been opened, the EMIF proceeds to issue a READ command while specifying the desired bank and column address. The address pin EM\_A[10] is held low during the READ command to avoid auto-pre-charging. The READ command signals the SDRAM device to start bursting data from the specified address while the EMIF issues NOP commands. Following a READ command, the CL field of SDCR1 defines how many delay cycles will be present before the read data appears on the data bus. This is referred to as the CAS latency.

Figure 1-5 shows the signal waveforms for a basic SDRAM read operation in which a burst of data is read from a single page. A burst size of eight is always used for SDRAM accesses.

The EMIF will truncate a series of bursting data if the remaining addresses of the burst are not required to complete the request. The EMIF can truncate the burst in three ways:

- By issuing another READ to the same page in the same bank.

- By issuing a PRE command in order to prepare for accessing a different page of the same bank.