EECS 470 Lab 3 SystemVerilog Style Guide

Department of Electrical Engineering and Computer Science College of Engineering University of Michigan

Thursday, 25th January 2024

#### Administrivia

#### Verilog Style Guide

#### Verilog Style Guide

Brevity Indentation and Alignment SystemVerilog Features

#### Finite State Machines

# Administrivia

#### Homework

▶ Homework 2 is due Friday, 2<sup>nd</sup> February at 10PM (via Gradescope)

Projects

Project 2 is due Tuesday, 30<sup>th</sup> January at 11:59PM (via submission script)

### Help

We are available to answer questions on anything here. Office hours can be found on the course web site.

# Verilog Style

### What is good style?

- Easy to read

- Easy to understand

- Easy to maintain

- High reusability

- Mostly a matter of personal/team preference, or "First-Come First-Serve"

# Verilog Style

#### Why should I use good style?

- Easier to debug: save your sanity

- Important for group work: give your teammate(s) an easier life :)

- Mandatory in projects 1-3

## Verilog Style Rules

#### Goal: Clarity

- We'll look at a bad example

- Then how to fix it

- Derive a rule

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

# Brevity by Example

### Example

```

always_comb

begin

if (foo[3] == 1'b1)

begin

bar[3] = 1'b1;

bar[2] = 1'b0;

bar[1] = 1'b1;

bar[0] = 1'b1;

end else if (foo[2] == 1'b1)

begin

bar[3] = 1'b0;

bar[2] = 1'b1;

bar[1] = 1'b0;

bar[0] = 1'b0;

end

```

# Brevity by Example

### Example

```

always_comb

begin

if (foo[3] == 1'b1)

begin

bar[3] = 1'b1;

VS.

bar[2] = 1'b0;

bar[1] = 1'b1;

bar[0] = 1'b1;

end else if (foo[2] == 1'b1)

begin

bar[3] = 1'b0;

bar[2] = 1'b1;

bar[1] = 1'b0;

bar[0] = 1'b0;

end

```

#### Example Reformatted

```

always_comb

begin

if (foo[3]) bar = 4'b1011;

else if (foo[2]) bar = 4'b0100;

end

```

# Brevity by Example

### Example

logic [5:0] shift;

```

always_ff @(posedge clock)

begin

if (reset)

begin

shif_reg <= 6'b0;</pre>

end else begin

shift[0] <= foo;</pre>

shift[1] <= shift[0];</pre>

shift[2] <= shift[1];</pre>

shift[3] <= shift[2];</pre>

shift[4] <= shift[3];</pre>

shift[5] <= shift[4];</pre>

```

end

VS.

#### Brevity

# Brevity by Example

### Example

```

logic [5:0] shift;

```

```

always_ff @(posedge clock)

begin

if (reset)

begin

shif_reg <= 6'b0;

end else begin

shift[0] <= foo;

shift[1] <= shift[0];

shift[2] <= shift[1];

shift[3] <= shift[2];

shift[4] <= shift[3];

shift[5] <= shift[4];</pre>

```

#### Example Reformatted

logic [5:0] shift;

```

always_ff @(posedge clock)

begin

if (reset)

begin

shift <= 6'b0;

end else begin

shift <= {shift[4:0], foo};

end</pre>

```

end

end

## Brevity Rule

#### Rule

Brevity is (often) strongly correlated with the optimal solution. Be brief, where you can.

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

# **Brevity Rule**

Is brevity always better? Not necessarily ... You also need to be clear

(University of Michigan)

# **General Requirements**

### **Clarity Rules**

- Use meaningful names for signal; wire wire; is confusing

- Comment your designs; (a ^ b ~ ^ c) | (&d) is unintelligible without an explanation

- Conceptualize what you need to build before you start writing Verilog. A state machine diagram will be make the Verilog much easier...

## **General Requirements**

### Clarity Rules

Starter guide on signal namings: https://github.com/lowRISC/ style-guides/blob/master/VerilogCodingStyle.md#naming

# Clarity by Example

Lab 3: Style

# Clarity by Example

(University of Michigan)

```

Example

logic enable;

always_comb

begin

begin

enable =

VS.

(op[0]^op[1] | op[2] & op[3])?

1'b1: 0'b0:

end

end

```

### Example Reformatted

logic enable;

```

always_comb

if(op[3])

begin

if(op[2])

begin

enable = 1'b1:

end else if(op[0] ^ op[1])

begin

enable = 1'b1:

end else begin

enable = 1'b0:

end

end else begin

enable = 1'b0:

end

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ ののの

Thursday, 25<sup>th</sup> January 2024 13 / 39

```

# Brevity & Clarity Rules

- Use commonsense and intuition.

- Ask your teammate(s) to peer-review.

- Use the names to describe what is happening

- For example:

- "\_d" suffix for combinational wires

- "\_q" suffix for sequential registers

- "\_n" for active low signals

- Macros or parameters for describing names of states.

・ロト ・ 母 ト ・ ヨ ト ・ ヨ ト ・ ヨ

### Indentation

### Why are we interested in indentation?

- Readability easier to trace down

- Clarity easier to check what is in a given scope

<ロト <部ト <注入 < 注入 = 二 =

### Indentation by Example

#### Example

```

always_comb

begin

if(cond)

begin

n_state = `IDLE;

n_gnt = `NONE;

end else begin

n_state = `TO_A;

n_gnt = `GNT_A;

end

end

```

### Indentation by Example

#### Example

```

always_comb

begin

if(cond)

begin

n_state = `IDLE;

n_gnt = `NONE;

end else begin

n_state = `TO_A;

n_gnt = `GNT_A;

end

end

```

vs.

#### Example Reformatted

```

always_comb

begin

if (cond)

begin

n_state = `IDLE;

n_gnt = `NONE;

end else begin

n_state = `TO_A;

n_gnt = `GNT_A;

end

end

```

Thursday, 25<sup>th</sup> January 2024 16 / 39

### Indentation Rule

#### Rule

Items within the same scope should have the same indentation.

(University of Michigan)

Thursday, 25<sup>th</sup> January 2024 17 / 39

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

### Alignment

#### Why are we interested in alignment?

- Readability easier to trace down

- Clarity easier to check that everything is assigned

#### Example

```

always_comb

begin

if (cond)

begin

n_state = `IDLE;

n_gnt = `NONE;

end else begin

n_state = `TO_A;

n_gnt = `GNT_A;

end

end

```

#### Example

```

always_comb

begin

if (cond)

begin

n_state = `IDLE;

n_gnt = `NONE; VS.

end else begin

n_state = `TO_A;

n_gnt = `GNT_A;

end

end

```

```

Example Reformatted

```

```

always_comb

begin

if (cond)

begin

n_state = `IDLE;

n_gnt = `NONE;

end else begin

n_state = `TO_A;

n_gnt = `GNT_A;

end

end

```

#### Example

assign mux\_out = (cond1) ? (foo1&bar): (cond2) ? (foo2+cnt3) : (cond3) ? (foo3&~bar2) : 0;

#### Example

```

assign mux_out = (cond1) ? (foo1&bar): (cond2) ? (foo2+cnt3) : (cond3) ? (foo3&~bar2) : 0;

```

#### Example Reformatted

| assign mux_out = (cond1) | ? (foo1 & | bar) :      |

|--------------------------|-----------|-------------|

| (cond2)                  | ? (foo2 + | cnt3) :     |

| (cond3)                  | ? (foo3 & | ~bar2) : 0; |

# Alignment Rule

#### Rule

- Assignments should be aligned by column.

- Ternary statements should have the conditionals aligned, and each "if" should be on a new line.

- Try to align bit width declaration and indices when possible

- Spaces are preferable over tabs for portability across IDEs

# SystemVerilog Types

#### User-defined Types

- Useful for cleaning repeated declarations, specifically bundling connections

- Types can be named informatively, e.g. arch\_reg\_t

### Structs

#### About struct

- A package of signals (wire or logic)

- Basically follow C conventions

- List of signal declarations

- Named with \_t ending

### Syntax

- struct

- List of signals between braces ({})

- Name after braces, followed by a semicolon (;)

3

イロト イボト イヨト イヨト

### Structs

### Example

typedef struct {

logic [7:0] a; //Structs can contain

logic b; //other structs, like

arch\_reg\_t c; //<-- this line

} example\_t; //named with \_t</pre>

#### Example

typedef struct packed {

addr\_t pc;

logic valid;

} prf\_entry\_t;

#### Usage Example

prf\_entry\_t [31:0] prf; assign prf[1].valid = 1'b0;

### Enums

#### About enum

- List of possible values, but named instead of numbered

- Good for state machine states

- Can be shown in Verdi instead of the associated value

#### Verdi Example

### Syntax

- enum

- List of values between braces ({})

- Name after braces, followed by a semicolon (;)

3

イロト イボト イヨト イヨト

### Enums

#### Example

typedef enum logic [3:0] {

IDLE, //=0, by default

GNT[0:7], //Expands to GNT0=1,...GNT7=8

RESET //=9

} arb\_state;

### Example

typedef enum logic [1:0] {

ADD = 2'b00, //The value associated with

MULT = 2'b10, //a particular name can be

NOT = 2'b11, //assigned explicitly.

AND = 2'b01

} opcode;

#### Usage Example

arb\_state state, n\_state; assign n\_state = IDLE;

# Typedef

#### About typedef

- Necessary for reuse of a struct or enum

- Without a typedef, a struct/enum must be redefined at each instance declaration

- Also useful in clearly naming commonly sized buses

Syntax

- typedef

- by any signal declaration or struct or enum declaration

- Name for the type followed by a semicolon (;)

# Typedef by Example

#### Example: Typedef'd Enum

//typedef, then definition, then name; typedef enum logic [3:0] { IDLE, GNT[0:7], RESET } arb\_state;

Example: Type Synonym //typedef, then definition, then name; typedef logic [63:0] addr;

# Procedural FSM Design

### FSM Process

- All states should be typedef enum

- All next state logic should go into a combinational block, following all combinational rules

- All resets should be synchronous (to the clock)

- All output assignments should go in their own combinational block

- The only logic in the sequential block should be the state assignment (to the computed next state)

### Finite State Machine Skeleton

```

typedef enum logic [(NUM_STATES-1):0] { STATES } fsm_state;

```

```

module fsm(

input wire inputs,

output logic outputs

);

fsm state state. next state:

always_comb begin

/* Transitions from a diagram go here */

/* next_state = f(inputs, state) */

end

always_ff @(posedge clock) begin

if(reset) begin

state <= DEFAULT;</pre>

end else begin

state <= next state:</pre>

end

end

endmodule

```

人口 医水道 医水油 医水白 医白白

### Finite State Machine Example

```

typedef enum logic { LOCKED, UNLOCKED } ts_state;

module turnstile(

input wire coin, push,

input wire clock, reset,

output ts_state state

);

ts state next state:

always_comb begin

next_state = state;

if (state==LOCKED && coin) next_state = UNLOCKED;

if (state==UNLOCKED && push) next_state = LOCKED;

end

always_ff @(posedge clock) begin

if (reset) state <= LOCKED:

else state <= next_state;</pre>

end

endmodule

```

- So last time we talked about why to write a testbench

- We also talked about how to write a good testbench

- All metrics that we talked about are rather qualitative, though

- How do we quantitatively measure how good a testbench is? Code coverage!

### Code Coverage Types

- Line Coverage measures statements in your HDL code that have been executed in the simulation

- Toggle Coverage measures the bits of logic that have toggled during simulation. A toggle simply means that a bit changes from 0 to 1 or from 1 to 0.

- One of the oldest metrics of coverage in hardware designs and can be used at both the register transfer level (RTL) and gate level.

- May give low numbers if you have wide signals (ex: adding 64 bit numbers)

- Condition Coverage measures how the variables or sub-expressions in the conditional statements are evaluated during simulation. It can find errors in the conditional statements that cannot be found by other coverage analysis.

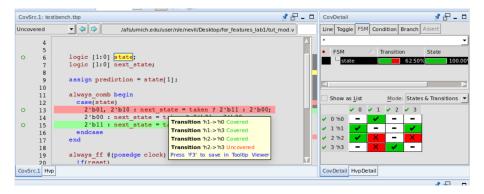

### Code Coverage Types Cont.

- Branch Coverage measures the coverage of expressions and case statements that affect the control flow (such as if-statement and while-statement) of the HDL. It focuses on the decision points that affect the control flow of the HDL execution.

- FSM Coverage verifies that every legal state of the state machine has been visited and that every transition between states has been covered.

- For more information about coverage, feel free to ask us or search online!

#### Coverage compile time options

- -cm line|cond|fsm|tgl|branch|assert

- The arguments specifies the types of coverage:

- line Compile for line or statement coverage.

- cond Compile for condition coverage.

- fsm Compile for FSM coverage.

- tgl Compile for toggle coverage.

- branch Compile for branch coverage

- assert Compile for SystemVerilog assertion coverage.

- If you want VCS to compile for more than one type of coverage, use the plus (+) character as a delimiter between arguments, for example:

- vcs -sverilog -xprop=tmerge +vc -Mupdate -line -full64 -kdb -lca -nc -debug\_access -cm fsm+tgl mydesign.sv mytest.sv -o simv

- ./simv -cm fsm+tgl

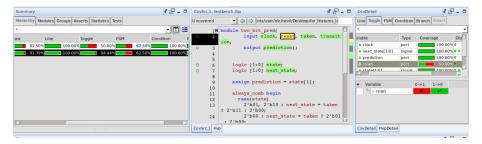

### Coverage example

#### Run make ${\tt verdi\_cov}$ in the lab 3 scripts to open Verdi in coverage mode.

#### Verdi Coverage

イロト イポト イヨト イヨト

### Coverage example Cont.

#### Verdi Coverage

We will come back to this later in the final project. As part of milestone 1, you will need to submit a module along with a testbench and we will grade you based on your coverage percentage, but that'll be much later. In the meanwhile... Give it a try on your project 2 testbench!

# Lab Assignment

- Assignment is posted to the <u>course website</u> as Lab 3 Assignment.

- If you get stuck...

- Ask a neighbor, quietly

- Put yourself in the help queue

- When you are finished, put yourself on help queue to get checked off.

- If you are unable to finish today, the assignment needs to be checked off by next Friday.