## University of Michigan EECS 522: Analog Integrated Circuits Winter 2009

CAD 2

Issued 3/11/2009 - Due 3/27/2009

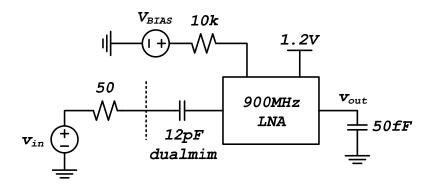

In this assignment, you will design an LNA for the 900MHz ISM band. The LNA should meet the specifications listed in the table below. The LNA should be designed using hand calculations, and simulated in Cadence using the IBM  $0.13\mu m$  CMOS process. Layout of the LNA is not required.

| Specification           | Value                           |

|-------------------------|---------------------------------|

| Peak S21 (Gain)         | > 10dB                          |

| 3dB Bandwidth           | 200MHz < BW < 300MHz            |

| <b>Center Frequency</b> | 900MHz                          |

| <b>Noise Figure</b>     | < 1.7dB between 800MHz and 1GHz |

| <b>S11</b>              | < -10dB between 800MHz and 1GHz |

| P1dB                    | > -30dBm (input referred)       |

| IIP3                    | > -15dBm (input referred)       |

| Power Consumption       | < 4mW (including bias circuits) |

## **Guidelines for Design:**

- 1. Use any design methodology you want, but use a design methodology.

- 2. Use only components available in the cmrf8sf library in your design. All inductors, capacitors, and resistors must be used from this library (no AnalogLib components). Use only nfet\_rf or pfet\_rf transistors (RF devices only).

- 3. The input has a fixed  $50\Omega$  source impedance.

- 4. The input must be AC coupled to your amplifier using a dualmimcap component from cmrf8sf with size 50μm by 50μm (value is about 12pF).

- 5. You are allowed to use one bias voltage source to bias your amplifier, connected to your circuit through an ideal  $10k\Omega$  resistor (from AnalogLib). You can set the value of this bias voltage anywhere between 0 and 1.2V.

- 6. The power supply must be 1.2V.

- 7. Your circuit must drive an ideal 50fF load capacitor (from AnalogLib).

## What to Turn In:

- 1. A *legible* schematic of your amplifier, clearly indicating the sizes and values of all devices. In addition to values, label the outer diameter and number of turns for inductors, X and Y dimensions for capacitors and resistors, W, L, and number of fingers for FETs.

- 2. A summary table comparing all measured values to the specifications in the table above.

- 3. Legible plots of S11, S21, P1dB, IIP3, and Noise Figure.