# EECS 570 Programming Assignment 1

University of Michigan

January 14, 2022

University of Michigan

EECS 570 Programming Assignment 1

January 14, 2022 1 / 40

イロト 不得 トイヨト イヨト 二日

- Sign up for final project groups ASAP

- https://docs.google.com/spreadsheets/d/ 1NDgrDKN5uI5Ve9K8IGd1Gg6222hzBDksut93-9NT0tY/edit?usp= sharing

- A team must have an identity!

- Project proposal due Monday 1/31

### Overview

#### Medical Imaging using Ultrasound

- Introduction

- Transmission and Reception

### Intel MIC Architecture

- Architectural Overview

- Programming the MIC

#### Introduction to POSIX Threads

- Thread Creation and Joining

- Synchronization Primitives

# Portable Medical Imaging Devices

- Medical imaging moving towards portability

- MEDICS (X-Ray CT) [Dasika '10]

- Handheld 2D Ultrasound [Fuller '09]

- Not just a matter of convenience

- Improved patient health [Gunnarsson '00, Weinreb '08]

- Access in developing countries

- Why ultrasound?

- Low transmit power [Nelson '10]

- No danger or side-effects

э

• • • • • • • • • • • •

э

э

э

(日)

э

(日)

э

10 / 40

(日)

э

• • • • • • • • • • • •

3

• • • • • • • • • • • •

э

э

э

э

Image: A mathematical states and a mathem

э

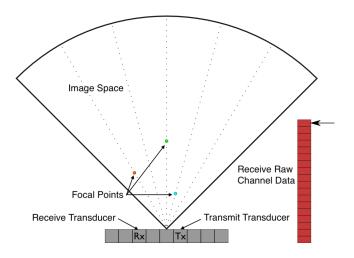

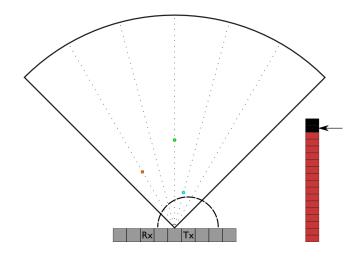

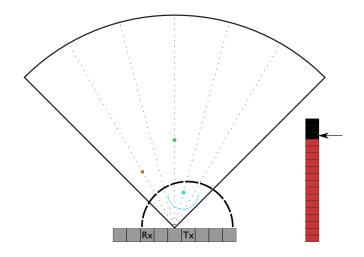

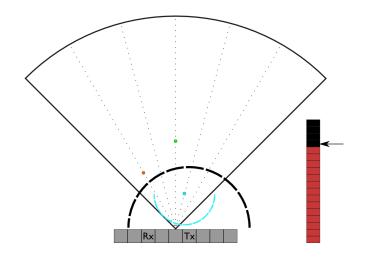

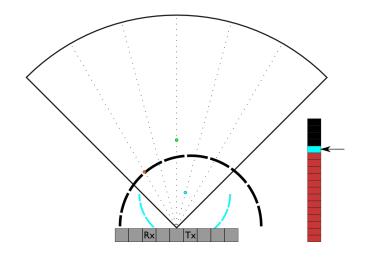

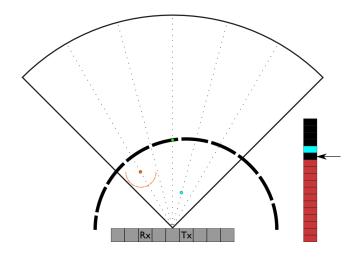

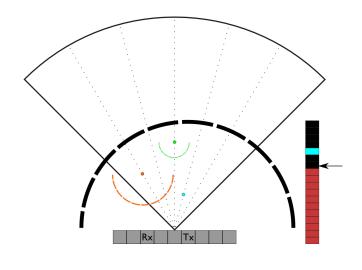

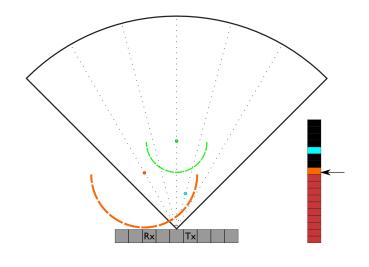

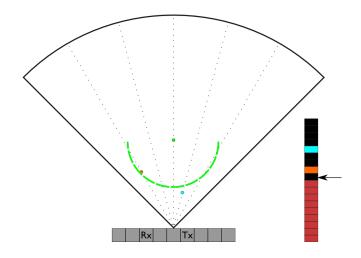

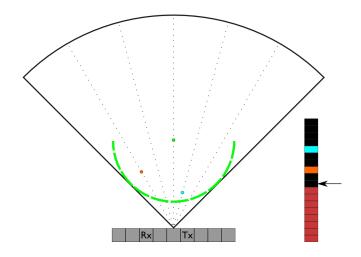

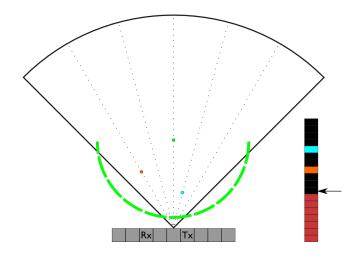

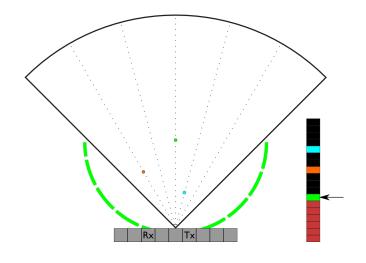

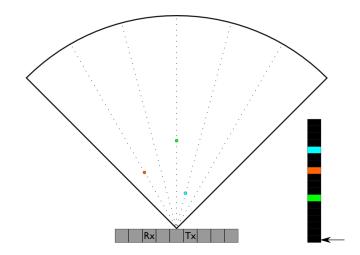

Each transducer stores an array of raw received data

University of Michigan

EECS 570 Programming Assignment 1

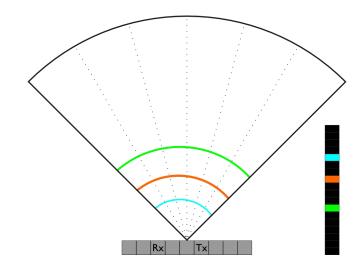

Image reconstructed from data based on round-trip delay

University of Michigan

EECS 570 Programming Assignment 1

January 14, 2022 19 / 40

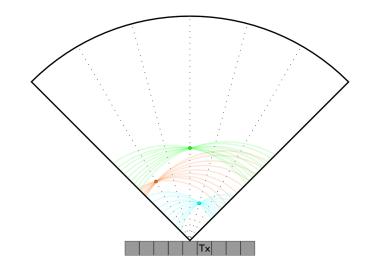

Images from each transducer combined to produce the full frame

University of Michigan

EECS 570 Programming Assignment 1

January 14, 2022 20 / 40

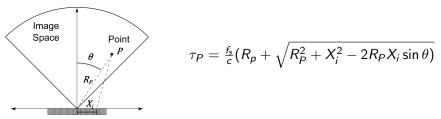

# **Delay Index Calculation**

• Iterate through all image points for each transducer and calculate delay index  $\tau_P$

• Often done with lookup tables (LUTs) instead

• 50 GB LUT required for target 3D system

(4) (日本)

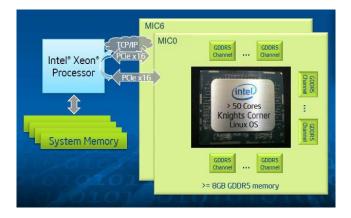

### Intel Xeon Phi Coprocessors and the MIC Architecture

University of Michigan

EECS 570 Programming Assignment 1

January 14, 2022

(日)

22 / 40

э

# Intex Xeon Processors and the MIC Architecture

Multi-core Intel Xeon processor

- C/C++/Fortran; OpenMP/MPI

- Standard Linux OS

- Up to 768 GB of DDR3 RAM

- $\geq$  12 cores/socket pprox 3 GHz

- 2-way hyper-threading

- 256-bit AVX vectors

Many-core Intel Xeon Phi coprocessor

- C/C++/Fortran; OpenMP/MPI

- Special Linux  $\mu$ OS distribution

- 6-16 GB cached GDDR5 RAM

- 57-61 cores at pprox 1 GHz

- 4-way hyper-threading

- 512-bit IMCI vectors

# Xeon Phi Programming Models

#### • Native coprocessor applications

- Compile with -mmic

- Run with micnativeloadex or scp+ssh

- The way to go for MPI applications without offload

#### Explicit offload

- Functions, global variables require \_\_attribute\_\_((target(mic)))

- Initiate offload, data marshalling with #pragma offload

- Only bitwise-copyable data can be shared

- Clusters and multiple coprocessors

- #pragma offload target(mic:i)

- Use threads to offload to multiple coprocessors

- Run native MPI applications

# Xeon Phi Programming Models

#### • Native coprocessor applications

- Compile with -mmic

- Run with micnativeloadex or scp+ssh

- The way to go for MPI applications without offload

#### Explicit offload

- Functions, global variables require \_\_attribute\_\_((target(mic)))

- Initiate offload, data marshalling with #pragma offload

- Only bitwise-copyable data can be shared

- Clusters and multiple coprocessors

- #pragma offload target(mic:i)

- Use threads to offload to multiple coprocessors

- Run native MPI applications

January 14, 2022

25 / 40

### Native Execution

```

Example ("Hello World" application)

#include <stdio.h>

#include <unistd.h>

int main() {

printf("Hello world! I have %ld logical cores.\n",

sysconf(_SC_NPROCESSORS_ONLN ));

}

```

#### Example (compile and run on host)

```

user@host% icc -o hello hello.c

user@host% ./hello

Hello world! I have 32 logical cores.

user@host% _

```

### Native Execution

Compile and run the same code on the coprocessor in native mode:

```

Example (compile and run on coprocessor)

```

user@host% icc -o hello.mic hello.c -mmic user@host% micnativeloadex hello.mic -t 300 -d 0 Hello world! I have 240 logical cores. user@host% \_

- Use -mmic to produce executable for MIC architecture

- Use micnativeloadex to run the executable on the coprocessor

- Native MPI applications work the same way (need Intel MPI library)

< ロ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ >

Introduction to POSIX Threads

### Introduction to POSIX Threads

• What is a thread?

3

イロト イボト イヨト イヨト

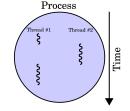

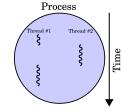

## Introduction to POSIX Threads

- What is a thread?

- Independently executing stream of instructions

- Schedulable unit of execution for the operating system

A D F A B F A B F A B

## Introduction to POSIX Threads

- What is a thread?

- Independently executing stream of instructions

- Schedulable unit of execution for the operating system

- Pthreads the POSIX threading interface

- Provides system calls to create and synchronize threads

- Communication happens strictly through shared memory

- Specifically, using *pointers* to shared data

# Creating Threads

Pthread create function signature int pthread\_create(pthread\_t\*, const pthread\_attr\_t\*, void\* (\*)(void\*), void\*);

#### Example

# Creating Threads

Pthread create function signature int pthread\_create(pthread\_t\*, const pthread\_attr\_t\*, void\* (\*)(void\*), void\*);

#### Example

errcode = pthread\_create(&thread\_obj, &thread\_attr, &thread\_func, &func\_arg);

- thread\_obj is the thread object or handle (used to halt, etc.)

- thread\_attr specifies various attributes

- Default values obtained by passing a NULL pointer

- thread\_func is a pointer to the function to be run (takes and returns) void\*)

- func\_arg is a pointer to an argument that is passed to thread\_func when it starts

- errorcode is be set to non-zero if pthread\_create() fails 1 = > = 990

29 / 40

# Shared Data and Threads

- Objects allocated on the heap may be shared (by passing pointers)

- Variables on the stack are private; passing pointers to those between threads can lead to problems

- How to pass multiple arguments to a thread?

- One way: create a "thread data" struct

- Pass a pointer to the struct object to each thread

#### Example

```

typedef struct _thread_data_t{

int thread_id, value;

char* message;

} thread_data_t;

...

thread_data_t td;

/* initialize elements of thread_data_t object */

pthread_create(&thread_obj, NULL, thread_func, &td);

...

```

# Joining Threads

```

Pthread join function signature

int pthread_join(pthread_t thread_obj,

void** retval);

```

#### Example

```

errcode = pthread_join(thread_obj, NULL);

```

# Joining Threads

```

Pthread join function signature

int pthread_join(pthread_t thread_obj,

void** retval);

```

#### Example

```

errcode = pthread_join(thread_obj, NULL);

```

- The function waits for the thread object thread\_obj to terminate

- If retval is not NULL, then pthread\_join() copies the exit status

- errcode is set to non-zero if pthread\_join() fails

## Multithreaded "Hello World"

```

Example ("Hello World" application)

void* func(void* arg) {

printf("Hello World!\n");

return NULL;

}

int main() {

pthread_t threads[2]; int i;

for(i = 0: i < 2: ++i) {

pthread_create(&threads[i], NULL, func, NULL);

}

for(i = 0; i < 2; ++i) {</pre>

pthread_join(threads[i], NULL);

}

```

• Compile using gcc -pthread

#### Let's run a "Hello World" program through the Phi!

University of Michigan

EECS 570 Programming Assignment 1

January 14, 2022 33 / 40

3

イロト イボト イヨト イヨト

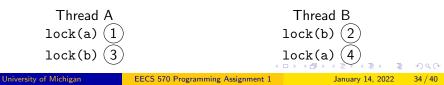

## Synchronization Primitives I - Mutexes

- Mutual exclusion (mutex), a.k.a. locks

- Threads working mostly independently may need to access shared data

```

mutex *m = alloc_and_init();

acquire(m);

/* modify shared data */

release(m);

```

- e.g. Producer-consumer model

- Coke machine example: single person refills coke (producer), multiple people buy coke (consumer)

- Is there any problem with holding multiple mutexes?

## Synchronization Primitives I - Mutexes

- Mutual exclusion (mutex), a.k.a. locks

- Threads working mostly independently may need to access shared data

```

mutex *m = alloc_and_init();

acquire(m);

/* modify shared data */

release(m);

```

- e.g. Producer-consumer model

- Coke machine example: single person refills coke (producer), multiple people buy coke (consumer)

- Multiple mutexes may be held, but may lead to deadlock

## Synchronization Primitives I - Mutexes

#### Example (mutex creation)

```

#include <pthread.h>

pthread_mutex_t myMutex = PTHREAD_MUTEX_INITIALIZER;

pthread_mutex_init(&myMutex, NULL);

```

#### Example (mutex usage)

pthread\_mutex\_lock(&myMutex);

/\* access critical data \*/

pthread\_mutex\_unlock(&myMutex);

#### Example (mutex deallocation)

pthread\_mutex\_destroy(&myMutex);

(日)

## Synchronization Primitives II - Barriers

- A barrier object allows global synchronization between threads

- Wait for all threads to reach a point in computation

- After that, launch all threads simultaneously to continue execution

- Common when running multiple copies of the same function in parallel

- Single Program Multiple Data (SPMD) paradigm

- Simple use of barriers: all threads hit the same barrier

```

work_on_my_problem();

barrier_woit();

```

```

barrier_wait();

```

```

get_data_from_others();

```

```

barrier_wait();

```

One thread waits for two other threads to arrive at the barrier

• More complicated: barriers

on branches (or loops)

if(thread\_id % 2 == 0) {

work\_on\_problem\_1();

}

### Synchronization Primitives II - Barriers

#### Example (static barrier initialization with 3 threads)

pthread\_barrier\_t barrier = PTHREAD\_BARRIER\_INITIALIZER(3);

#### Example (dynamic barrier initialization with 3 threads)

pthread\_barrier\_t myBarrier;

pthread\_barrier\_init(&myBarrier, NULL, 3);

#### Example (barrier usage)

pthread\_barrier\_wait(&myBarrier);

#### Example (barrier deallocation)

pthread\_barrier\_destroy(&myBarrier);

(I) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1))

## Pthreads Summary

- Initialize every pthread object you use

- e.g. pthread\_mutex\_t, pthread\_barrier\_t

- Do not spawn threads for small jobs

- Thread creation overhead is non-trivial

- Too many threads can lead to performance degradation (Amdahl's law)

- Work through a tutorial!

- https://computing.llnl.gov/tutorials/pthreads/

- http://pages.cs.wisc.edu/~travitch/pthreads\_primer.html

# Questions?

University of Michigan

EECS 570 Programming Assignment 1

January 14, 2022

э

39 / 40

イロト イポト イヨト イヨト

Programming Assignment I due 2/4 11:59 PM on Canvas

40 / 40

イロト 不得 トイラト イラト 一日

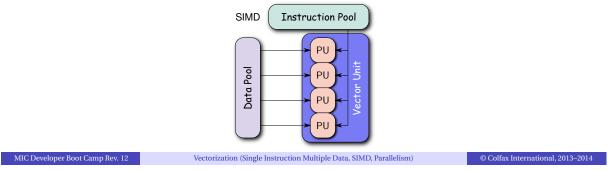

## Vectorization (Single Instruction Multiple Data, SIMD, Parallelism)

MIC Developer Boot Camp Rev. 12

Vectorization (Single Instruction Multiple Data, SIMD, Parallelism)

© Colfax International, 2013–2014

## **SIMD Operations**

## SIMD — Single Instruction Multiple Data

#### Scalar Loop

SIMD Loop

1 for (i = 0; i < n; i++) 2 A[i] = A[i] + B[i];

## Each SIMD addition operator acts on 4 numbers at a time.

## Instruction Sets in Intel Architectures

| Instruction | Year and Intel Processor   | Vector    | Packed Data Types                |

|-------------|----------------------------|-----------|----------------------------------|

| Set         |                            | registers |                                  |

| MMX         | 1997, Pentium              | 64-bit    | 8-, 16- and 32-bit integers      |

| SSE         | 1999, Pentium III          | 128-bit   | 32-bit single precision FP       |

| SSE2        | 2001, Pentium 4            | 128-bit   | 8 to 64-bit integers; SP & DP FP |

| SSE3-SSE4.2 | 2004 - 2009                | 128-bit   | (additional instructions)        |

| AVX         | 2011, Sandy Bridge         | 256-bit   | le and double precision FP       |

| AVX2        | 2013, <mark>Haswell</mark> | 256-bit   | gers, additional instructions    |

| IMCI        | 2012, Knights Corner       | 512-bit   | 32- and 64-bit integers;         |

|             |                            |           | single & double precision FP     |

| AVX-512     | (future) Knights Landing   | 512-bit   | 32- and 64-bit integers;         |

|             |                            |           | single & double precision FP     |

MIC Developer Boot Camp Rev. 12

Vectorization (Single Instruction Multiple Data, SIMD, Parallelism)

© Colfax International, 2013–2014

### **Explicit Vectorization: Compiler Intrinsics IMCI Intrinsics**

| SSE2 Intrinsics |  |

|-----------------|--|

|                 |  |

| 1 | for (int i=0; i <n; i+="4)" th="" {<=""></n;> |

|---|-----------------------------------------------|

| 2 | <pre>m128 Avec=_mm_load_ps(A+i);</pre>        |

| 3 | <pre>m128 Bvec=_mm_load_ps(B+i);</pre>        |

| 4 | <pre>Avec=_mm_add_ps(Avec, Bvec);</pre>       |

| 5 | _mm_store_ps(A+i, Avec);                      |

| 6 | }                                             |

for (int i=0; i<n; i+=16) { \_\_m512 Avec=\_mm512\_load\_ps(A+i); \_\_m512 Bvec=\_mm512\_load\_ps(B+i); Avec=\_mm512\_add\_ps(Avec, Bvec); \_mm512\_store\_ps(A+i, Avec); |}

- The arrays float A[n] and float B[n] are aligned on a 16-byte (SSE2) and 64-byte (IMCI) boundary

- n is a multiple of 4 for SSE and a multiple of 16 for IMCI

- Variables Avec and Bvec are

- $128 = 4 \times \text{sizeof(float)}$  bits in size for SSE2 and

- $512 = 16 \times \text{sizeof(float)}$  bits for the Intel Xeon Phi architecture

1

2

3

4

5

6

```

MIC Developer Boot Camp Rev. 12

Vectorization (Single Instruction Multiple Data, SIMD, Parallelism)

```

© Colfax International, 2013–2014