# Section 17 Assertions

# 17.1 Introduction (informative)

SystemVerilog adds features to specify assertions of a system. An assertion specifies a behavior of the system. Assertions are primarily used to validate the behavior of a design. In addition, assertions can be used to provide functional coverage and generate input stimulus for validation.

There are two kinds of assertions: concurrent and immediate.

- Immediate assertions follow simulation event semantics for their execution and are executed like a statement in a procedural block. Immediate assertions are primarily intended to be used with simulation.

- Concurrent assertions are based on clock semantics and use sampled values of variables. One of the goals of SystemVerilog assertions is to provide a common semantic meaning for assertions so that they can be used to drive various design and verification tools. Many tools, such as formal verification tools, evaluate circuit descriptions using cycle-based semantics, which typically relies on a clock signal or signals to drive the evaluation of the circuit. Any timing or event behavior between clock edges is abstracted away. Concurrent assertions incorporate these clock semantics. While this approach generally simplifies the evaluation of a circuit description, there are a number of scenarios under which this cycle-based evaluation provides different behavior from the standard event-based evaluation of SystemVerilog.

This section describes both types of assertions.

# 17.2 Immediate assertions

The immediate assertion statement is a test of an expression performed when the statement is executed in the procedural code. The expression is non-temporal and is interpreted the same way as an expression in the condition of a procedural if statement. That is, if the expression evaluates to X, Z or 0, then it is interpreted as being false and the assertion is said to fail. Otherwise, the expression is interpreted as being true and the assertion is said to pass.

The immediate **assert** statement is a *statement\_item* and can be specified anywhere a procedural statement is specified.

| procedural_assertion_statement ::=                                               | // from Annex A.6.10 |                     |

|----------------------------------------------------------------------------------|----------------------|---------------------|

| <br>  immediate_assert_statement                                                 |                      |                     |

| <pre>immediate_assert_statement ::=     assert ( expression ) action_block</pre> |                      |                     |

| action_block ::=<br>statement _or_null<br>  [ statement ] else statement         |                      | // from Annex A.6.3 |

## Syntax 17-1—Immediate assertion syntax (excerpt from Annex A)

The *action\_block* specifies what actions are taken upon success or failure of the assertion. The statement associated with the success of the assert statement is the first statement. It is called the *pass statement* and is executed if the expression evaluates to true. The pass statement can, for example, record the number of successes for a coverage log, but can be omitted altogether. If the pass statement is omitted, then no user-specified action is taken when the assert expression is true. The statement associated with **else** is called a *fail statement* and is executed if the expression evaluates to false. The **else** statement can also be omitted. The action block is executed immediately after the evaluation of the assert expression.

The optional statement label (identifier and colon) creates a named block around the assertion statement (or any other SystemVerilog statement) and can be displayed using the %m format specification.

```

assert_foo : assert(foo) $display("%m passed"); else $display("%m failed");

```

Note: The assertion control system tasks are described in Section 23.9.

Since the assertion is a statement that something must be true, the failure of an assertion shall have a severity associated with it. By default, the severity of an assertion failure is *error*. Other severity levels can be specified by including one of the following severity system tasks in the fail statement:

- \$fatal is a run-time fatal.

- \$error is a run-time error.

- \$warning is a run-time warning, which can be suppressed in a tool-specific manner.

- \$info indicates that the assertion failure carries no specific severity.

The syntax for these system tasks is shown in Section 23.8.

If an assertion fails and no **else** clause is specified, the tool shall, by default, call \$error, unless a tool-specific option, such as a command-line option, is enabled to suppress the failure.

All of these severity system tasks shall print a tool-specific message indicating the severity of the failure, and specific information about the specific failure, which shall include the following information:

- The file name and line number of the assertion statement.

- The hierarchical name of the assertion, if it is labeled, or the scope of the assertion if it is not labeled.

For simulation tools, these tasks shall also include the simulation run-time at which the severity system task is called.

Each system task can also include additional user-specified information using the same format as the Verilog \$display.

If more than one of these system tasks is included in the **else** clause, then each shall be executed as specified.

If the severity system task is executed at a time other than when the assertion fails, the actual failure time of the assertion can be recorded and displayed programmatically. For example:

```

time t;

always @(posedge clk)

if (state == REQ)

assert (req1 || req2)

else begin

t = $time;

#5 $error("assert failed at time %0t",t);

end

```

If the assertion fails at time 10, the error message shall be printed at time 15, but the user-defined string printed shall be "assert failed at time 10".

The display of messages of warning and info types can be controlled by a tool-specific option, such as a command-line option.

Since the fail statement, like the pass statement, is any legal SystemVerilog procedural statement, it can also be used to signal a failure to another part of the testbench.

assert (myfunc(a,b)) count1 = count + 1; else ->event1;

assert (y == 0) else flag = 1;

#### 17.3 Concurrent assertions overview

Concurrent assertions describe behavior that spans over time. Unlike immediate assertions, the evaluation model is based on a clock such that a concurrent assertion is evaluated only at the occurrence of a clock tick. The values of variables used in the evaluation are the sampled values. This way, a predictable result can be obtained from the evaluation, regardless of the simulator's internal mechanism of ordering events and evaluating events. This model of execution also corresponds to the synthesis model of hardware interpretation from an RTL description.

The values of variables used in assertions are sampled in the Preponed region of a time slot and the assertions are evaluated during the Observe region. This is explained in Section 14, Scheduling Semantics.

The timing model employed in a concurrent assertion specification is based on clock ticks and uses a generalized notion of clock cycles. The definition of a clock is explicitly specified by the user and can vary from one expression to another.

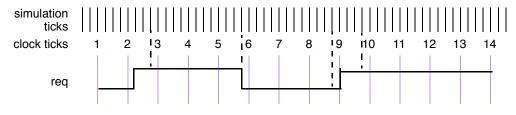

A *clock tick* is an atomic moment in time that itself spans no duration of time. A clock shall tick only once at any simulation time and the sampled values for that simulation time are used for evaluation of concurrent assertions. In an assertion, the sampled value is the only valid value of a variable at a clock tick. Figure 17-1 shows the values of a variable as the clock progresses. The value of signal req is low at clock ticks 1 and 2. At clock tick 3, the value is sampled as high and remains high until clock tick 6. The sampled value of variable req at clock tick 6 is low and remains low until clock tick 10. Notice that the simulation value transitions to high at clock tick 9. However, the sampled value at clock tick 9 is low.

Figure 17-1 — Sampling a variable on simulation ticks

An expression used in an assertion is always tied to a clock definition. The sampled values are used to evaluate value change expressions or boolean subexpressions that are required to determine a match of a sequence.

Note:

- It is important to ensure that the defined clock behavior is glitch free. Otherwise, wrong values can be sampled.

- If a variable that appears in the expression for clock also appears in an expression with an assertion, the values of the two usages of the variable can be different. The current value of the variable is used in the clock expression, while the sampled value of the variable is used within the assertion.

The clock expression that controls evaluation of a sequence can be more complex than just a single signal name. Expressions such as (clk && gating\_signal) and (clk **iff** gating\_signal) can be used to represent a gated clock. Other more complex expressions are possible. However, in order to ensure proper behavior of the system and conform as closely as possible to truly cycle-based semantics, the signals in a clock expression must be glitch-free and should only transition once at any simulation time.

An example of a concurrent assertion is:

```

base_rule1: assert property (cont_prop(rst,in1,in2)) pass_stat else fail_stat;

```

The keyword **property** distinguishes a concurrent assertion from an immediate assertion. The syntax of concurrent assertions is discussed in 17.13.

## **17.4 Boolean expressions**

The expressions used in sequences are evaluated over sampled values of the variables that appear in the expressions. The outcome of the evaluation of an expression is boolean and is interpreted the same way as an expression is interpreted in the condition of a procedural if statement. That is, if the expression evaluates to x, z, or 0, then it is interpreted as being false. Otherwise, it is true.

There are certain restrictions on the expressions that can appear in concurrent assertions. The restrictions on operand types, variables, and operators are specified in the following sections.

Expressions are allowed to include function calls, but certain semantic restrictions are imposed.

- Functions that appear in expressions cannot contain output or ref arguments (const ref are allowed).

- Functions should be automatic (or preserve no state information) and have no side effects.

#### 17.4.1 Operand types

The following types are not allowed:

- non-integer types (shortreal, real and realtime)

- string

- event

- chandle

- class

- associative arrays

- dynamic arrays

Fixed size arrays, packed or unpacked, can be used as a whole or as part selects or as indexed bit or part selects. The indices can be constants, parameters, or variables.

The following example shows some possible forms of comparison of members of structures and unions:

```

typedef int [4] array;

typedef struct { int a, b, c,d } record;

union { record r; array a; } p, q;

```

The following comparisons are legal in expressions:

p.a == q.a

and

p.r == q.r

The following example provides further illustration of the use of arrays in expressions.

logic [7:0] arrayA [0:15], arrayB[0:15];

The following comparisons are legal:

arrayA == arrayB;

```

arrayA != arrayB;

arrayA[i] >= arrayB[j];

arrayB[i][j+:2] == arrayA[k][m-:2];

(arrayA[i] & (~arrayB[j])) == 0;

```

## 17.4.2 Variables

The variables that can appear in expressions must be static design variables or function calls returning values of types described in Section 17.4.1. Static variables declared in programs, interfaces or clocking blocks can also be accessed. If a reference is to a static variable declared in a task, that variable is sampled as any other variable, independent of calls to the task.

## 17.4.3 Operators

All operators that are valid for the types described in Section 17.4.1 are allowed with the exception of assignment operators and increment and decrement operators. SystemVerilog includes the C assignment operators, such as +=, and the C increment and decrement operators, ++ and --. These operators cannot be used in expressions that appear in assertions. This restriction prevents side effects.

```

// from Annex A.2.10

sequence_expr ::=

cycle_delay_range sequence_expr { cycle_delay_range sequence_expr }

sequence_expr cycle_delay_range sequence_expr { cycle_delay_range sequence_expr }

expression_or_dist [ boolean_abbrev ]

| ( expression_or_dist {, sequence_match_item } ) [ boolean_abbrev ]

| sequence instance [ sequence abbrev ]

[ (sequence_expr {, sequence_match_item } ) [ sequence_abbrev ]

| sequence_expr and sequence_expr

sequence_expr intersect sequence_expr

| sequence expr or sequence expr

i first_match ( sequence_expr {, sequence_match_item} )

expression_or_dist throughout sequence_expr

| sequence_expr within sequence_expr

l clocking_event sequence_expr

cycle_delay_range ::=

## integral_number

| ## identifier

| ## (constant expression)

| ## [ cycle_delay_const_range_expression ]

sequence match item ::=

operator_assignment

l inc or dec expression

| subroutine_call

sequence instance ::=

ps_sequence_identifier [ ( [ actual_arg_list ] ) ]

actual arg list ::=

actual_arg_expr { , actual_arg_expr }

. formal_identifier ( actual_arg_expr ) { ,. formal_identifier ( actual_arg_expr ) }

actual_arg_expr ::=

event_expression

1 $

boolean abbrev ::=

consecutive_repetition

I non consecutive repetition

| goto_repetition

sequence abbrev ::= consecutive repetition

consecutive_repetition ::= [* const_or_range_expression ]

non_consecutive_repetition ::= [= const_or_range_expression ]

goto_repetition ::= [-> const_or_range_expression ]

const or range expression ::=

constant_expression

l cycle_delay_const_range_expression

cycle delay const range expression ::=

constant_expression : constant_expression

| constant expression : $

expression_or_dist ::= expression [ dist { dist_list } ]

```

Syntax 17-2—Sequence syntax (excerpt from Annex A)

#### SystemVerilog 3.1a

Properties are often constructed out of sequential behaviors. The **sequence** feature provides the capability to build and manipulate sequential behaviors. The simplest sequential behaviors are linear. A *linear sequence* is a finite list of SystemVerilog boolean expressions in a linear order of increasing time. The linear sequence is said to match along a finite interval of consecutive clock ticks provided the first boolean expression evaluates to true at the first clock tick, the second boolean expression evaluates to true at the second clock tick, and so forth, up to and including the last boolean expression evaluating to true at the last clock tick. A single boolean expression is an example of a simple linear sequence, and it matches at a single clock tick provided the boolean expression evaluates to true at that clock tick.

More complex sequential behaviors are described by SystemVerilog sequences. A sequence is a regular expression over the SystemVerilog boolean expressions that concisely specifies a set of zero, finitely many, or infinitely many linear sequences. If at least one of the linear sequences from this set matches along a finite interval of consecutive clock ticks, then the sequence is said to match along that interval.

A property may involve checking of one or more sequential behaviors beginning at various times. An attempted evaluation of a sequence is a search for a match of the sequence beginning at a particular clock tick. To determine whether such a match exists, appropriate boolean expressions are evaluated beginning at the particular clock tick and continuing at each successive clock tick until either a match is found or it is deduced that no match can exist.

Sequences can be composed by concatenation, analogous to a concatenation of lists. The concatenation specifies a delay, using ##, from the end of the first sequence until the beginning of the second sequence.

The following is the syntax for sequence concatenation.

| sequence_expr ::=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | // from Annex A.2.10 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| cycle_delay_range sequence_expr { cycle_delay_range sequence_expr }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

| <pre>l sequence_expr cycle_delay_range sequence_expr { cycle_expr { cycle_</pre> | uence_expr }         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| cycle_delay_range ::=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| ## integral_number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| <b>##</b> identifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |

| <pre>## ( constant_expression )</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| ## [ cycle_delay_const_range_expression ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

| cycle_delay_const_range_expression ::=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

| constant_expression : constant_expression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

| constant_expression : \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

Syntax 17-3—Sequence concatenation syntax (excerpt from Annex A)

In this syntax:

- *constant\_expression* is computed at compile time and must result in an integer value.

- *constant\_expression* can only be 0 or greater.

- The \$ token is used to indicate the end of simulation. For formal verification tools, \$ is used to indicate a finite, unbounded, range.

- When a range is specified with two expressions, the second expression must be greater or equal to the first expression.

The context in which a sequence occurs determines when the sequence is evaluated. The first expression in a sequence is checked at the first occurrence of the clock tick at or after the expression that triggered evaluation of the sequence. Each successive element (if any) in the sequence is checked at the next subsequent occurrence of the clock.

A ## followed by a number or range specifies the delay from the current clock tick to the beginning of the

sequence that follows. The delay ##1 indicates that the beginning of the sequence that follows is one clock tick later than the current clock tick. The delay ##0 indicates that the beginning of the sequence that follows is at the same clock tick as the current clock tick.

When used as a concatenation between two sequences, the delay is from the end of the first sequence to the beginning of the second sequence. The delay ##1 indicates that the beginning of the second sequence is one clock tick later than the end of the first sequence. The delay ##0 indicates that the beginning of the second sequence is at the same clock tick as the end of the first sequence.

The following are examples of delay expressions. 'true is a boolean expression that always evaluates to true and is used for visual clarity. It can be defined as:

```

`define true 1

##0 a // means a

##1 a // means `true ##1 a

##2 a // means `true ##1 `true ##1 a

##[0:3]a // means (a) or (`true ##1 a) or (`true ##1 `true ##1 a)

a ##2 b // means a ##1 `true ##1 b

```

The sequence:

req ##1 gnt ##1 !req

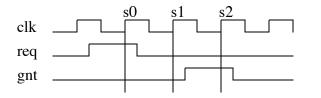

specifies that req be true on the current clock tick, gnt shall be true on the first subsequent tick, and req shall be false on the next clock tick after that. The ##1 operator specifies one clock tick separation. A delay of more than one clock tick can be specified, as in:

req ##2 gnt

This specifies that req shall be true on the current clock tick, and gnt shall be true on the second subsequent clock tick, as shown in Figure 17-2.

Figure 17-2 — Concatenation of sequences

The following specifies that signal b shall be true on the Nth clock tick after signal a:

a ##N b // check b on the Nth sample

To specify a concatenation of overlapped sequences, where the end point of one sequence coincides with the start of the next sequence, a value of 0 is used, as shown below.

a ##1 b ##1 c // first sequence seq1

d ##1 e ##1 f // second sequence seq2

(a ##1 b ##1 c) ##0 (d ##1 e ##1 f) // overlapped concatenation

In the above example, c must be true at the endpoint of sequence seq1, and d must be true at the start of sequence seq2. When concatenated with 0 clock tick delay, c and d must be true at the same time, resulting in a concatenated sequence equivalent to:

SystemVerilog 3.1a

a ##1 b ##1 c&&d ##1 e ##1 f

It should be noted that no other form of overlapping between the sequences can be expressed using the concatenation operation.

In cases where the delay can be any value in a range, a time window can be specified as follows:

req ##[4:32] gnt

In the above case, signal req must be true at the current clock tick, and signal gnt must be true at some clock tick between the 4th and the 32nd clock tick after the current clock tick.

The time window can extend to a finite, but unbounded, range by using \$ as in the example below.

req ##[4:\$] gnt

A sequence can be unconditionally extended by concatenation with 'true.

a ##1 b ##1 c ##3 `true

After satisfying signal c, the sequence length is extended by 3 clock ticks. Such adjustments in the length of sequences can be required when complex sequences are constructed by combining simpler sequences.

#### 17.6 Declaring sequences

A sequence can be declared in

- a module

- an interface

- a program

- a clocking block

- a package

- a compilation-unit scope

Sequences are declared using the following syntax.:

```

// from Annex A.2.10

concurrent assertion item declaration ::=

I sequence declaration

sequence declaration ::=

sequence sequence_identifier [ ( [ list_of_formals ] ) ];

{ assertion_variable_declaration }

sequence expr;

endsequence [: sequence identifier]

sequence instance ::=

ps_sequence_identifier [ ( [ actual_arg_list ] ) ]

actual arg list ::=

actual arg expr {, actual arg expr }

. formal_identifier ( actual_arg_expr ) { ,. formal_identifier ( actual_arg_expr ) }

actual arg expr ::=

event_expression

1 $

assertion_variable_declaration ::=

data type list of variable identifiers;

```

Syntax 17-4—Declaring sequence syntax (excerpt from Annex A)

The *clocking\_event* specifies the clock for the sequence.

A sequence is declared with optional formal arguments. When a sequence is instantiated, actual arguments can be passed to the sequence. The sequence gets expanded with the actual arguments by replacing the formal arguments with the actual arguments. Semantic checks are performed to ensure that the expanded sequence with the actual arguments is legal.

An actual argument can replace an:

- identifier

- expression

- event control expression

- upper range as \$

Note that variables used in a sequence that are not formal arguments to the sequence are resolved according to the scoping rules from the scope in which the sequence is declared.

```

sequence s1;

@(posedge clk) a ##1 b ##1 c;

endsequence

sequence s2;

@(posedge clk) d ##1 e ##1 f;

endsequence

sequence s3;

@(negedge clk) g ##1 h ##1 i;

endsequence

```

In this example, sequences s1 and s2 are evaluated on successive posedge events of c1k. The sequence s3 is evaluated on successive negedge events of c1k.

Another example of sequence declaration, which includes arguments is shown below:

SystemVerilog 3.1a

```

sequence s20_1(data,en);

(!frame && (data==data_bus)) ##1 (c_be[0:3] == en);

endsequence

```

Sequence s20\_1 does not specify a clock. In this case, a clock would be inherited from some external source, such as a **property** or an **assert** statement. A sequence can be referred to by its name. A hierarchical name can be used, consistent with the SystemVerilog naming conventions. A sequence can be referenced in a **property**, an **assert** statement, or a **cover** statement.

To use a named sequence as a subsequence of another sequence, simply reference its name. The evaluation of a sequence that references a named sequence is performed in the same way as if the named sequence was contained as a lexical part of the referencing sequence, with the formal arguments of the named sequence replaced by the actual ones and the remaining variables in the named sequence resolved according to the scope of the declaration of the named sequence. An example is shown below:

```

sequence s;

a ##1 b ##1 c;

endsequence

sequence rule;

@(posedge sysclk)

trans ##1 start_trans ##1 s ##1 end_trans;

endsequence

```

Sequence rule in the preceding example is equivalent to:

```

sequence rule;

@(posedge sysclk)

trans ##1 start_trans ##1 a ##1 b ##1 c ##1 end_trans ;

endsequence

```

Any form of syntactic cyclic dependency of the sequence names is disallowed. The example below illustrates an illegal dependency of s1 on s2 and s2 on s1, because it creates a cyclic dependency.

```

sequence s1;

@(posedge sysclk) (x ##1 s2);

endsequence

sequence s2;

@(posedge sysclk) (y ##1 s1);

endsequence

```

## 17.7 Sequence operations

#### 17.7.1 Operator precedence

Operator precedence and associativity are listed in Table 17-1, below. The highest precedence is listed first.

| SystemVerilog expression operators | Associativity |

|------------------------------------|---------------|

| [*] [=] [->]                       |               |

| ##                                 | left          |

| throughout                         | right         |

| within                             | left          |

| Table 17-1: Operator precedence and associativity | Table 17-1: 0 | <b>Operator</b> | precedence | and | associativity |

|---------------------------------------------------|---------------|-----------------|------------|-----|---------------|

|---------------------------------------------------|---------------|-----------------|------------|-----|---------------|

| intersect | left |

|-----------|------|

| and       | left |

| or        | left |

#### 17.7.2 Repetition in sequences

Following is the syntax for sequence repetition.

| sequence_expr ::=                                                                                                                                                                                                                                | // from Annex A.2.10 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <pre>     expression_or_dist [ boolean_abbrev ]     l ( expression_or_dist {, sequence_match_item } ) [ boolean_abbrev ]     l sequence_instance [ sequence_abbrev ]     l ( sequence_expr {, sequence_match_item} ) [ sequence_abbrev ]  </pre> |                      |

| boolean_abbrev ::=<br>consecutive_repetition<br>  non_consecutive_repetition<br>  goto_repetition                                                                                                                                                |                      |

| sequence_abbrev ::= consecutive_repetition                                                                                                                                                                                                       |                      |

| consecutive_repetition ::= [* const_or_range_expression ]                                                                                                                                                                                        |                      |

| non_consecutive_repetition ::= [= const_or_range_expression ]                                                                                                                                                                                    |                      |

| <pre>goto_repetition ::= [-&gt; const_or_range_expression ]</pre>                                                                                                                                                                                |                      |

| <pre>const_or_range_expression ::=     constant_expression</pre>                                                                                                                                                                                 |                      |

| <pre>cycle_delay_const_range_expression ::=     constant_expression : constant_expression     l constant_expression : \$</pre>                                                                                                                   |                      |

Syntax 17-5—Sequence repetition syntax (excerpt from Annex A)

The number of iterations of a repetition can either be specified by exact count or be required to fall within a finite range. If specified by exact count, then the number of iterations is defined by a non-negative integer constant expression. If required to fall within a finite range, then the minimum number of iterations is defined by a non-negative integer constant expression and the maximum number of iterations is either defined by a non-negative integer constant expression or is \$, indicating a finite, but unbounded maximum.

If both the minimum and maximum numbers of iterations are defined by non-negative integer constant expressions, then the minimum number must be less than or equal to the maximum number.

Three kinds of repetition are provided:

- consecutive repetition ([\*): Consecutive repetition specifies finitely many iterative matches of the operand sequence, with a delay of one clock tick from the end of one match to the beginning of the next. The overall repetition sequence matches at the end of the last iterative match of the operand.

- goto repetition ( [-> ): Goto repetition specifies finitely many iterative matches of the operand boolean expression, with a delay of one or more clock ticks from one match of the operand to the next successive

match and no match of the operand strictly in between. The overall repetition sequence matches at the last iterative match of the operand.

— non-consecutive repetition ( [= ): Non-consecutive repetition specifies finitely many iterative matches of the operand boolean expression, with a delay of one or more clock ticks from one match of the operand to the next successive match and no match of the operand strictly in between. The overall repetition sequence matches at or after the last iterative match of the operand, but before any later match of the operand.

The effect of consecutive repetition of a subsequence within a sequence can be achieved by explicitly iterating the subsequence, as:

a ##1 b ##1 b ##1 b ##1 c

Using the consecutive repetition operator [\*3], which indicates 3 iterations, this sequential behavior is specified more succinctly:

a ##1 b [\*3] ##1 c

A consecutive repetition specifies that the operand sequence must match a specified number of times. The consecutive repetition operator [\*N] specifies that the operand sequence must match N times in succession. For example:

a [\*3] means a ##1 a ##1 a

Using 0 as the repetition number, an empty sequence results, as:

a [\*0]

An *empty sequence* is one that does not match over any positive number of clocks. The following rules apply for concatenating sequences with empty sequences. An empty sequence is denoted as *empty* and a sequence is denoted as *seq*.

- (*empty* ##0 *seq*) does not result in a match

- (seq ##0 empty) does not result in a match

- (*empty* ##n seq), where n is greater than 0, is equivalent to (##(n-1) seq)

- (seq ##n empty), where n is greater than 0, is equivalent to (seq ##(n-1) 'true)

For example,

b ##1 ( a[\*0] ##0 c)

produces no match of the sequence.

b ##1 a[\*0:1] ##2 c

is equivalent to

(b ##2 c) **or** (b ##1 a ##2 c)

The syntax allows combination of a delay and repetition in the same sequence. The following are both allowed:

```

`true ##3 (a [*3]) // means `true ##1 `true ##1 `true ##1 a ##1 a ##1 a

(`true ##2 a) [*3] // means (`true ##2 a) ##1 (`true ##2 a) ##1

// (`true ##2 a), which in turn means `true ##1 `true ##1

// a ##1 `true ##1 `true ##1 a ##1 `true ##1 a

```

A sequence can be repeated as follows:

(a ##2 b) [\*5]

This is the same as:

(a ##2 b ##1 a ##2 b ##1 a ##2 b ##1 a ##2 b ##1 a ##2 b)

A repetition with a range of min minimum and max maximum number of iterations can be expressed with the consecutive repetition operator [\* min:max].

As an example,

(a ##2 b) [\*1:5]

is equivalent to

(a ##2 b)

or (a ##2 b ##1 a ##2 b)

or (a ##2 b ##1 a ##2 b ##1 a ##2 b)

or (a ##2 b ##1 a ##2 b ##1 a ##2 b)

or (a ##2 b ##1 a ##2 b ##1 a ##2 b ##1 a ##2 b)

or (a ##2 b ##1 a ##2 b ##1 a ##2 b ##1 a ##2 b ##1 a ##2 b)

Similarly,

(a[\*0:3] ##1 b ##1 c)

is equivalent to

(b ##1 c) or (a ##1 b ##1 c) or (a ##1 a ##1 b ##1 c) or (a ##1 a ##1 a ##1 b ##1 c)

To specify a finite, but unbounded, number of iterations, the dollar sign ( \$ ) is used. For example, the repetition:

a ##1 b [\*1:\$] ##1 c

matches over an interval of three or more consecutive clock ticks if a is true on the first clock tick, c is true on the last clock tick, and b is true at every clock tick strictly in between the first and the last.

Specifying the number of iterations of a repetition by exact count is equivalent to specifying a range in which the minimum number of repetitions is equal to the maximum number of repetitions. In other words, seq[\*n] is equivalent to seq[\*n:n].

The *goto repetition* (non-consecutive exact repetition) takes a boolean expression rather than a sequence as operand. It specifies the iterative matching of the boolean expression at clock ticks that are not necessarily consecutive and ends at the last iterative match. For example,

a ##1 b [->2:10] ##1 c

matches over an interval of consecutive clock ticks provided a is true on the first clock tick, c is true on the last clock tick, b is true on the penultimate clock tick, and, including the penultimate, there are at least 2 and at most 10 not-necessarily-consecutive clock ticks strictly in between the first and last on which b is true. This sequence is equivalent to:

a ##1 ((!b[\*0:\$] ##1 b) [\*2:10]) ##1 c

The *non-consecutive repetition* is like the goto repetition except that a match does not have to end at the last iterative match of the operand boolean expression. The use of non-consecutive repetition instead of goto repe-

tition allows the match to be extended by arbitrarily many clock ticks provided the boolean expression is false on all of the extra clock ticks. For example,

a ##1 b [=2:10] ##1 c

matches over an interval of consecutive clock ticks provided a is true on the first clock tick, c is true on the last clock tick, and there are at least 2 and at most 10 not-necessarily-consecutive clock ticks strictly in between the first and last on which b is true. This sequence is equivalent to:

a ##1 ((!b [\*0:\$] ##1 b) [\*2:10]) ##1 !b[\*0:\$] ##1 c

#### 17.7.3 Sampled value functions

This section describes the system functions available for accessing sampled values of an expression. These functions include the capability to access current sampled value, access sampled value in the past, or detect changes in sampled value of an expression. Sampling of an expression is explained in Section 17.3. The following functions are provided.

```

$sampled(expression [, clocking_event])

$rose( expression [, clocking_event])

$fell( expression [, clocking_event])

$stable( expression [, clocking_event])

$past( expression1 [, number of ticks] [, expression2] [, clocking event])

```

The use of these functions is not limited to assertion features; they can be used as expressions in procedural code as well. The clocking event, although optional as an explicit argument to the functions, is required for their semantics. The clocking event is used to sample the value of the argument expression.

The clocking event must be explicitly specified as an argument, or inferred from the code where it is used. The following rules are used to infer the clocking event:

- if used in an assertion, the appropriate clocking event from the assertion is used.

- if used in an action block of a singly-clocked assertion, the clock of the assertion is used.

- if used in a procedural block, the inferred clock, if any, for the procedural code (Section 17.13.5) is used.

Otherwise, default clocking (Section 15.11) is used.

When these functions are used in an assertion, the clocking event argument of the functions, if specified, shall be identical to the clocking event of the expression in the assertion. In the case of multi-clock assertion, the appropriate clocking event for the expression where the function is used, is applied to the function.

Function \$sampled returns the sampled value of the expression with respect to the last occurrence of the clocking event. When \$sampled is invoked prior to the occurrence of the first clocking event, the value of X is returned. The use of \$sampled in assertions, although allowed, is redundant, as the result of the function is identical to the sampled value of the expression itself used in the assertion.

Three functions are provided to detect changes in sampled values: \$rose, \$fell and \$stable.

A value change function detects the change in the sampled value of an expression. The clocking event is used to obtain the sampled value of the argument expression at a clock tick prior to the current simulation time unit. Here, the current simulation time unit refers to the simulation time unit in which the function is evaluated. This sampled value is compared against the value of the expression determined at the prepone time of the current simulation time unit. The result of a value change expression is true or false and can be used as a boolean expression.

srose returns true if the least significant bit of the expression changed to 1. Otherwise, it returns false.

\$fell returns true if the least significant bit of the expression changed to 0. Otherwise, it returns false.

sstable returns true if the value of the expression did not change. Otherwise, it returns false.

When these functions are called at or before the first clock tick of the clocking event, the results are computed by comparing the current sampled value of the expression to X.

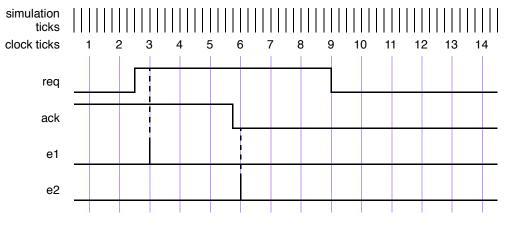

Figure 17-3 illustrates two examples of value changes:

- Value change expression e1 is defined as \$rose(req)

- Value change expression e2 is defined as \$fell(ack)

Figure 17-3 — Value change expressions

The clock ticks used for sampling the variables are derived from the clock for the property, which is different from the simulation ticks. Assume, for now, that this clock is defined elsewhere. At clock tick 3, e1 occurs because the value of req at clock tick 2 was low and at clock tick 3, the value is high. Similarly, e2 occurs at clock tick 6 because the value of ack was sampled as high at clock tick 5 and sampled as low at clock tick 6.

The example below illustrates the use of \$rose in SystemVerilog code outside assertions.

```

always @(posedge clk)

reg1 <= a & $rose(b);</pre>

```

In this example, the clocking event (**posedge** clk) is applied to \$rose. \$rose is true whenever the sampled value of b changed to 1 from its sampled value at the previous tick of the clocking event.

In addition to accessing value changes, the past values can be accessed with the *spast* function. The following three optional arguments are provided:

expression2 is used as a gating expression for the clocking event

number\_of\_ticks specifies the number of clock ticks in the past

clocking\_event specifies the clocking event for sampling expression1

expression1 and expression2 can be any expression allowed in assertions.

$number_of_ticks$  must be one or greater. If  $number_of_ticks$  is not specified, then it defaults to 1. \$past returns the sampled value of the expression that was present  $number_of_ticks$  prior to the time of evaluation of \$past. A clock tick is based on clocking\_event. If the specified clock tick in the past is before the start of simulation, the returned value from the \$past function is a value of X.

The optional argument *clocking\_event* specifies the clock for the function. The rules governing the usage of *clocking\_event* are same as those described for the value change function.

When intermediate optional arguments between two arguments are not needed, a comma must be placed for each omitted argument. For example,

\$past(in1, , enable);

Here, a comma is specified to omit *number\_of\_ticks*. The default of one is used for the empty *number\_of\_ticks* argument. Note that a comma for the omitted *clocking\_event* argument is not needed, as it does not fall within the specified arguments.

\$past can be used in any System Verilog expression. An example is shown below.

```

always @(posedge clk)

reg1 <= a & $past(b);</pre>

```

In this example, the clocking event (**posedge** clk) is applied to \$past. \$past is evaluated in the current occurrence of (**posedge** clk), and returns the value of b sampled at the previous occurrence of (**posedge** clk).

When *expression2* is specified, the sampling of *expression1* is performed based on its clock gated with *expression2*. For example,

```

always @(posedge clk)

if (enable) q <= d;

always @(posedge clk)

assert (done |=> (out == $past(q, 2, enable)) ;

```

In this example, the sampling of q for evaluating spast is based on the clocking expression

posedge clk iff enable

#### 17.7.4 AND operation

The binary operator **and** is used when both operands are expected to match, but the end times of the operand sequences can be different.

| sequence_expr ::=                     | // from Annex A.2.10 |

|---------------------------------------|----------------------|

| <br>  sequence_expr and sequence_expr |                      |

Syntax 17-6—and operator syntax (excerpt from Annex A)

The two operands of **and** are sequences. The requirement for the match of the **and** operation is that both the operands must match. The operand sequences start at the same time. When one of the operand sequences matches, it waits for the other to match. The end time of the composite sequence is the end time of the operand sequence that completes last.

When tel and te2 are sequences, then the composite sequence:

tel **and** te2

- Matches if te1 and te2 match.

- The end time is the end time of either tel or te2, whichever matches last.

The following example is a sequence with operator **and**, where the two operands are sequences.

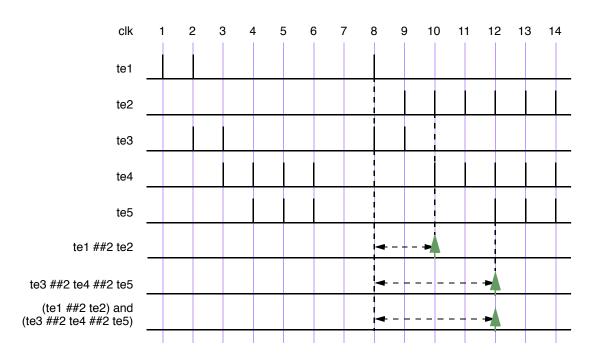

(te1 ##2 te2) **and** (te3 ##2 te4 ##2 te5)

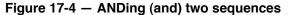

The operation as illustrated in Figure 17-4 shows the evaluation attempt at clock tick 8. Here, the two operand sequences are (te1 ##2 te2) and (te3 ##2 te4 ##2 te5). The first operand sequence requires that first te1 evaluates to true followed by te2 two clock ticks later. The second sequence requires that first te3 evaluates to true followed by te4 two clock ticks later, followed by te5 two clock ticks later.

This attempt results in a match since both operand sequences match. The end times of matches for the individual sequences are clock ticks 10 and 12. The end time for the composite sequence is the later of the two end times, so a match is recognized for the composite sequence at clock tick 12.

In the following example, the first operand sequence has a concatenation operator with range from 1 to 5:

(te1 ##[1:5] te2) **and** (te3 ##2 te4 ##2 te5)

The first operand sequence requires that tel evaluate to true and that te2 evaluate to true 1, 2, 3, 4, or 5 clock ticks later. The second operand sequence is the same as in the previous example. To consider all possibilities of a match of the composite sequence, the following steps can be taken:

- 1) Five threads of evaluation are started for the five possible linear sequences associated with the first sequence operand.

- 2) The second operand sequence has only one associated linear sequence, so only one thread of evaluation is started for it.

- 3) Figure 17-5 shows the evaluation attempt beginning at clock tick 8. All five linear sequences for the first operand sequence match, as shown in a time window, so there are five matches of the first operand sequence, ending at clock ticks 9, 10, 11, 12 and 13 respectively. The second operand sequence matches at clock tick 12.

4) Each match of the first operand sequence is combined with the single match of the second operand sequence, and the rules of the and operation determine the end time of the resulting match of the composite sequence.

The result of this computation is five matches of the composite sequence, four of them ending at clock tick 12, and the fifth ending at clock tick 13. Figure 17-5 shows the matches of the composite sequence ending at clock ticks 12 and 13.

Figure 17-5 — ANDing (and) two sequences, including a time range

If tel and te2 are sampled expressions (not sequences), the sequence (tel and te2) matches if tel and te2 both evaluate to true.

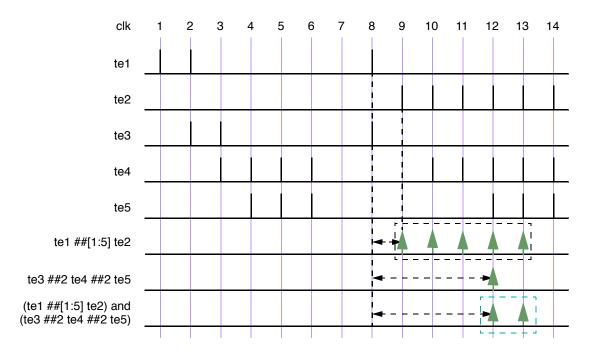

An example is illustrated in Figure 17-6, which shows the results for attempts at every clock tick. The sequence matches at clock tick 1, 3, 8, and 14 because both tel and te2 are simultaneously true. At all other clock ticks, match of the **and** operation fails because either tel or te2 is false.

Figure 17-6 — ANDing (and) two boolean expressions

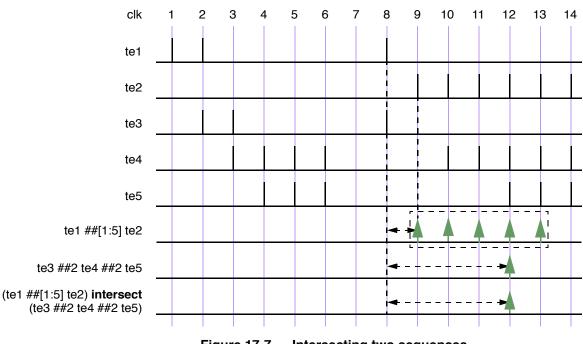

#### 17.7.5 Intersection (AND with length restriction)

The binary operator **intersect** is used when both operand sequences are expected to match, and the end times of the operand sequences must be the same.

sequence\_expr ::= // from Annex A.2.10

| sequence\_expr **intersect** sequence\_expr

#### Syntax 17-7—intersect operator syntax (excerpt from Annex A)

The two operands of **intersect** are sequences. The requirements for match of the **intersect** operation are:

- Both the operands must match.

- The lengths of the two matches of the operand sequences must be the same.

The additional requirement on the length of the sequences is the basic difference between **and** and **intersect**.

An attempted evaluation of an **intersect** sequence can result in multiple matches. The results of such an attempt can be computed as follows.

- Matches of the first and second operands that are of the same length are paired. Each such pair results in a

match of the composite sequence, with length and endpoint equal to the shared length and endpoint of the

paired matches of the operand sequences.

- If no such pair is found, then there is no match of the composite sequence.

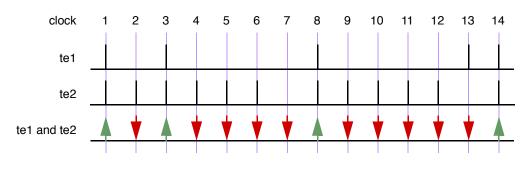

Figure 17-7 is similar to Figure 17-5, except that **and** is replaced by **intersect**. In this case, unlike in Figure 17-5, there is only a single match at clock tick 12.

Figure 17-7 — Intersecting two sequences

## 17.7.6 OR operation

The operator **or** is used when at least one of the two operand sequences is expected to match.

```

sequence_expr ::= // from Annex A.2.10

...

| sequence_expr or sequence_expr

```

Syntax 17-8—or operator syntax (excerpt from Annex A)

The two operands of or are sequences.

If the operands tel and te2 are expressions, then

tel **or** te2

matches at any clock tick on which at least one of te1 and te2 evaluates to true.

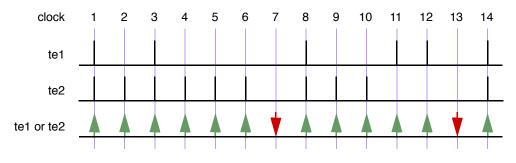

Figure 17-8 illustrates an **or** operation for which the operands te1 and te2 are expressions. The composite sequence does not match at clock ticks 7 and 13 because te1 and te2 are both false at those times. At all other clock ticks, the composite sequence matches, as at least one of the two operands evaluates to true.

Figure 17-8 — ORing (or) Two Sequences

When tel and te2 are sequences, then the sequence

tel **or** te2

matches if at least one of the two operand sequences tel and te2 matches. Each match of either tel or te2 constitutes a match of the composite sequence, and its end time as a match of the composite sequence is the same as its end time as a match of tel or of te2. In other words, the set of matches of tel or te2 is the union of the set of matches of tel with the set of matches of te2.

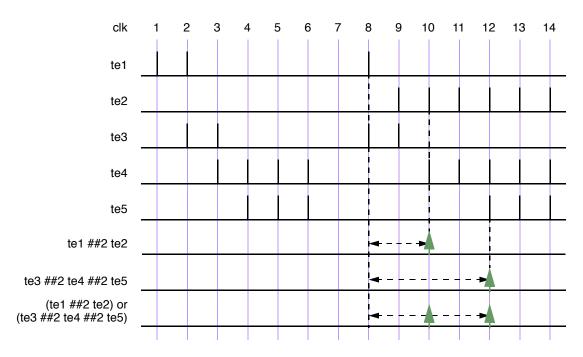

The following example shows a sequence with operator **or** where the two operands are sequences. Figure 17-9 illustrates this example.

(te1 ##2 te2) **or** (te3 ##2 te4 ##2 te5)

#### Figure 17-9 — ORing (or) two sequences

Here, the two operand sequences are: (te1 ##2 te2) and (te3 ##2 te4 ##2 te5). The first sequence requires that te1 first evaluates to true, followed by te2 two clock ticks later. The second sequence requires that te3 evaluates to true, followed by te4 two clock ticks later, followed by te5 two clock ticks later. In Figure 17-9, the evaluation attempt for clock tick 8 is shown. The first sequence matches at clock tick 10 and the second sequence matches at clock tick 12. So, two matches for the composite sequence are recognized.

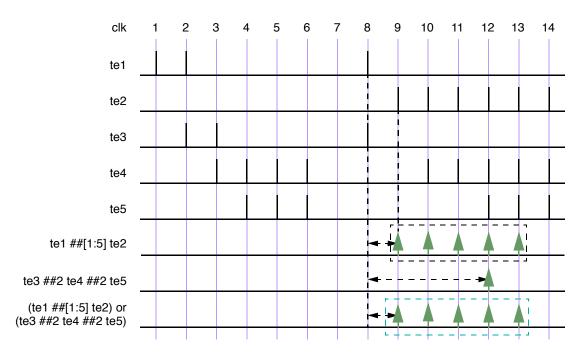

In the following example, the first operand sequence has a concatenation operator with range from 1 to 5

(te1 ##[1:5] te2) or (te3 ##2 te4 ##2 te5)

The first operand sequence requires that tel evaluate to true and that te2 evaluate to true 1, 2, 3, 4, or 5 clock ticks later. The second operand sequence requires that te3 evaluate to true, that te4 evaluate to true 2 clock ticks later, and that te5 evaluate to true another 2 clock ticks later. The composite sequence matches at any clock tick on which at least one of the operand sequences matches. As shown in Figure 17-10, for the attempt at clock tick 8, the first operand sequence matches at clock ticks 9, 10, 11, 12, and 13, while the second operand matches at clock tick 12. The composite sequence therefore has one match at each of clock ticks 9, 10, 11, and 13 and has two matches at clock tick 12.

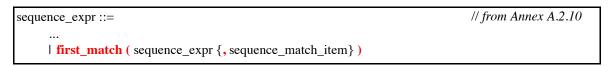

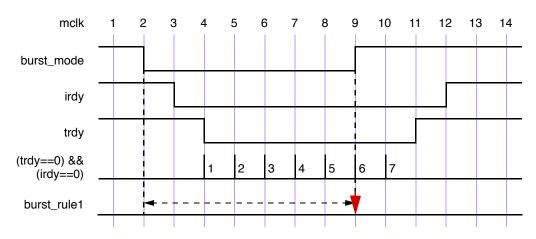

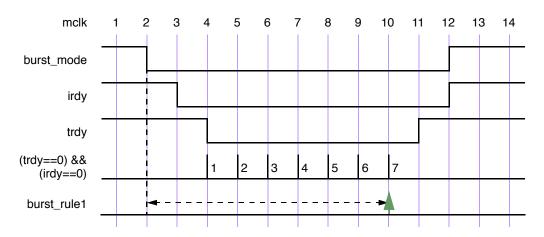

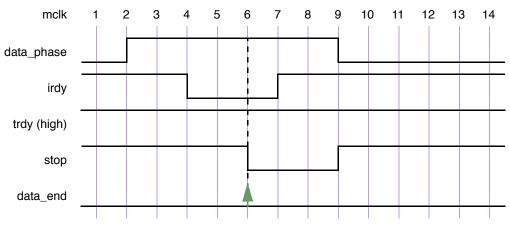

#### 17.7.7 first\_match operation

The first\_match operator matches only the first of possibly multiple matches for an evaluation attempt of its operand sequence. This allows all subsequent matches to be discarded from consideration. In particular, when a sequence is a subsequence of a larger sequence, then applying the first\_match operator has significant effect on the evaluation of the enclosing sequence.

Syntax 17-9—first\_match operator syntax (excerpt from Annex A)

An evaluation attempt of first\_match (seq) results in an evaluation attempt for the operand seq beginning at the same clock tick. If the evaluation attempt for seq produces no match, then the evaluation attempt for first\_match (seq) produces no match. Otherwise, the match of seq with earliest ending clock tick is a match of first\_match (seq). If there are multiple matches of seq with the same ending clock tick as the earliest one, then all those matches are matches of first\_match (seq).

The example below shows a variable delay specification.

```

sequence t1;

tel ## [2:5] te2;

endsequence

sequence ts1;

first_match(tel ## [2:5] te2);

endsequence

```

Here, tel and te2 are expressions. Each attempt of sequence tl can result in matches for up to four of the following sequences: te1 ##2 te2 te1 ##3 te2 te1 ##4 te2 te1 ##5 te2