ENGINEERING

UNIVERSITY OF MICHIGAN

Introduction

- Reliability is a big concern in Multi-core Processors as the technology nodes are scaling

- Inter-Core resource sharing increases reliability in presence of fault (e.g. StageNet Architecture)

- This leads to high communication delay

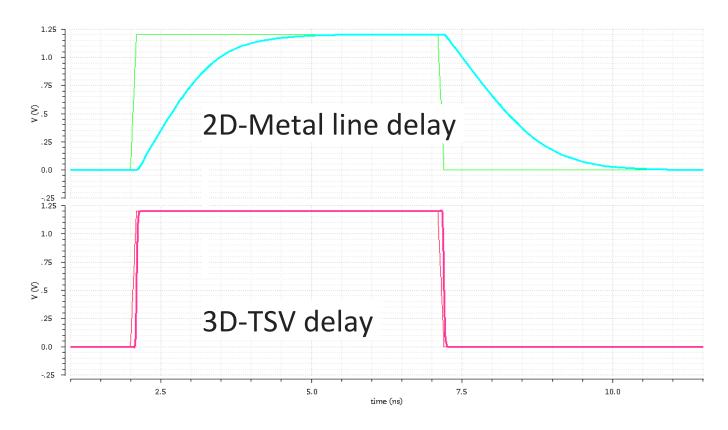

- 3D integration is a promising solution to increase density and performance

# Objective

- Use StageNet based structure with two functionalities in case of failure

- Arranging healthy resources in different cores to create one healthy pipeline (Virtual Pipeline)

- Sharing healthy resources in other cores when they are not being used

- Use 3D integration to reduce communication delay and hence improve performance over 2D design

- Model Through-Silicon Vias (TSV) to simulate the 3D design and performance

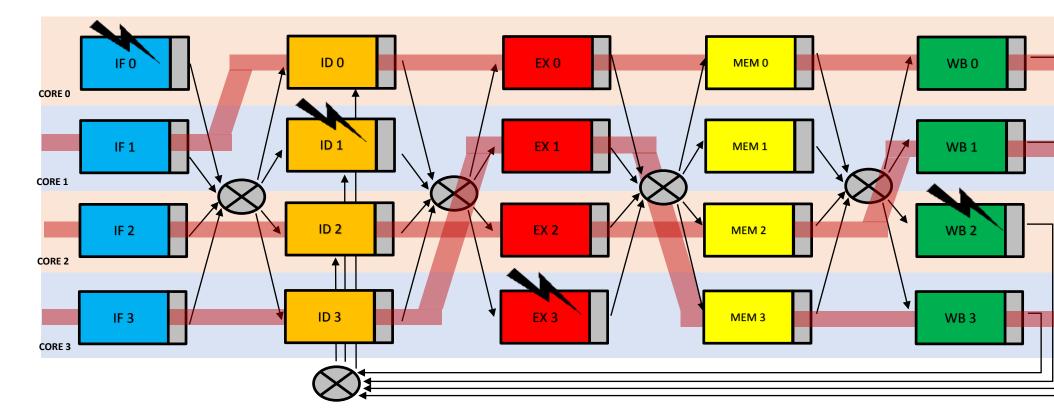

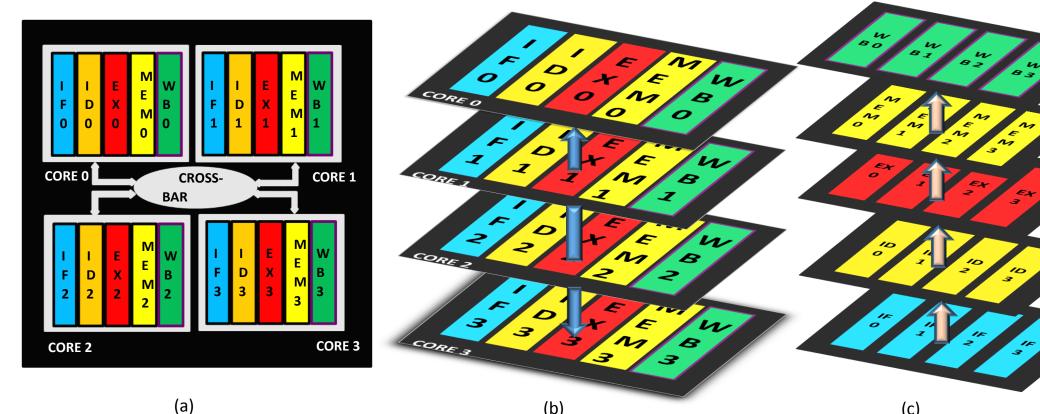

# Architecture

- MaPnet: Using inter-core redundancy to salvage the processor in case of faults.

- 2D design

- Core-based 3D design

- Pipeline-based 3D design

Figure 1. A 5-satge pipeline structure for 4 cores and switches between stages

Figure 2. Three different designs for MAPnet (a) 2D structure with crossbars (b) Core-based 3D structure (c) Pipelinebased 3D structure

# MaPnet: A Three-Dimensional Fabric for Reliable Multi-core Processors

Javad Bagherzadeh, Sugandha Gupta, Byounchan Oh University of Michigan, Ann Arbor

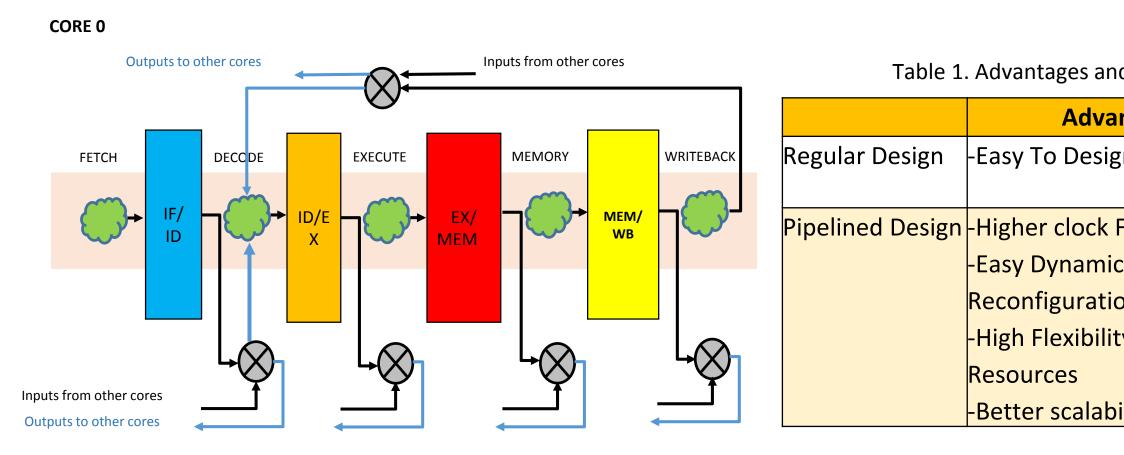

Figure 3. Single core architecture with connection to crossbar and pipeline registers

# Implementation

- MAPnet design is implemented on a 4-core architecture with simple cores

- TSV delay and behavior is simulated by SPICE simulations and used to determine routing delay and processor frequency

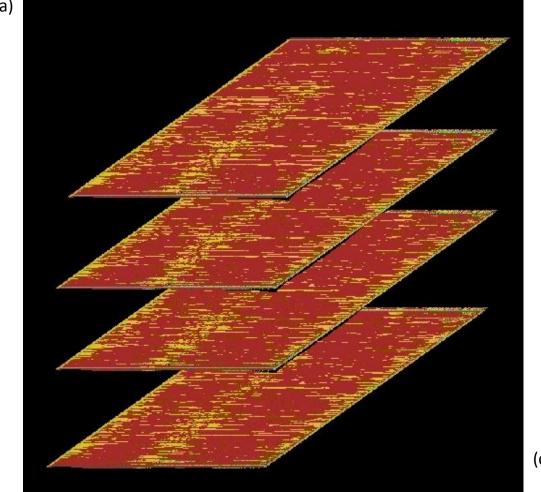

- Both 3D designs show performance improvement over the 2D design

- The throughput increases by 1.74X

- On comparing the post-APR frequencies in faulty and healthy cores and considering Table 1, we decided to pipeline both architectures to reduce clock frequency

- Crossbars in 2D and 3D structures need 1 and 2 pipeline stages respectively.

- The RTL was synthesized using Synopsys Design Compiler and Cadence Encounter was used to create the layout

| Table 2. Clock Period results after Place and Route (using Encounter) |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

| MAPnet Design              | 2D                  | Core-based 3D       | Pipeline 3D         |

|----------------------------|---------------------|---------------------|---------------------|

| Clock<br>(No Fault)        | 2.5 ns<br>(400 MHz) | 2.5 ns<br>(400 MHz) | 2.5 ns<br>(400 MHz) |

| Clock<br>(Fault Condition) | 7 ns<br>(143 MHz)   | 3.95 ns<br>(250MHz) | 3.85<br>(260MHz)    |

| Footprint Area             | 1200*1200 sq.us     | 600*600 sq. us      |                     |

| Layout Density             | 71%                 | 67%                 |                     |

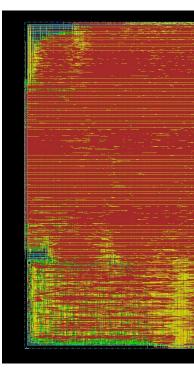

Conceptual 3D 4-core Design

### 3D architectures have performance advantage in many core designs (Figure 6)

Results

Table 1. Advantages and disadvantages of each design

| Advantages            | Disadvantages             |  |  |

|-----------------------|---------------------------|--|--|

| o Design              | -Slow                     |  |  |

|                       | -Low Scalability          |  |  |

| r clock Frequency     | -Difficult to Design      |  |  |

| Dynamic               | -Need extra control units |  |  |

| figuration            | -Area Overhead            |  |  |

| lexibility in Sharing |                           |  |  |

| rces                  |                           |  |  |

| r scalability         |                           |  |  |

Figure 5. Layouts for (a) 2D 4-core processor, (b) Basic 1-core and (c)

Figure 6. Estimated Clock Period for different number of cores for MAPnet – (a) 2D structure with crossbars (b) Core-based 3D structure (c) Pipeline-based 3D structure

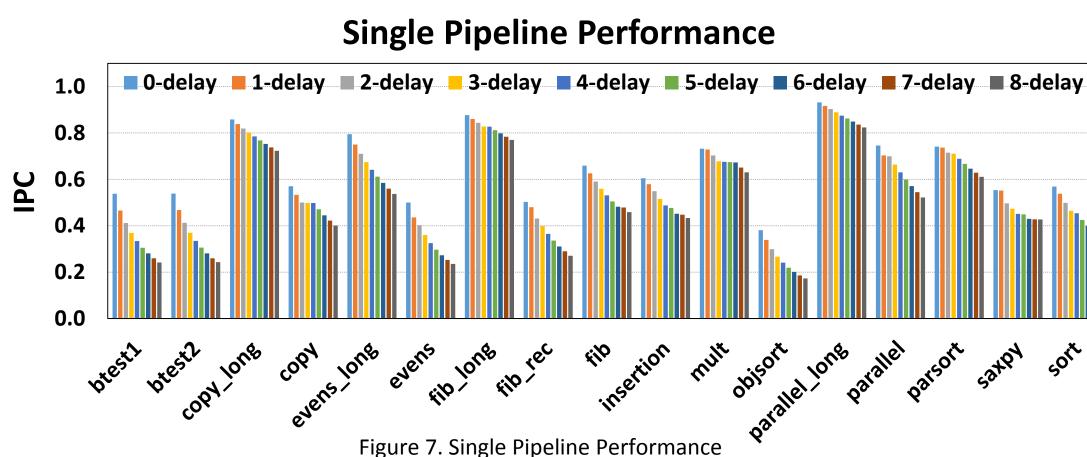

- into pipeline structure to use resources in other cores

- extra delay cycles added in pipeline structure which is reflected in Figure 7.

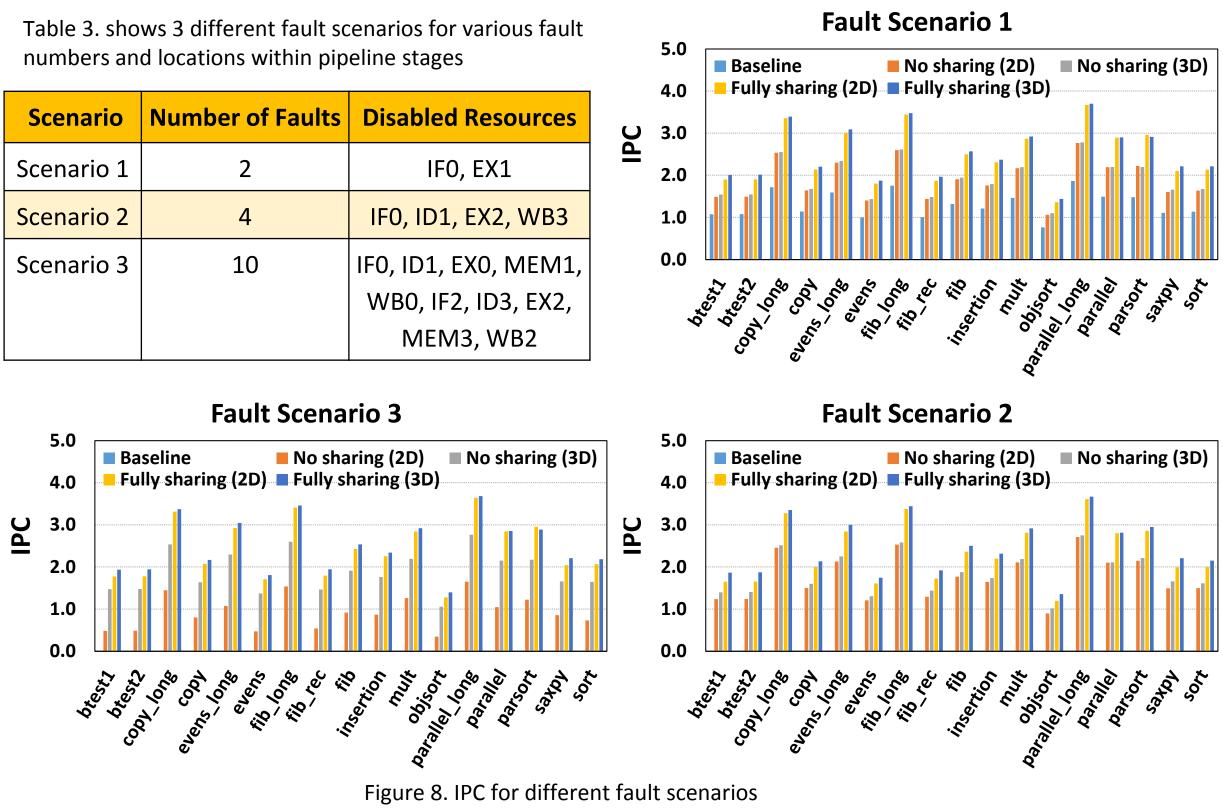

- IPC was measured for each scenario

- Figures 8 reflect the results for baseline 2D and 3D pipelined structures regarding sharing the same resource and no sharing.

numbers and locations within pipeline stages

| Scenario   | Number of Faults | <b>Disabled Resources</b>                                |

|------------|------------------|----------------------------------------------------------|

| Scenario 1 | 2                | IFO, EX1                                                 |

| Scenario 2 | 4                | IFO, ID1, EX2, WB3                                       |

| Scenario 3 | 10               | IF0, ID1, EX0, MEM1,<br>WB0, IF2, ID3, EX2,<br>MEM3, WB2 |

- Improvement with 2D and 3D StageNet compared 2 baseline

- 16.3% on average and up to 28.2% improvement in 3D compared to 2D

- area of our 3D design is under than 25% of the traditional 2D design due to reduced interconnection complexity.

# Conclusion

- 3D reconfigurable pipeline design, named MaPNet.

- more-reliable operation, higher performance, lower cost, and/or lower power consumption by taking advantage of the redundancy and capabilities available at each layer in the system stack.

# Fall 2015

Each fault forces the processor to reconfigure and adds extra delays cycles

We simulated a single core for different test cases and measured the IPC for