John P. Hayes

University of Michigan EECS 579 Fall 2001

Lecture13: Page 1

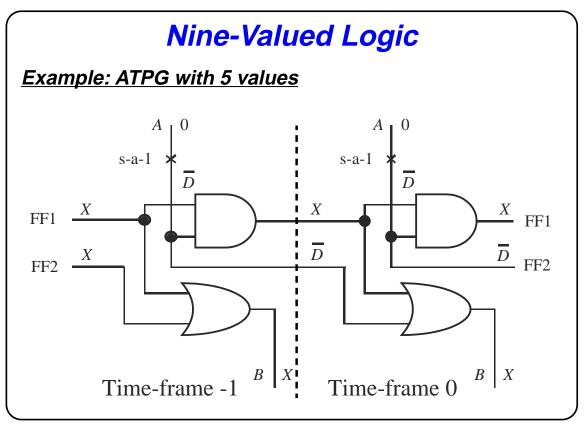

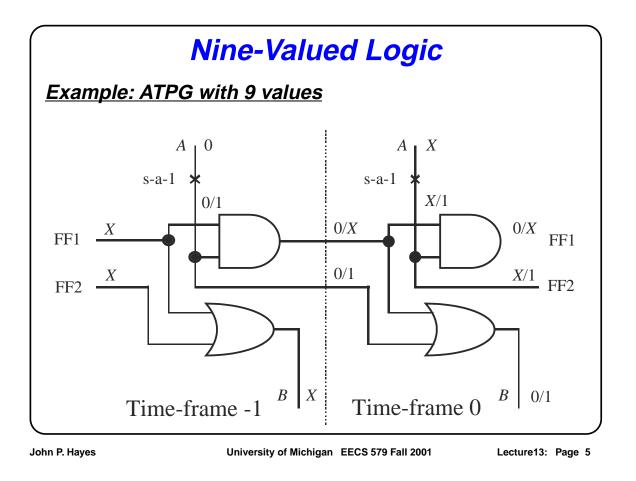

|               | -                | Ŭ         |      | l may to | conside | all pair | s of 0,1,1 | X   |

|---------------|------------------|-----------|------|----------|---------|----------|------------|-----|

| U             |                  | e good/fa | •    | chines   |         |          |            |     |

|               |                  | ed algeb  |      |          |         |          |            |     |

| D             | D'               | 0         | 1    | X        |         |          |            |     |

| 1/0           | 0/1              | 0/0       | 1/1  | X/X      |         |          |            |     |

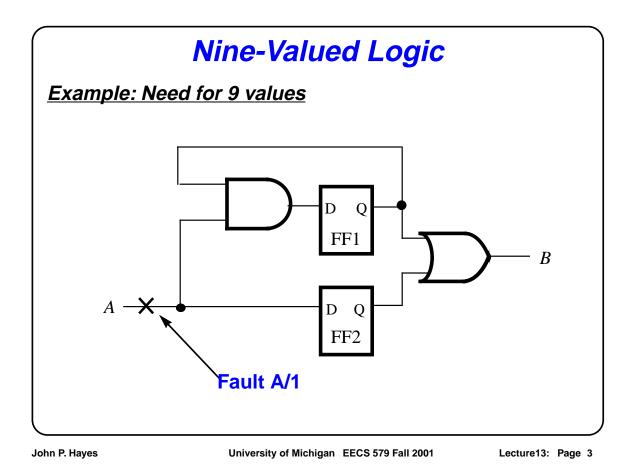

| • <u>Muth</u> | <u>'s 9-valu</u> | ied algeb | ora: |          |         |          |            |     |

| D             | D'               | 0         | 1    | X        |         |          |            |     |

| 1/0           | 0/1              | 0/0       | 1/1  | X/X      | 0/X     | 1/X      | X/0        | X/1 |

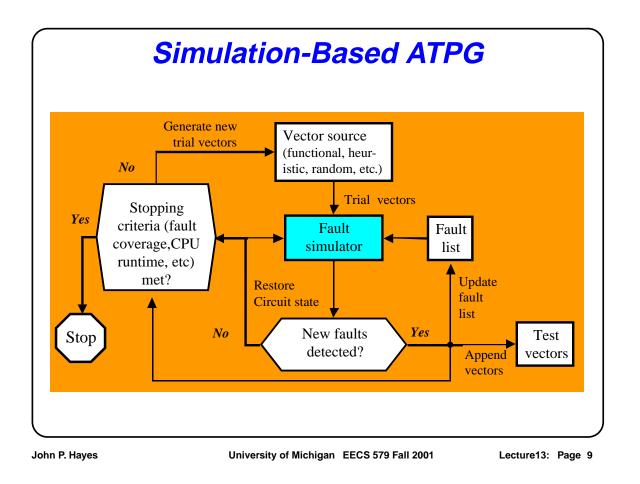

Simulation-Based ATPG

### **Possible Methods**

- Directed search

- Genetic algorithms

- Spectral techniques

### Advantages

- Fault simulation technology is very well-developed

- Many types of test methods (deterministic, functional, random) can be used

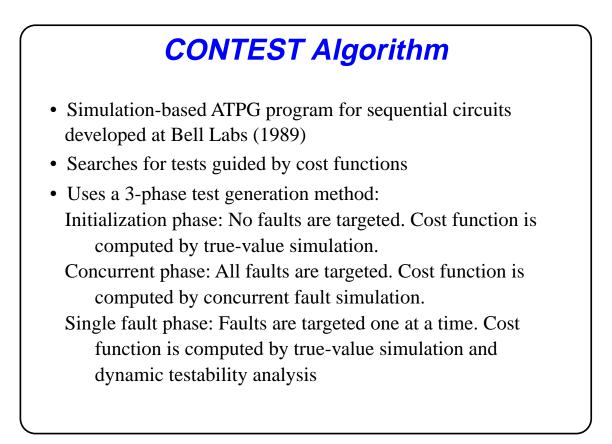

## CONTEST Algorithm Cost Functions Functions are defined for specific current objectives (initialization or fault detection) Each function numerically grades a test vector for suitability to meet the current objective Cost function = 0 for any vector that exactly meets the objective Cost is computed for an input vector via either true-value or fault simulation

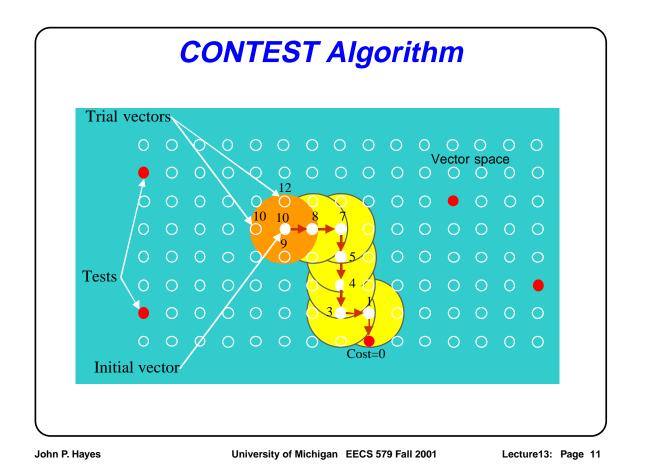

# CONTEST Algorithm Phase I: Initialization Initialize test sequence with random or given vector (sequence) Set all flip-flops in unknown (X) state Cost functions used: Number of flip-flops in the X state Cost computed from true-value simulation of trial vectors Trial vector generation: Heuristically generate trial vector set from the previous vector(s) in the test sequence, e.g., all vectors at Hamming distance one from the last vector Vector selection: Add the minimum-cost trial vector to the test sequence. Repeat trial vector generation and vector selection until cost ≤ given limit.

John P. Hayes

University of Michigan EECS 579 Fall 2001

Lecture13: Page 13

### **CONTEST** Algorithm

### **Phase II: Concurrent Fault Detection**

- Initial test sequence uses vectors from Phase I

- Simulate all faults and drop detected faults

- Compute a distance cost function for trial vectors: For each undetected fault, find the shortest fault distance (no. of gates) between its fault effect and a primary output Cost function = sum of fault distances for all undetected faults

- Trial vectors: Generate trial vectors, e.g., using unit distance

- Vector selection:

Add trial vector with the minimum cost function to test sequence Remove faults with zero fault distance from the fault list.

• Repeat trial vector generation and vector selection until fault list reduces to given size

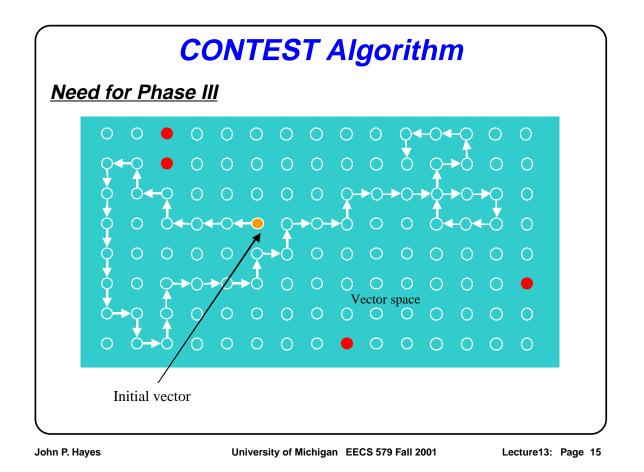

## CONTEST Algorithm Dhase III: Single Fault Target Cost (fault, input vector) = K × AC + PC Activation cost (AC) is the dynamic controllability of the faulty line Propagation cost (PC) is the minimum (over all paths to POs) dynamic observability of the faulty line. K is a large weighting factor, e.g., K = 100. Dynamic testability measures (controllability and observability) are specific to the present signal values in the circuit. Cost of a vector is computed for a fault from the true-value simulation result. Cost = 0 means fault is detected. Trial vector generation and vector selection are similar to the other phases

|                      | CONTEST | Random Tests | Gentest** |

|----------------------|---------|--------------|-----------|

| Fault coverage       | 75.5%   | 67.6%        | 72.6%     |

| Untestable faults    | 0       | 0            | 122       |

| Test vectors         | 1,722   | 57,532       | 490       |

| Trial vectors used   | 57,532  |              |           |

| Test gen. CPU time#  | 3 min.* | 0            | 4.5 hrs.  |

| Fault sim. CPU time# | 9 min.* | 9 min.       | 10 sec.   |

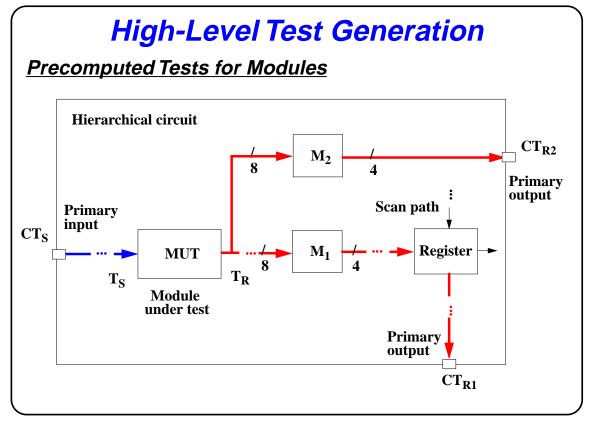

### **High-Level Test Generation**

### <u>Goals</u>

- Speed up test generation

- Generate tests for circuits without complete structural models

### <u>Methods</u>

- Use structural hierarchy and circuit and fault modeling

- Use functional descriptions of modules and circuits

- Distinguish data and control functions

- Exploit high-level (expert) information about circuit operation

John P. Hayes

University of Michigan EECS 579 Fall 2001

Lecture13: Page 19