# EECS 373 Midterm 1

20 February 2024

No calculators, reference material, internet, or communicating with others about the exam (except course staff).

Name

UM Uniqname

Sign below to acknowledge the Engineering Honor Code: "I have neither given nor received aid on this examination, nor have I concealed a violation of the Honor Code." "Concealed" should be interpreted as "have failed or will fail to report".

Signature

# 1 [13 pts.] Short questions

- 1. [3 pts.] If the embedded market is larger than the general-purpose computing market, why is it common for embedded systems designers to work on smaller teams? Select the single most correct answer.

- Embedded systems are generally less expensive than general-purpose computers so the total market capitalization for embedded systems is lower, leading to less money to hire embedded systems engineers.

- The market is fragmented, with more varieties of applications and products. This increases the number of teams required, reducing the number of embedded systems designers per team.

- Embedded system designers are more productive than general-purpose computer system designers, so fewer are needed to accomplish the same amount of work.

- Debugging complexity is linearly related to processor clock frequency, making low-frequency embedded microcontroller based systems much easier to debug than high-frequency general-purpose systems.

- There are a very wide range of general-purpose processors available, but only a few embedded processors. This enables fewer embedded system designers to manage processor-based design complexity.

- Unlike general-purpose computer system designers, embedded systems designers use FPGAs in the prototyping process, making it easy for fewer designers to complete the same work.

- 2. [3 pts.] Indicate all system design decisions that will likely increase total design and debugging time.

- Adding assertions for facts that appear to be obviously correct to one's code.

- Deferring all error checking to run-time.

- Adding infinite loop traps to unused ISRs that should never be invoked.

- $\bigcirc$  Writing special values to memory locations to enable checking whether they were inappropriately overwritten.

- $\bigcirc$  Ensuring that all tests are done on the entire system in a realistic environment approximating its expected future use.

- 3. [3 pts.] Consider a virtual timer system in which the bookkeeping information on individual timers is stored in a container sorted in order of increasing timer firing times. You must decide whether to implement the container using an array or linked list. Indicate all the application characteristics that indicate that an array would be better, or for which a linked list would provide no advantages over an array.

- $\bigcirc$  Virtual timers will most frequently be periodic/recurring.

- $\bigcirc$  New timers will always have firing times greater than all previously created timers.

- $\bigcirc$  The application requires floating point math.

- The number of virtual timers required is unknown and unbounded at compile time.

- The timers must execute callbacks provided via function pointers.

- 4. [2 pts.] If we were to model the debugging time of a complex system as  $2^{e+v}$  minutes where v is the number of vertices and e is the number of edges in a component interaction graph, then what is the expected debugging time (in minutes) for a system with four components, each of which may interact with any other component? Treat this as an undirected graph, i.e., an interaction between A and B is captured by the same edge as an interaction between B and A.

5. [2 pts.] Continuing from the prior question, if we were to limit the number of interactions to two per component, what would the expected debugging time (in minutes) be?

# 2 [10 pts.] MMIO

1. [5 pts.] Indicate all of the following that are true.

- $\bigcirc\,$  Accessing MMIO requires special load and store instructions.

- $\bigcirc\,$  Accessing MMIO can be slower than accessing physical memory.

- $\bigcirc\,$  All MMIO transactions happen entirely on the AHB.

- $\bigcirc\,$  Using MMIO is always faster than using a dedicated I/O bus.

- MMIO is only used to communicate with peripherals external to the microcontroller.

- 2. [5 pts.] Consider the following code segment.

```

volatile uint32_t *addr = 0x1234ABCD;

uint32_t x = *addr;

x = *addr;

```

Use at most one sentence to indicate what may go wrong if the volatile keyword on the first line were not used.

# 3 [20 pts.] APB

You are designing a smart brooder for chicks. You are given an APB memory-mapped I/O hardware device that has three distance sensors and three LEDs. Each distance sensor is configured to output a high signal when one or more chicks is near it and a low signal when no chick is near it. The goal is to allow remote monitoring of chick locations to enable adjustment to brooder temperature profiles. The LEDs are active low. Each distance sensor has an associated read-only 32-bit memory address, with the sensor's output transmitted in bit 31. The LEDs have a shared write-only 32-bit memory address. LEDs A, B, and C are controlled by bits in positions 0, 1, and 2, respectively. Below is the implementation of the Verilog module that can be controlled by writing to the memory-mapped I/O registers.

```

module chicks_in_a_house (

input PCLK, PRESERN, PSEL, PENABLE, PWRITE

output PREADY, PSLVERR,

input [7:0] PADDR,

input [31:0] PWDATA,

output [31:0] PRDATA,

input dist_sen_a, dist_sen_b, dist_sen_c,

output led_a, led_b, led_c);

assign PSLVERR = 0;

assign PREADY = PENABLE;

wire enable, read_a_en, read_b_en, read_c_en;

assign enable = PSEL & PENABLE & PWRITE & (PADDR == 0);

assign read_a_en = PSEL & PENABLE & ~PWRITE & (PADDR == 4);

assign read_b_en = PSEL & PENABLE & ~PWRITE & (PADDR == 8);

assign read_c_en = PSEL & PENABLE & ~PWRITE & (PADDR == 12);

assign PRDATA[31] =

(read_a_en) ? dist_sen_a :

(read_b_en) ? dist_sen_b :

(read_c_en) ? dist_sen_c :

1'bz;

always @(posedge PCLK) begin

if (enable) begin

led_a <= PWDATA[0];</pre>

led_b <= PWDATA[1];</pre>

led_c <= PWDATA[2];</pre>

end

end

endmodule

```

1. [12 pts.] In the following sub-problems, you will write a C program that reads in the state of the distance sensors and turns on the corresponding LED. Distance sensor A is associated with LED A, B with B, and C with C. Assume that PSEL is configured to be high when memory locations 0x80080000– 0x8008000F are accessed. You may assume that the distance sensor measurement will not change while the functions are running.

(a) [4 pts.] Write the body of a function that reads one of the distance sensors, where the sensor selection index ranges from 0-2.

uint32\_t read\_distance\_sensor (uint32\_t index) {

(b) [4 pts.] Write the body of a function that writes to the LED indicated by the index.void write\_led (uint32\_t index, uint32\_t val) {

(c) [4 pts.] Write a function that uses the read\_distance\_sensor and write\_led functions to set the LEDs appropriately based on the distance sensor states.

void update\_leds {

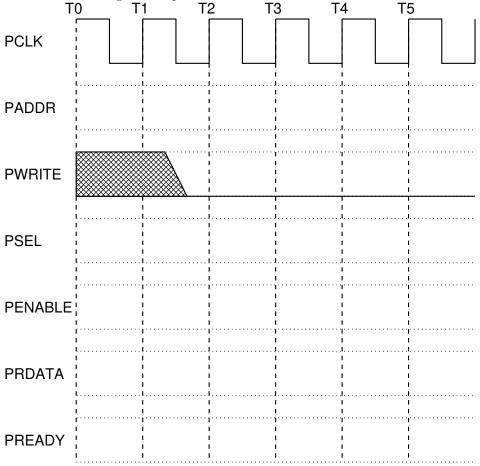

2. [8 pts.] Fill in the unspecified signals in the timing diagram bylow for a read from distance sensor B. The PWRITE and CLK signals are provided.

## 4 [20 pts.] Embedded ANSI C

Your friend is writing ANSI C for an ARM Cortex M4 microcontroller. Assume access to a linker script that gives the following memory layout.

| High men           | nory address     |  |  |

|--------------------|------------------|--|--|

| Heap               | $1\mathrm{KB}$   |  |  |

| Data               | $50\mathrm{KB}$  |  |  |

| Stack              | $1\mathrm{KB}$   |  |  |

| Text               | $100\mathrm{KB}$ |  |  |

| Low memory address |                  |  |  |

Assume the stack grows toward lower memory addresses. Your friend has written the following main.c file.

```

#include <stdint.h>

1

2

#define SIGNIFICANT_VALUE OxDEADBEEF

3

4

5

/* Adds el to buffer at index, then increments index, wrapping

6

* around if needed.

7

* Implementation not shown, assume it is correctly implemented */

extern void pushCircularBuffer(char* buffer, int size, uint32_t* index, char el);

8

9

10 #define BUFFER_SIZE 10000

11 uint32_t currentIndex = 0;

12

13 int main(void) {

14 uint32_t *peripheralRegister = (uint32_t *) 0x40000000;

15 char circularBuffer[BUFFER_SIZE];

16

17

while (1) {

if (*peripheralRegister == SIGNIFICANT_VALUE) {

18

19

incrementCounter();

20

pushCircularBuffer(circularBuffer, BUFFER_SIZE, &currentIndex, 'Y');

21

} else {

22

pushCircularBuffer(circularBuffer, BUFFER_SIZE, &currentIndex, 'N');

23

}

24

}

15 }

16

17 void incrementCounter(void) {

static int counter = 0;

18

19

++counter;

20 }

```

1. [8 pts.] For the following symbols, indicate what region of memory their underlying value is stored in. If a symbol doesn't correspond to something stored in memory, write "n.a.". If a value is a pointer, indicate where the pointer is stored, not the address it points to.

| Symbol             | Region |

|--------------------|--------|

| peripheralRegister |        |

| currentIndex       |        |

| circularBuffer     |        |

| incrementCounter   |        |

| SIGNIFICANT_VALUE  |        |

2. [4 pts.] Your friend attempts to cross-compile and link their program with the ARM GNU toolchain, and uses the -O3 and -Werror flags. The program fails to compile. Give the number of one line of the program that can be changed to correct the compilation problem, and write the new contents of the line. It is fine to replace any numbered line, even one that is currently empty.

| Line number:   |       |  |  |

|----------------|-------|--|--|

| New line conte | ents: |  |  |

|                |       |  |  |

|                |       |  |  |

|                |       |  |  |

3. [4 pts.] After your change, the binary is successfully built and flashed to the microcontroller. However, a HARD\_FAULT signal is generated soon after the program starts execution. Describe the most likely cause of the hard fault, and indicate the change you would make to correct it. Reference line numbers when possible.

4. [4 pts.] After your change, the program no longer faults. However, after single-stepping with a debugger, you observe unexpected behavior: the counter doesn't increment despite the peripheral register holding SIGNIFICANT\_VALUE. Modify one line to fix the unexpected behavior. Indicate the line you changed, write the revised version, and explain why your solution is correct below.

Line number:

New line contents and explanation:

## 5 [25 pts.] Assembly and ABI

### 1. [10 pts.] Assembly.

The function rand is an ABI compliant function with the following prototype: int rand(void). The function swap\_randomly has the following prototype: void swap\_randomly(int \*a, int \*b). The following ARM assembly code attempts to implement the swap\_randomly function. The empty boxes are places where you might later add code; ignore them for now.

#### 1 swap\_randomly:

2 ldr r6, [r0] // load int from a 3 4 ldr r7, [r1] // load int from b 5 6 bl rand 7 8 and r0, r0, #1 9 cmp r0, #0 10 11 beq end 12 str r7, [r0] 13 str r6, [r1] 14 15 end: 16 17 bx lr

Unfortunately, swap\_randomly it is not ABI-compliant. Make the additions in the boxes above needed for it to be ABI compliant, correct, and efficient. There exists a correct solution in which only four lines of code are added in total to some of the numbered but empty lines in the version shown above.

2. [15 pts.] ABI.

Write an ARM assembly language procedure that implements the C function naive\_shuffle in an ABI-compliant manner. Clearly comment code and label which registers each value represents. Code comments enable partial credit. Assume that we are using the ABI-compliant implementation of the function swap\_randomly.

```

void naive_shuffle(int *array, int input_size) {

int i = 1;

while (i < input_size) {

int *a = array + i;

int *b = a - 1;

swap_randomly(a, b);

++i;

}

}</pre>

```

Although you are not required to use the following assembly instructions, some might be helpful: ADD, B, BEQ, BGE, BL, BX, CMP, LDR, LSL, MUL, MOV, POP, PUSH, SUB, and STRB.

# 6 [12 pts.] Interrupts

- 1. [3 pts.] Which of the following maps interrupt numbers to ISR addresses?

- $\bigcirc$  NVIC

- ⊖ MMIO

- $\bigcirc$  APB bus

- $\bigcirc$  AHB bus

- $\bigcirc\,$  EXTI controller

- 2. [5 pts.] A single interrupt occurs during the execution of a process. Label the following 1–5 in the order in which they happen. 1 is what happens first and 5 is what happens last. One blank will have two numbers in it.

| • | Interrupt pending bit goes high. |

|---|----------------------------------|

| • | External event in the world.     |

| • | Executing in ISR mode.           |

| • | Executing in thread mode.        |

3. [4 pts.] Use at most three sentences to describe a scenario in which tail chaining happens. Be specific and include relative times of when events happen. How does tail chaining improve performance of a system?

This page may be used for work. Please hand it in with the exam and reference it from the associated questions if you would like it to be considered when determining partial credit.