### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# InP- AND GaN-BASED DEVICES AND MMICS FOR SIGNAL CONTROL AND GENERATION

# by

# **Egor Alekseev**

A dissertation submitted in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

(Electrical Engineering)

in The University of Michigan

2000

# **Doctoral Committee:**

Professor Dimitris Pavlidis, Chairman Assistant Professor Rachel Goldman Professor Gabriel M. Rebeiz Professor Jasprit Singh UMI Number: 9963734

#### UMI Microform 9963734

Copyright 2000 by Bell & Howell Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346 © Egor Alekseev

All Rights Reserved

2000

To my parents, my fiancée Denise, and my friends,

all of whom have helped and supported me

during the time of my graduate studies and,

hopefully,

will continue to do so in the future.

#### **ACKNOWLEDGMENTS**

I would like to thank my committee chairman, Professor Dimitris Pavlidis, for his professional and personal guidance, help, and advice received during the course of my graduate research. It has been a great experience to work in his research group and be involved in so many of its challenging projects. I would also like to thank my other committee members Professor Rachel Goldman, Professor Gabriel Rebeiz, and Professor Jasprit Singh for their helpful suggestions and comments.

I would like also to express my sincere appreciation to Dr. Jürgen Dickmann from Daimler Benz Research Center at Ulm and Dr. John Zolper of the Office of Naval Research for their financial and professional support.

This work would not have been possible without the contributions of Dr. Kyushik Hong and Delong Cui (InP), and especially Dr. Andreas Eisenbach (GaN), who spent long hours in the MOCVD room providing epilayers for fabrication and characterization of the first UofM GaN-based devices presented in this work. The contribution of Thomas Hackbarth at Daimler Benz for additional MBE-grown PIN wafers is also greatly appreciated. I would also like to thank Dr. Xiangkun Zhang and Prof. Pallab Bhattacharya for additional PIN/HEMT wafers.

I would like to thank my past fellow students Dr. Phil Marsh, Kevin Hein, Dr. Apostolos Samelis, and Dr. Donald Sawdai among others, for their training, help, and useful discussions in the fabrication technology and characterization methods. The contributions of former group members who developed the basis for the PIN and FET technology developed in this work (Dr. Phil Marsh, Dr. Don Sawdai, Dr. Youngwoo Kwon, and Dr. Kyushik Hong) are greatly appreciated. I would also like to thank our current group members Seth Hubbard, Shawn Hsu, and William Sutton, and Abishai Daniels for taking over the burden of GaN research, which helped me to concentrate on writing of this thesis. I would also like to thank our colleagues Volker Ziegler and Michel

Berg from Daimler Benz for fabrication of coplanar InP-based PIN diode switches and some of the concepts used in their design.

I would especially like to thank Dr. Heribert Eisele for valuable discussions and help with W-band power characterization. Suggestions and help from Professor Tamotsu Hashizume of Hokkaido University in the matter of AlN/GaN interface properties is also greatly appreciated. Characterization of GaN-based HFETs for switching applications was made possible by collaboration with our colleagues Nguyen X. Nguyen, Chanh Nguyen, and David E. Grider at HRL Laboratories.

I would like to deeply thank the staff of Solid-State Electronics Laboratory for support, assistance, and keeping the lab running. I would especially like to thank Dr. Dennis Grimard, Tim Brock, Keith Bowerman, and the volunteers on the GaAs-Bay Committee, who worked hard to improve the equipment and students in the lab.

My coming to the University of Michigan was made possible by an exchange program with St-Petersburg State Polytechnic University and its representatives Ms. Irina Podnozova, Professor Charles Kauffman, and Assistant Dean Anne W. Monterio. I would also like to acknowledge the role of Dr. Edward Lozansky of American University in Moscow and Professor Edwin Dolan of American Institute of Business and Economics, who gave me a start on the road to education in the United States. Last, but not least, I would like to thank Mr. Robert Emett and Mrs. Mary Ann Emett of Balboa, CA, and Mr. Greg Knapp and Mrs. Jolene Knapp of Ann Arbor, MI for their generous friendship that made my stay in Michigan much happier.

Finally, I would like to thank my fiancée Denise Bryngelson (my chief editor) and my parents for their unlimited patience, love, and understanding during my studies. I would also like to thank my friends (in and out of the clean room), such as Don Sawdai, Peter Goetz, Seth Hubbard, Will Sutton, Shawn Hsu, Cheng-Hui Lin, Andreas Eisenbach, Sergei Filippov, Val Kolpakov, Nick Taylor, Mark Klein, and Tom Yeh for their support and encouragement. Go blue!

I would like to sincerely thank ARO/URI (Contract No. DAAL 03-92-G-0109), MURI (Contract No. DAAH04-96-1-0001) Daimler Benz AG, and ONR (Contract Nos. N00014-92-J-1552 and N00014-99-1-0513) for their funding of this research.

# TABLE OF CONTENTS

| DEDICATION                                                         | ii   |

|--------------------------------------------------------------------|------|

| ACKNOWLEDGMENTS                                                    | iii  |

| LIST OF FIGURES                                                    | vii  |

| LIST OF TABLES                                                     | xv   |

| CHAPTER   INTRODUCTION                                             | 1    |

| 1.1. Status of Compound Semiconductor RF Technology                |      |

| 1.2. Role of Signal Control and Generation Circuits in W-band      |      |

| Automotive Radars                                                  |      |

| 1.3. Semiconductor Devices for Control Applications                | 5    |

| 1.4. Review of Microwave PIN Diode Switches                        | 8    |

| 1.5. GaN-Based NDR Diodes for Microwave Signal Generators          | 11   |

| 1.6. Objective and Scope of the Thesis                             | 12   |

| CHAPTER 2 FUNDAMENTAL CHARACTERISTICS OF SWITCHING PIN             |      |

| DIODES                                                             | 15   |

| 2.1. Design and Operation of InGaAs PIN Diodes                     | 16   |

| 2.2. DC Characteristics of InGaAs PIN Diodes                       | 19   |

| 2.3. High-Frequency Characteristics of InGaAs PIN Diodes           | 29   |

| 2.4. Numerical Simulations of InGaAs PIN Diodes                    | 36   |

| 2.5. Conclusions                                                   | 43   |

| CHAPTER 3 InGaAs PIN DIODES FOR MILLIMETER-WAVE MONOLITHIC         |      |

| INTEGRATED CONTROL CIRCUITS                                        | 44   |

| 3.1. Optimization of InGaAs PIN Diodes for Millimeter-Wave         |      |

| Applications                                                       | 45   |

| 3.2. InGaAs PIN Diode Technology                                   |      |

| 3.3. Low-Frequency Characterization of Switching InGaAs PIN Diode  | s 62 |

| 3.4. High-Frequency Characterization of Switching InGaAs PIN Diode | s71  |

| 3.5. Conclusions                                                   | 80   |

| CHAPTER 4 InP-BASED PIN DIODE SIGNAL-CONTROL MMICs FOR W-          |      |

| BAND APPLICATIONS                                                  | 82   |

| 4.1. Semiconductor Microwave and Millimeter-Wave Switches          |      |

| 4.2. Design of W-band InGaAs PIN Diode SPST Switches               | 85   |

| 4.3. Microstrip InGaAs PIN Diode Switches                          |      |

| 4.4. Coplanar InGaAs PIN Diode Switches                            |      |

| 4.5. W-band InGaAs PIN Diode Phase Shifters                        |      |

| 4.6. Conclusions                                                   | 122  |

| CHAPTER 5 CHARACTERIZATION OF POWER-HANDLING AND                    |     |

|---------------------------------------------------------------------|-----|

| SWITCHING-RATE CAPABILITIES OF InGaAs PIN DIODES                    | 123 |

| 5.1. Development of W-Band Automatic On-Waver Load-Pull System      | 123 |

| 5.2. W-band Load-Pull Characterization of InGaAs PIN Diode and      |     |

| MMICs                                                               | 130 |

| 5.3. Power-Handling Capabilities of Switching InGaAs PIN Diodes and |     |

| MMICs                                                               | 133 |

| 5.4. Evaluation of InGaAs PIN Diode Switching Rates                 | 140 |

| 5.5. Conclusions                                                    |     |

| CHAPTER 6 GaN-BASED HETEROJUNCTION FETs FOR SWITCHING               |     |

| APPLICATIONS                                                        | 149 |

| 6.1. Design and Operation of Switching FETs                         |     |

| 6.2. Power Capabilities of GaN-Based FETs                           |     |

| 6.3. Power Performance and Scalability of AlGaN/GaN HFETs           |     |

| 6.4. Development of AlN/GaN MISFETs                                 |     |

| 6.5. Summary                                                        |     |

| CHAPTER 7 GaN-BASED NEGATIVE DIFFERENTIAL RESISTANCE                |     |

| DIODES FOR HIGH-POWER MILLIMETER SIGNAL                             |     |

| GENERATION                                                          | 189 |

| 7.1. Mechanism of Negative Differential Resistance in GaN           |     |

| 7.2. Fundamental Frequency Limitations of NDR Devices               |     |

| 7.3. GaN NDR Diodes Simulation Methodology                          |     |

| 7.4. Design of GaN NDR Diodes                                       | 204 |

| 7.5. Small-Signal Analysis of GaN NDR Diode Oscillators             |     |

| 7.6. Large-Signal Analysis of GaN-based NDR Diodes                  |     |

| 7.7. Evaluation of Frequency and Power Capabilities of GaN NDR      |     |

| Sources                                                             | 219 |

| 7.8. Conclusions                                                    | 221 |

| CHAPTER 8 CONCUSIONS AND SUGGESTIONS FOR FUTURE STUDIES             | 223 |

| 8.1. Summary and Conclusions                                        |     |

| 8.2. Suggestions for Future Work                                    |     |

| BIBLIOGRAPHY                                                        | 231 |

|                                                                     |     |

# LIST OF FIGURES

| Figure |                                                                                                                                                                        |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 1.1. Block diagram of a W-band automotive front-end module4                                                                                                            |

|        | 1.2. Performance-frequency diagram demonstrating development of monolithic PIN diode switches9                                                                         |

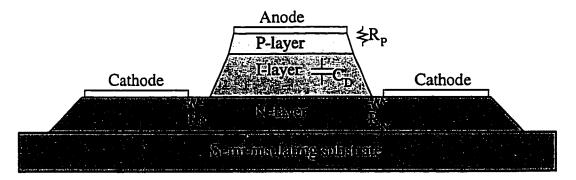

|        | 2.1. Cross-section of an epitaxially-grown switching microwave PIN diode 15                                                                                            |

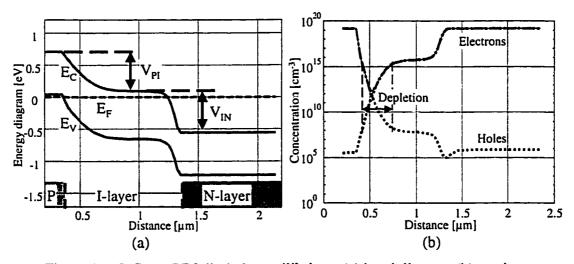

|        | 2.2. InGaAs PIN diode in equilibrium: (a) band diagram (b) carrier-concentration profiles                                                                              |

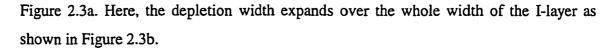

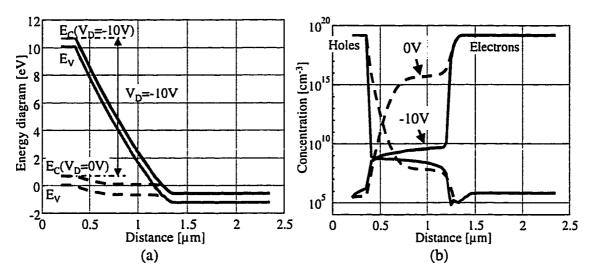

|        | 2.3. InGaAs PIN diode band-diagram and carrier profiles in the OFF-state 18                                                                                            |

|        | 2.4. InGaAs PIN diode band-diagram and carrier profiles in the ON-state19                                                                                              |

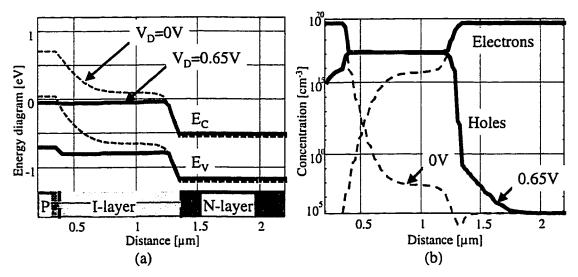

|        | 2.5. Experimental and theoretical leakage current of InGaAs PIN diodes20                                                                                               |

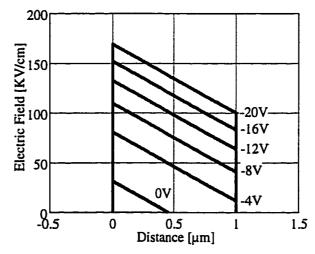

|        | 2.6. Distribution of electric field in the InGaAs PIN diode for reverse bias of 0, -4, -8, -12, -16, and -20V (V <sub>PT</sub> =-2.7V)22                               |

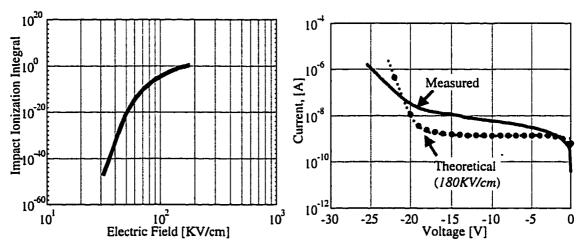

|        | 2.7. Impact ionization integral and I-V characteristics for avalanche breakdown of the InGaAs PIN diode24                                                              |

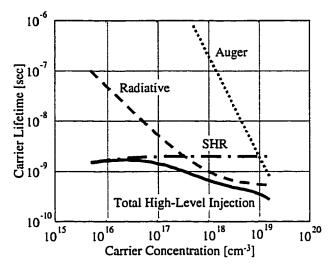

|        | 2.8. Dependence of carrier lifetimes on carrier concentration in I-InGaAs27                                                                                            |

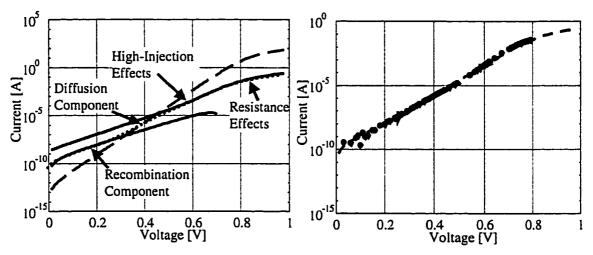

|        | 2.9. I-V characteristics of InGaAs PIN diodes: a) different components of the ON-state current, b) comparing of theoretical and measured results28                     |

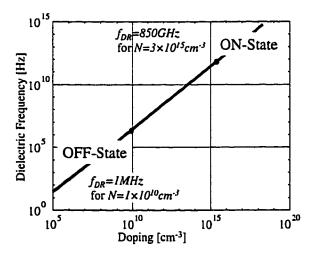

|        | 2.10. Dielectric relaxation frequency in InGaAs and frequency dependence of conductance mechanism in I-InGaAs (N <sub>I</sub> =5×10 <sup>15</sup> cm <sup>-3</sup> )29 |

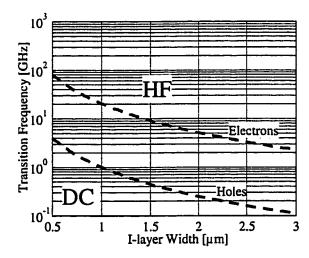

|        | 2.11. Electron and hole transit-time frequencies of InGaAs PIN diodes31                                                                                                |

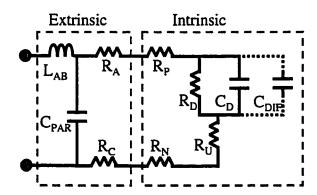

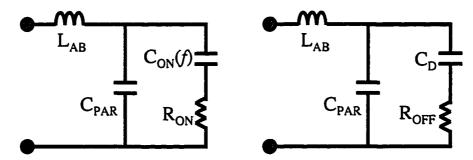

|        | 2.12. Complete small-signal equivalent circuit of the PIN diode32                                                                                                      |

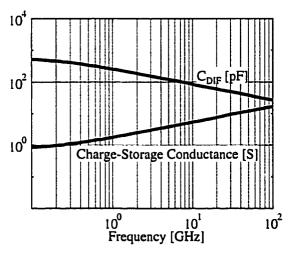

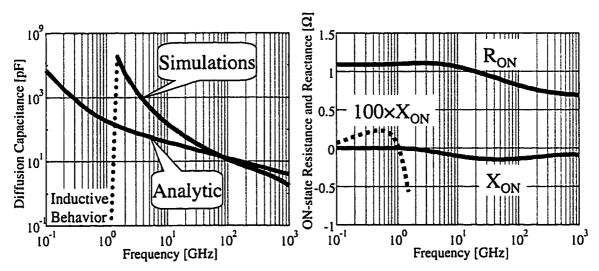

|        | 2.13. Frequency dependence of the diffusion capacitance and charge-storage conductance evaluated for the ON-state InGaAs PIN diode33                                   |

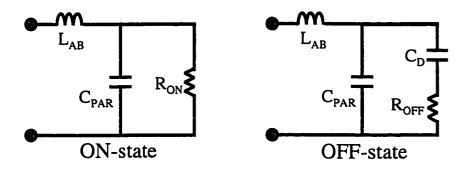

|        | 2.14. ON-state and OFF-state equivalent circuits of the InGaAs PIN diode34                                                                                             |

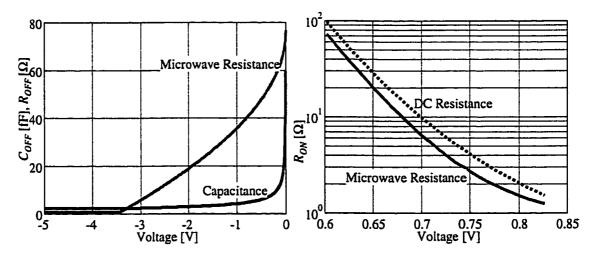

|        | 2.15. High-frequency characteristics of the InGaAs PIN diode as a function of control bias: a) OFF-state and b) ON-state                                               |

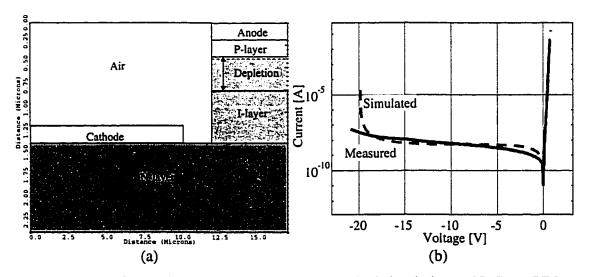

|        | 2.16. Two-dimensional cross-section of InGaAs PIN diode37                                                                                                              |

|        | 2.17. Results of two-dimensional numerical simulations of InGaAs PIN                                                                                                   |

diodes: a) boundaries of depletion region at equilibrium, b) I-V

characteristics......38

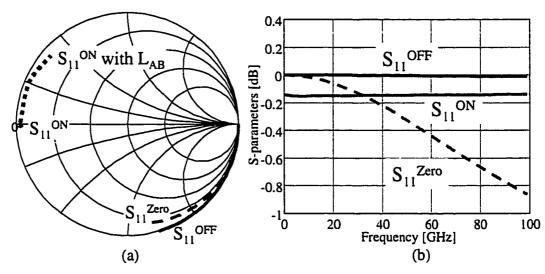

| 2.18. Simulated $S_{II}$ -parameter of the InGaAs PIN diode                                                                                                                                  | 39 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.19. Frequency dependence of diffusion capacitance and the ON-state impedance of an InGaAs PIN diode                                                                                        | 40 |

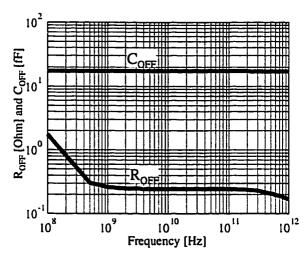

| 2.20. Frequency dependence of the OFF-state InGaAs PIN equivalent-circuit elements                                                                                                           | 41 |

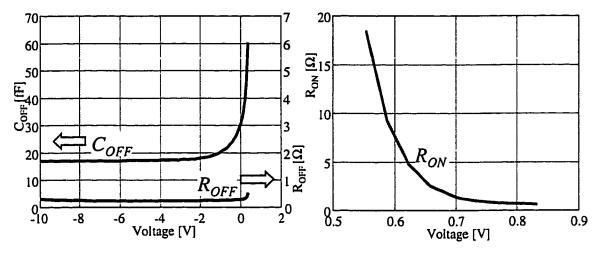

| 2.21. Bias d ependence of InGaAs PIN diode equivalent-circuit elements                                                                                                                       | 42 |

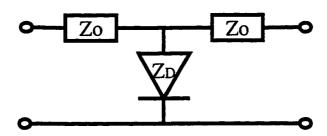

| 3.1. Schematic of a shunt PIN diode SPST switch                                                                                                                                              | 46 |

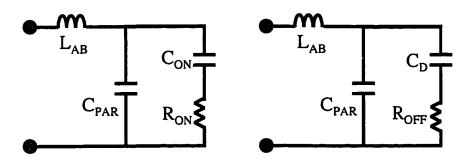

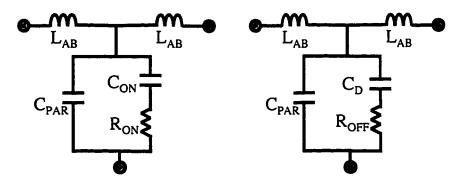

| 3.2. Millimeter-wave equivalent-circuit of switching InGaAs PIN diode in the ON- and in the OFF-state                                                                                        | 46 |

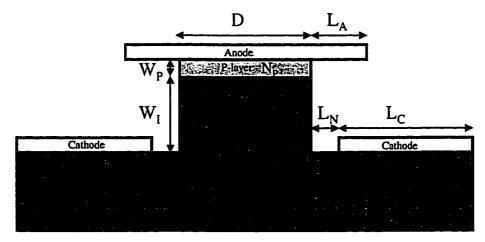

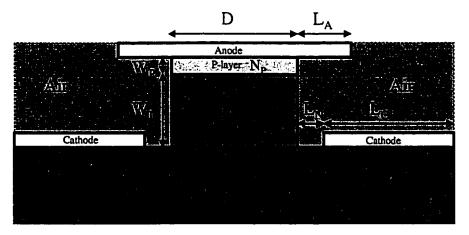

| 3.3. Cross-section of InGaAs PIN used for device optimization                                                                                                                                | 48 |

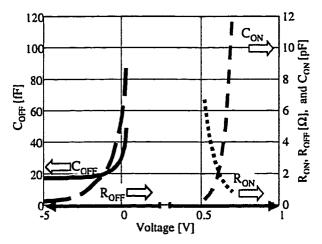

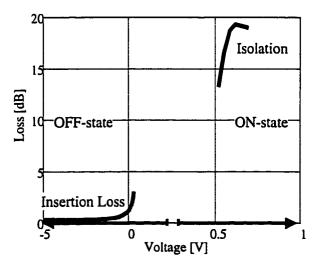

| 3.4. Simulated bias dependence of $R_{ON}$ , $C_{ON}$ , $R_{OFF}$ , and $C_{OFF}$                                                                                                            | 49 |

| 3.5. Bias dependence of insertion loss and isolation of the InGaAs SPST switch at 94GHz                                                                                                      | 49 |

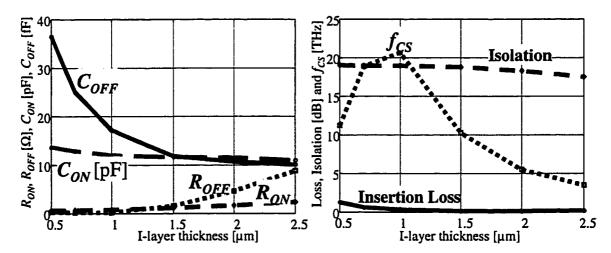

| 3.6. Influence of the I-layer thickness on the high-frequency characteristics of InGaAs PIN diode and the performance of a shunt PIN SPST at 94GHz                                           |    |

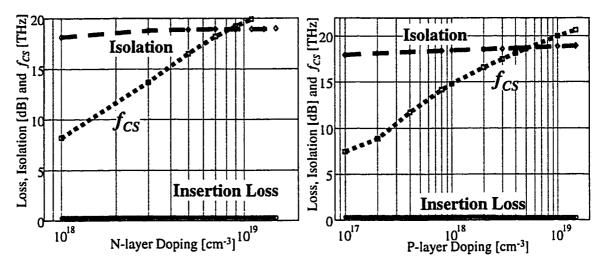

| 3.7. Influence of the P- and N-layer doping on the performance of a shunt InGaAs PIN diode SPST switch at 94GHz                                                                              | 52 |

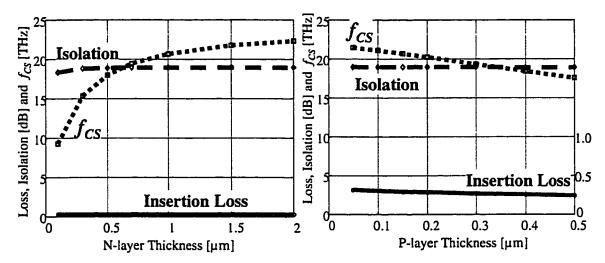

| 3.8. Influence of the P and N layer thickness' on the performance of a shunt InGaAs PIN diode SPST switch at 94GHz                                                                           | 53 |

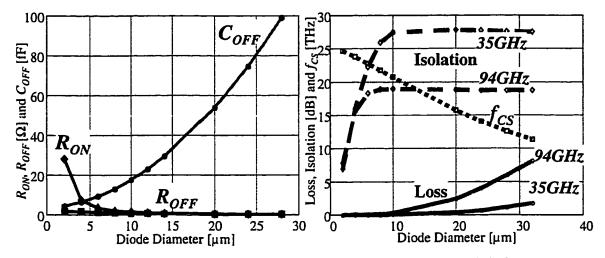

| 3.9. Influence of the InGaAs PIN diode diameter on the high-frequency characteristics of the InGaAs PIN diode and the performance of a shunt InGaAs PIN diode SPST switch at 94GHz and 35GHz |    |

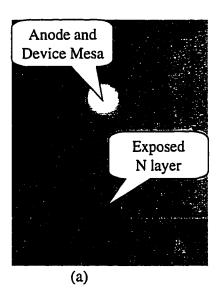

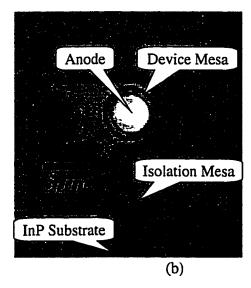

| 3.10. Optical microscope photographs of InGaAs PIN diodes during fabrication: (a) after device mesa etch and (b) after isolation mesa etch                                                   | 60 |

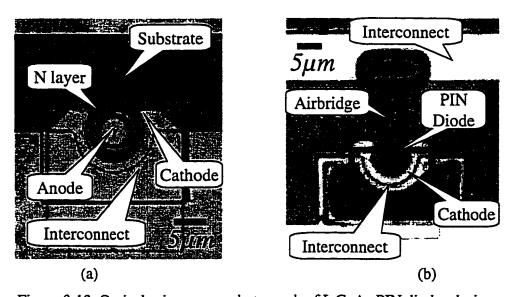

| 3.11. SEM photograph of a partially fabricated InGaAs PIN diode                                                                                                                              | 60 |

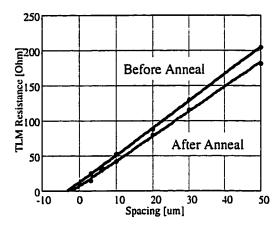

| 3.12. Typical TLM Characteristics of InGaAs n-type ohmic contacts                                                                                                                            | 61 |

| 3.13. Optical microscope photograph of InGaAs PIN diodes during fabrication (a) after interconnect deposition and (b) after airbridge plating                                                | 61 |

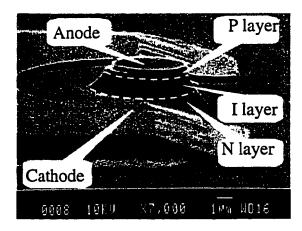

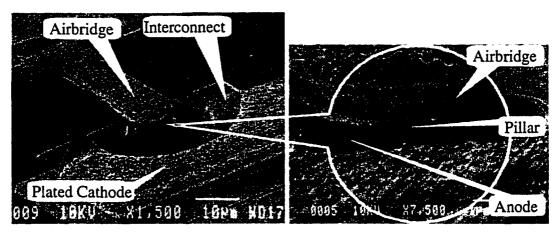

| 3.14. SEM photograph of a fabricated InGaAs PIN diode                                                                                                                                        | 62 |

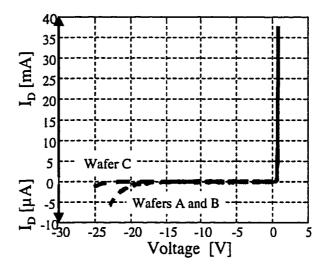

| 3.15. I-V characteristics of InGaAs PIN diodes                                                                                                                                               | 64 |

| 3.16. I-V characteristics of InGaAs PIN demonstrating thermal nature of the experimentally observed negative differential resistance                                                         | 65 |

| 3.17. Dependence of Ideality Factor on the doping of the I layer                                                                                                                             | 66 |

| 3.18. Reverse I-V characteristics for InGaAs and GaAs PIN diodes                                                                                                                             | 67 |

| 3.19. Breakdown of InGaAs PINs as a function of temperature                                                                                                                                  | 68 |

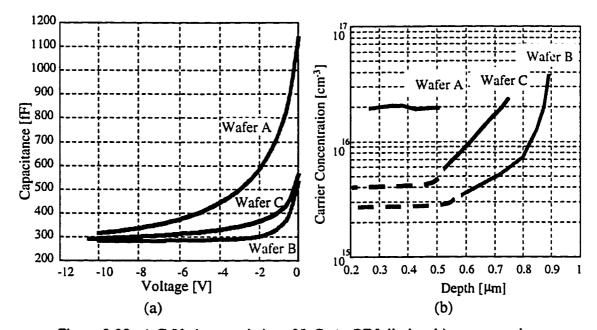

| 3.20.   | a) C-V characteristics of InGaAs PIN diodes; b) concentration profiles extracted from the C-V characteristics.                                                         | .69 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

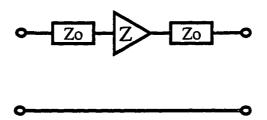

| 3.21.   | Schematic of a series PIN diode SPST switch                                                                                                                            | .71 |

| 3.22.   | Photograph of a InGaAs PIN diode series SPST switch                                                                                                                    | .72 |

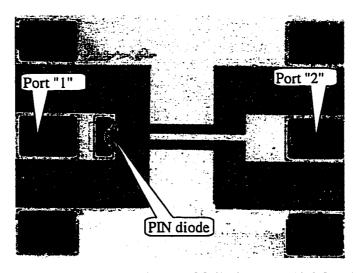

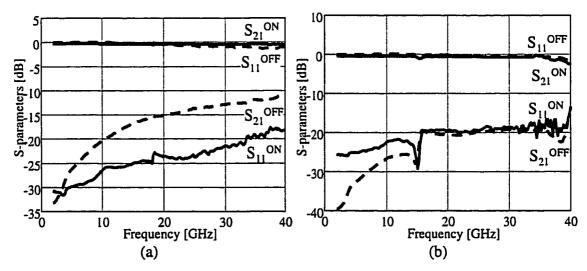

|         | S-parameters of InGaAs PIN diode series SPST switches with (a) 10µm-diameter and (b) 5µm-diameter diodes                                                               |     |

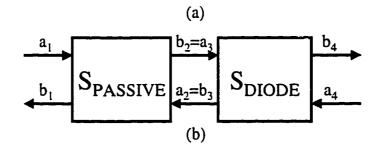

| 3.24.   | PIN diode S-parameter extraction: (a) S-parameters of SPST switch (b) S-parameters of the cascaded networks of the passive structure and the discrete InGaAs PIN diode | .74 |

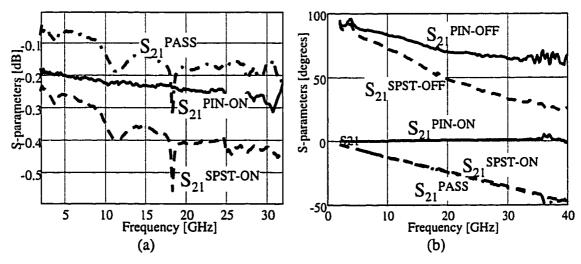

| 3.25.   | S-parameters of the InGaAs PIN SPST switch (dashed line), passive structure (dash-dot line), and discrete InGaAs PIN (solid line)                                      | .75 |

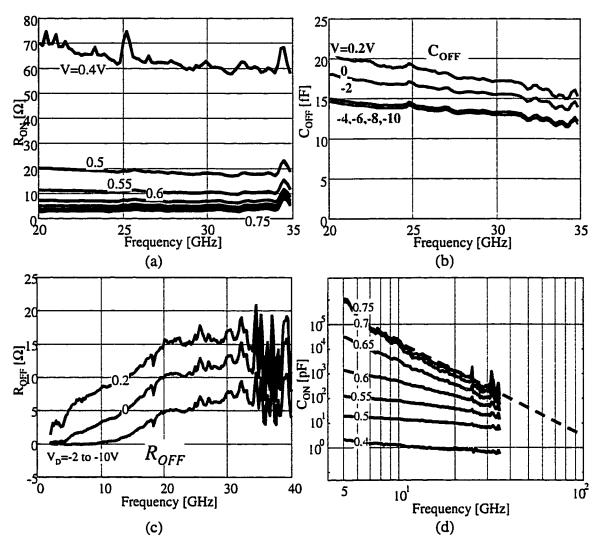

| 3.26.   | Frequency-dependent equivalent-circuit elements of a $10\mu m$ -diameter InGaAs PIN diode: a) $R_{ON}$ , b) $C_{OFF}$ , c) $R_{OFF}$ , and d) $C_{ON}$                 | .77 |

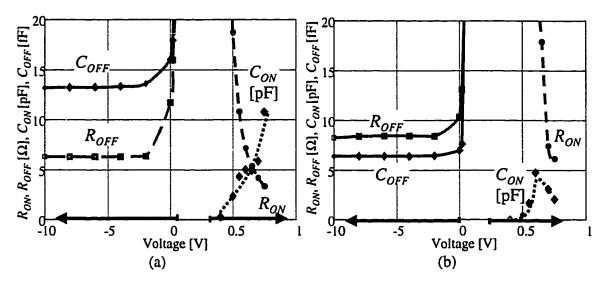

| 3.27.   | Bias dependence of equivalent-circuit elements of a) $10\mu m$ -diameter and b) $5\mu m$ -diameter InGaAs PIN diodes                                                   | .78 |

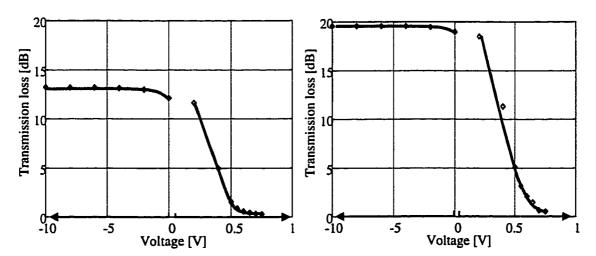

| 3.28.   | Measured bias-dependence of switching characteristics of InGaAs PINs for a) $10\mu m$ -diameter and b) $5\mu m$ -diameter diodes                                       | .79 |

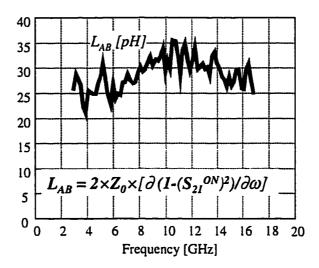

| 3.29.   | Evaluation of airbridge inductance from measured S-parameters                                                                                                          | .80 |

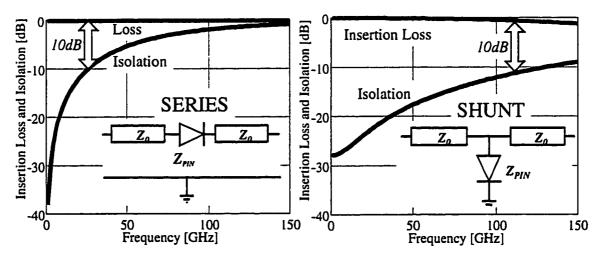

| 4.1. l  | Performance of the series and shunt PIN diode switches                                                                                                                 | .83 |

| 4.2. 1  | Flow-chart highlighting development of InP-based PIN diode switches                                                                                                    | .84 |

| 4.3. 5  | Schematic of a W-band shunt PIN diode SPST switch                                                                                                                      | .85 |

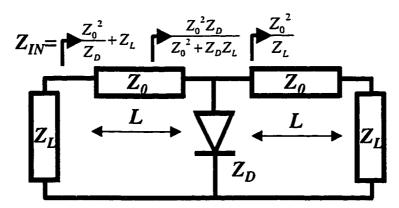

| 4.4. ]  | InGaAs PIN diode equivalent circuit in ON- and OFF-state                                                                                                               | .87 |

| 4.5.    | Calculated performance of a W-band InGaAs shunt PIN SPST                                                                                                               | .88 |

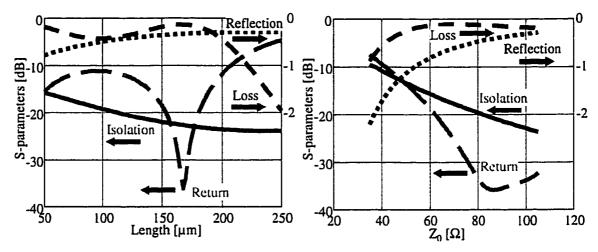

| 4.6. (  | Optimization of W-band InGaAs PIN diode SPST design                                                                                                                    | .89 |

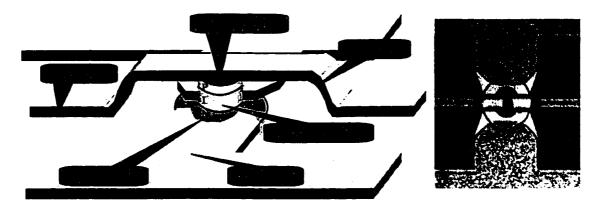

| 4.7.    | Step-by-step depiction of InP backside via-hole technology                                                                                                             | .90 |

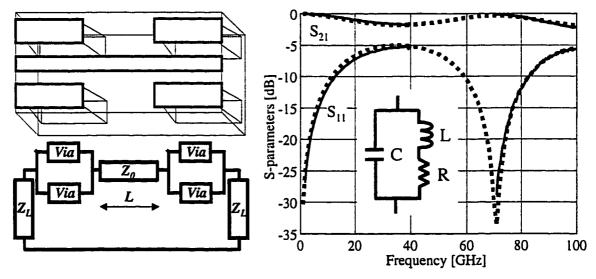

| 4.8. \$ | Schematics and S-parameters of the InP microstrip "through" lines: measured (solid lines) and calculated (dashed lines)                                                | .91 |

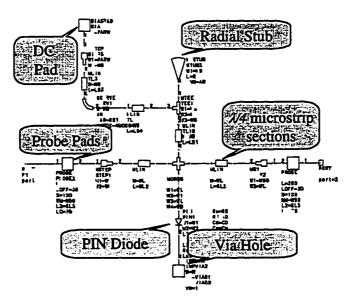

| 4.9.    | Libra schematics of a microstrip W-band SPST switch with a single shunt InGaAs PIN diode                                                                               | .93 |

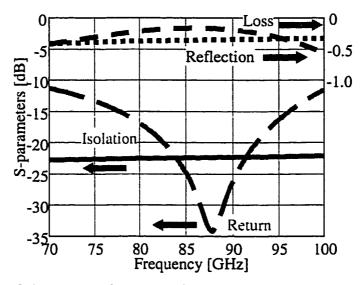

| 4.10.   | Simulated S-parameters of a W-band InGaAs PIN diode SPST                                                                                                               | .93 |

| 4.11.   | Schematic of a SPST with two shunt InGaAs PIN diodes                                                                                                                   | .94 |

| 4.12.   | Comparison of single-diode (dashed) and double-diode (solid) 94GHz InGaAs PIN SPST switches employing 5µm-diameter diodes                                              | .95 |

| 4.13.   | . Photograph of an InGaAs PIN diode SPST switch                                                                                                                        | .96 |

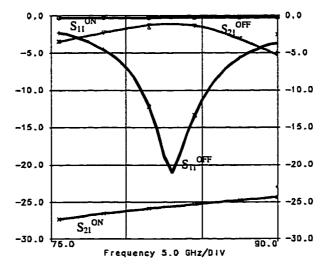

| 4.14.   | . Measured S-parameters of W-band InGaAs PIN SPST switch                                                                                                               | .96 |

| 4.15. | S-parameters of 87GHz InGaAs PIN diode SPST measured with the "capacitive" (solid) and "inductive" (dashed lines) loading of the biasing pad | 97 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.16. | Photographs of the single-diode and double-diode InGaAs PIN diode SPST switches.                                                             | 98 |

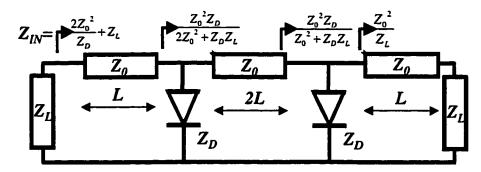

| 4.17. | Schematic of double-diode PIN diode SPST switch                                                                                              | 98 |

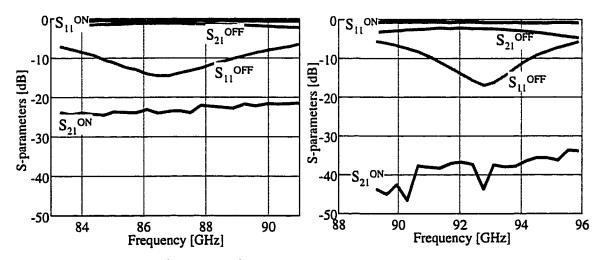

| 4.18. | Performance of the (a) single- and (b) double-diode SPSTs                                                                                    | 99 |

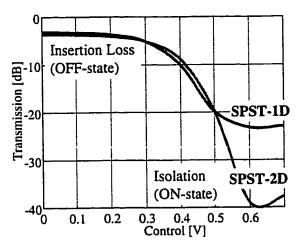

| 4.19. | Dependence of the switching characteristics of InGaAs PIN diode SPST switches on the control bias voltage                                    | 00 |

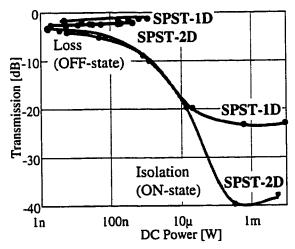

| 4.20. | Tradeoff between DC power consumption and performance for W-band InGaAs PIN single-diode (SPST-1D) and double-diode (SPST-2D) SPST switches  | 00 |

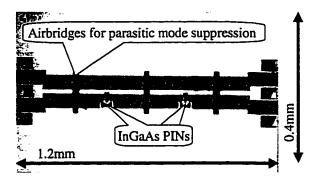

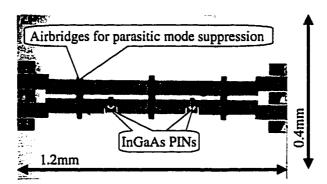

| 4.21. | A photograph of coplanar W-band InGaAs PIN-diode SPST switch 1                                                                               | 03 |

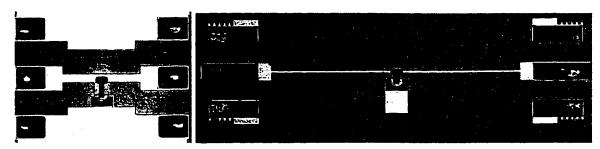

| 4.22. | Coplanar and microstrip Ka-band switches employing shunt-mounted InGaAs PIN diodes                                                           | 03 |

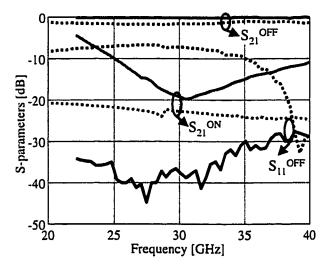

| 4.23. | Measured characteristics of coplanar (solid lines) and microstrip (dotted lines) Ka-band InGaAs PIN diode SPST switches                      | 04 |

| 4.24. | Schematics of investigated PIN-CPW transitions: (a) asymmetric-shunt, (b) symmetric-shunt, and (c) series transition                         | 05 |

| 4.25. | Design schematic and photograph of the developed low-inductance PIN-CPW transition                                                           | 05 |

| 4.26. | Equivalent circuit of an InGaAs PIN diode with a low-inductance PIN-CPW transition                                                           | 06 |

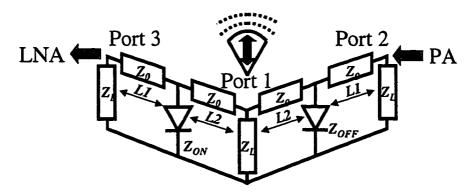

| 4.27. | Schematic of InGaAs PIN diode SPDT switch 1                                                                                                  | 07 |

| 4.28. | Calculated performance of an InGaAs PIN diode SPDT switch                                                                                    | 08 |

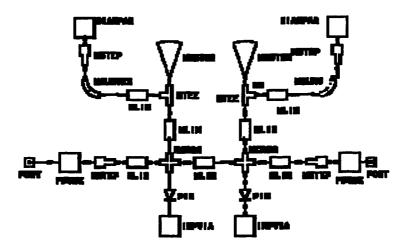

| 4.29. | Layout of coplanar 77GHz InGaAs PIN diode SPDT switch automatically generated by HP EEsof Libra/Academy simulator1                           | 09 |

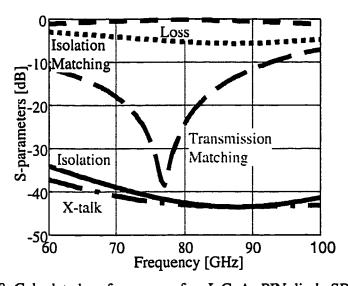

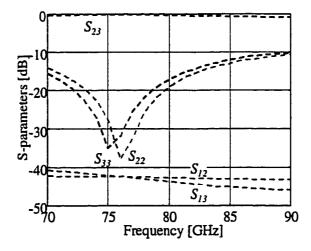

| 4.30. | Simulated S-parameters of a coplanar SPDT switch designed for operation at 77GHz1                                                            | 10 |

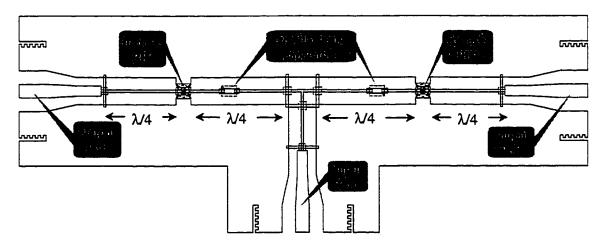

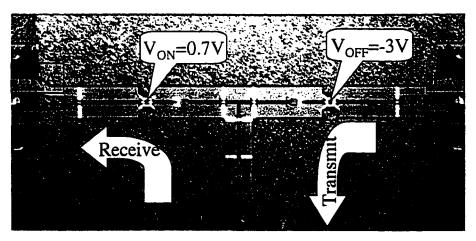

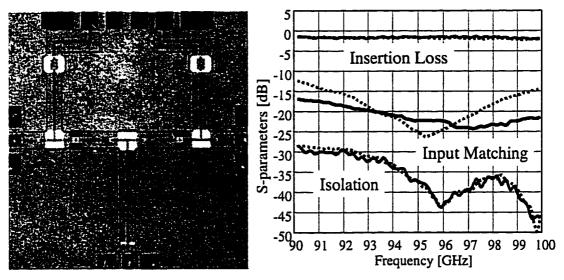

| 4.31. | Photograph of fabricated coplanar 77GHz InGaAs PIN diode SPDT transmit-receive switch                                                        | 11 |

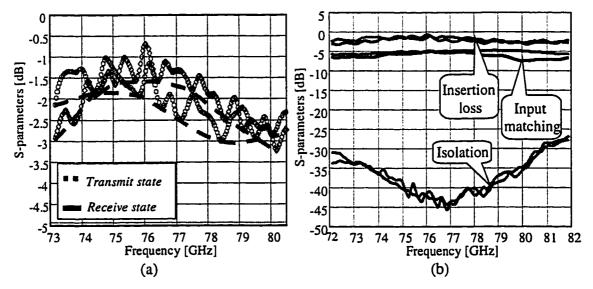

| 4.32. | Insertion loss (a) and isolation (b) of 77GHz InGaAs PIN diode SPDT switch measured for the "receive" and "transmit" directions              | 12 |

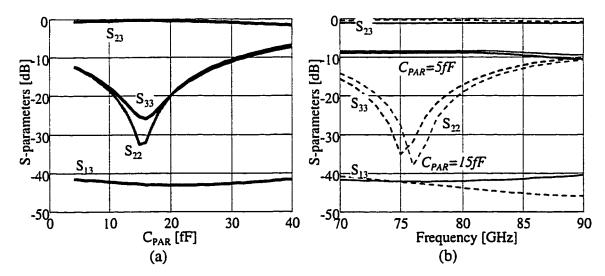

| 4.33. | Impact of the parasitic PIN-diode capacitance on performance of a coplanar 77-GHz InGaAs PIN diode SPDT switch                               | 13 |

| 4.34. | Output crosstalk of 77GHz InGaAs PIN diode SPDT switch1                                                                                      | 14 |

| 4.35.  | Photograph and characteristics of 94-GHz InGaAs PIN diode SPDT transceiver switch with on-chip integrated biasing networks                             | 14 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

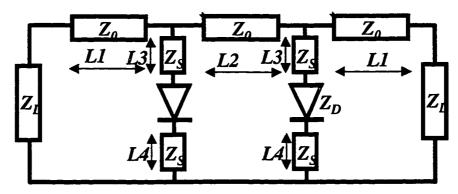

| 4.36.  | Schematics of a loaded-line InGaAs PIN diode phase shifter 1                                                                                           | 16 |

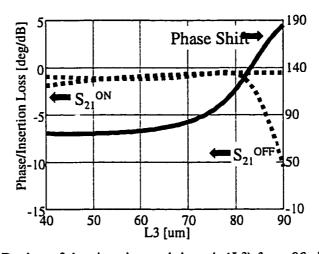

| 4.37.  | Design of the shunting stub length (L3) for a 90-degree phase shift of 94GHz InGaAs PIN loaded-line phase shifter                                      | 17 |

| 4.38.  | Calculated high-frequency characteristics of a 94GHz 90-degree InGaAs PIN diode loaded-line phase shifter1                                             | 17 |

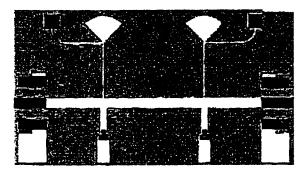

| 4.39.  | Photograph of microstrip 94-GHz InGaAs PIN diode loaded-line 90-degrees phase shifter with on-chip integrated biasing networks                         | 18 |

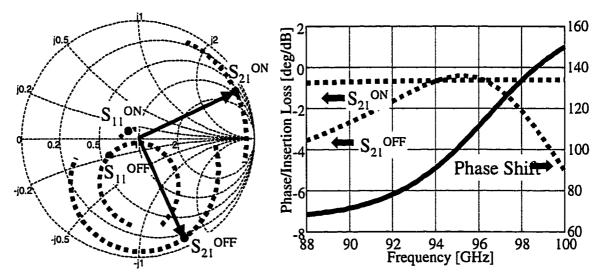

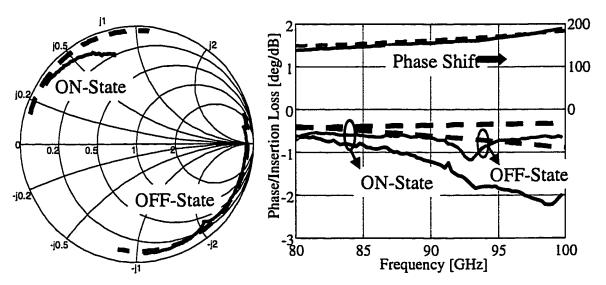

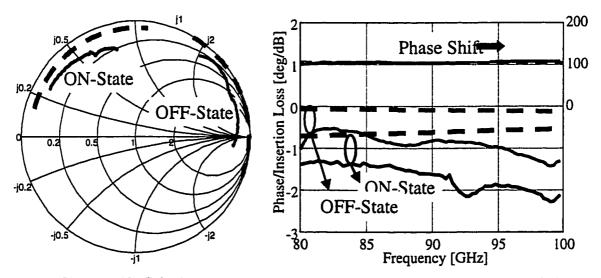

| 4.40.  | Experimental (solid lines) and simulated (dashed lines) characteristics of microstrip 94-GHz InGaAs PIN diode loaded-line 90-degrees phase shifter.    | 19 |

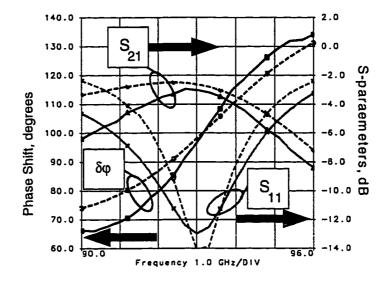

| 4.41.  | . Calculated (dashed lines) and measured (solid-lines) characteristics of W-band InGaAs PIN time-delay phase shifters                                  | 20 |

| 4.42.  | . Calculated (dashed lines) and measured (solid-lines) characteristics W-band InGaAs PIN constant <i>phase-shift</i> phase shifters                    | 21 |

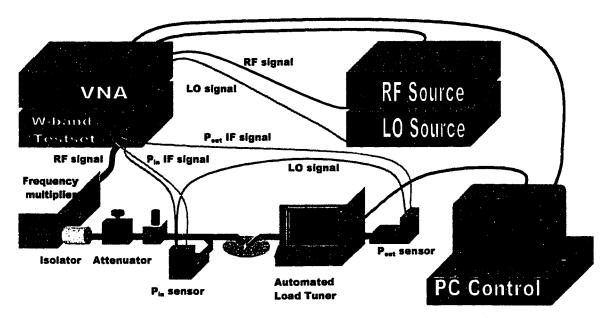

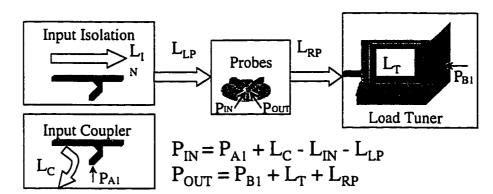

| 5.1.5  | Schematics of an automated W-band on-wafer load-pull system l                                                                                          | 25 |

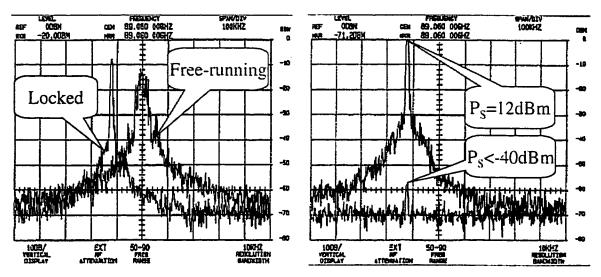

| 5.2. I | Injection-locking of free-running IMPATT oscillatorl                                                                                                   | 26 |

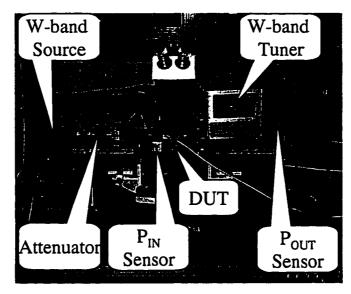

| 5.3. I | Photograph of the automated W-band on-wafer load-pull system 1                                                                                         | 27 |

| 5.4. I | Power-flow schematics of the calibrated part of the load-pull system 1                                                                                 | 27 |

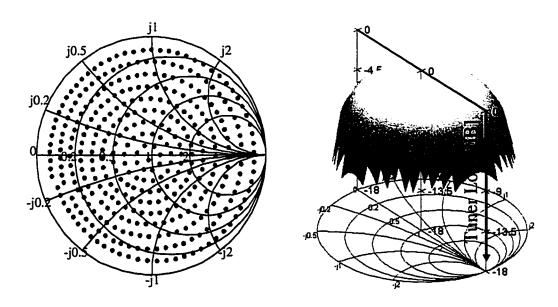

| 5.5. 0 | Calibration of the W-band Electromechanical Tuner at 77GHz 1                                                                                           | 28 |

| 5.6. ( | Constant loss contours measured for a "through" calibration standard l                                                                                 | 29 |

| 5.7.   | A photograph of coplanar W-band InGaAs PIN-diode SPST switch l                                                                                         | 30 |

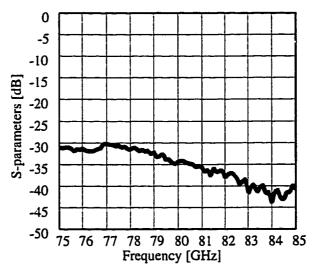

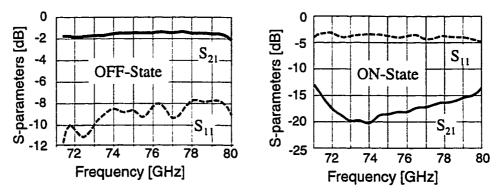

| 5.8. 5 | S-parameters of InGaAs PIN SPST switch in the OFF-state                                                                                                | 31 |

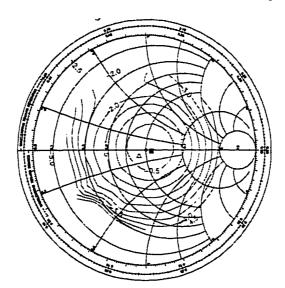

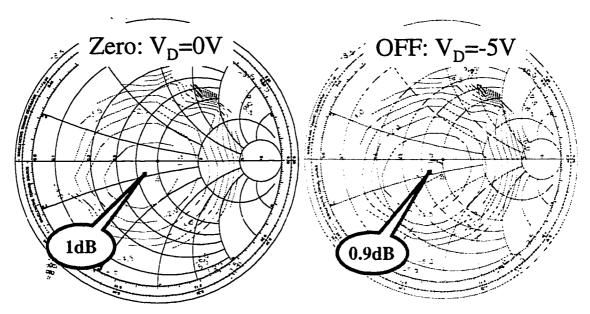

| 5.9.   | W-band constant-loss contours for OFF-state InGaAs PIN SPST1                                                                                           | 32 |

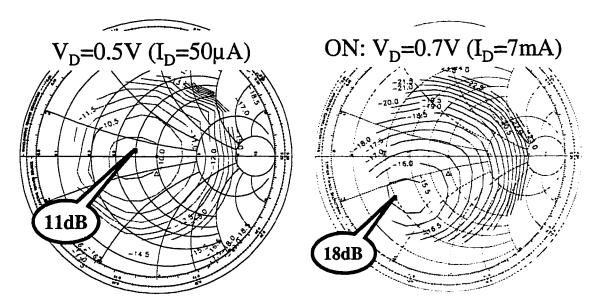

| 5.10.  | . W-band constant-loss contours for ON-state InGaAs PIN SPST1                                                                                          | 33 |

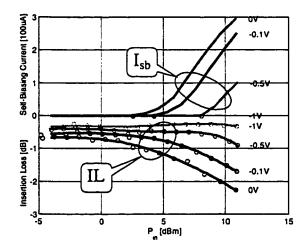

| 5.11.  | Insertion loss (IL) and self-biasing current ( $I_{SB}$ ) of InGaAs PIN switch measured at $I02GHz$ as a function of input power and bias conditions 1 | 34 |

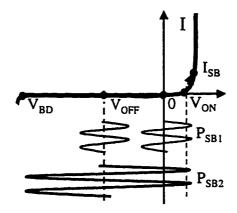

| 5.12.  | Relation between power-handling capabilities, self-biasing effects, and biasing conditions of InGaAs PIN diode switches                                | 35 |

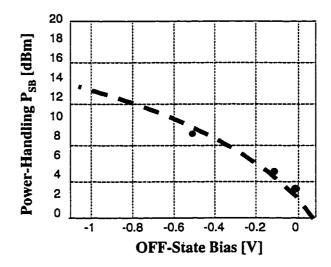

| 5.13.  | Calculated and measured power handling ( <i>P<sub>SB</sub></i> ) of InGaAs PIN SPST switches at <i>102GHz</i>                                          | 36 |

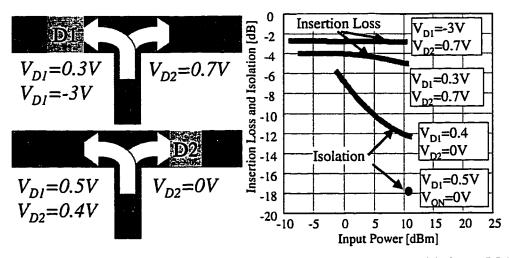

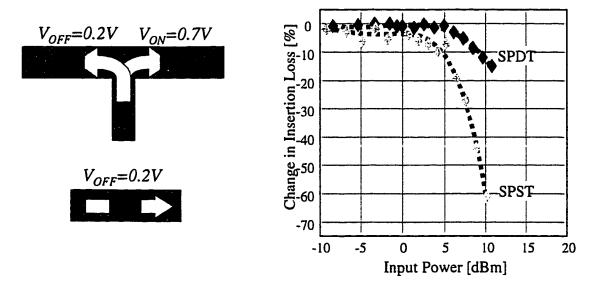

| 5.14.  | Power dependence of insertion loss and isolation of InGaAs PIN diode SPDT switch for different bias conditions                                         | 37 |

| 5.15.  | . Comparison of power-handling capabilities of SPST and SPDT InGaAs PIN diode switches                                                                 | 38 |

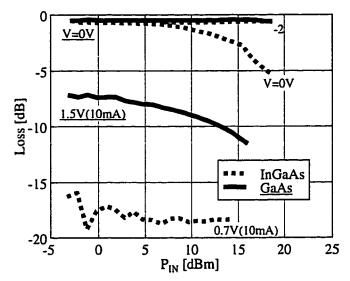

| 5.16. | Large-signal characteristics of InGaAs and GaAs PIN SPST switches measured at 8GHz                                                                       | 39  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

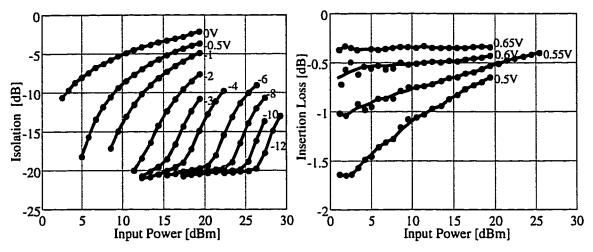

| 5.17. | Large-signal switching characteristics of series InGaAs PIN diodes 1                                                                                     | 40  |

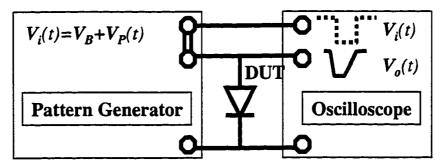

| 5.18. | PIN switching characterization using a setup consisting of a digital pattern generator, DUT, and high-speed digitizing oscilloscope                      | 41  |

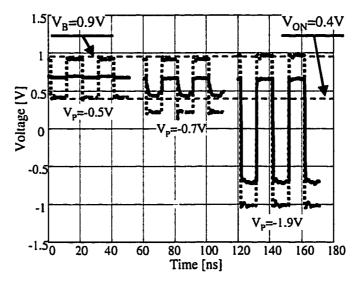

| 5.19. | Input (dashed line) and output (solid line) voltage waveforms were obtained in the switching experiment with $V_B=+0.9V$ , $V_P=-0.5$ , -0.7, and -1.9V. | 42  |

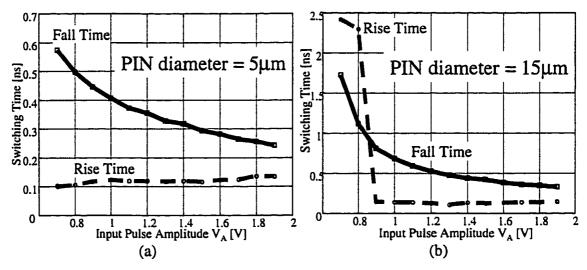

| 5.20. | Dependence of switching times on the pulse amplitude for (a) small and (b) large InGaAs PIN diodes                                                       | 43  |

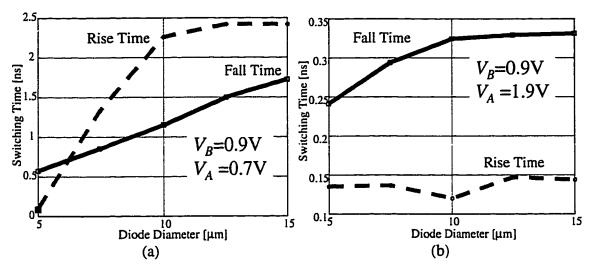

| 5.21. | Dependence of switching times on InGaAs PIN diode size for (a) small and (b) large pulse conditions                                                      | 45  |

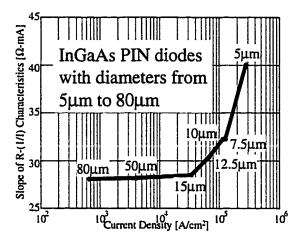

| 5.22. | The dependence of the slope of R-1/I characteristics on the diode size for InGaAs PIN diodes                                                             | 46  |

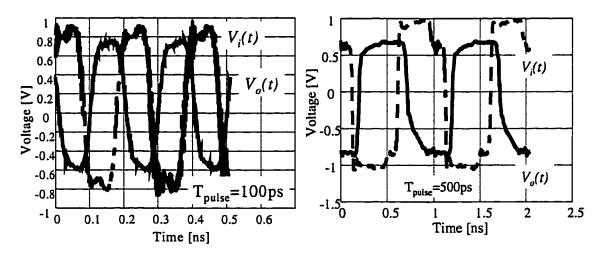

| 5.23. | Input $V_i(t)$ and output $V_o(t)$ waveforms of $5\mu m$ -diameter InGaAs PIN diode SPST switch at high-switching rate of $5Gps$ and $1Gps$              | 46  |

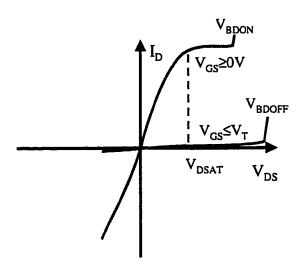

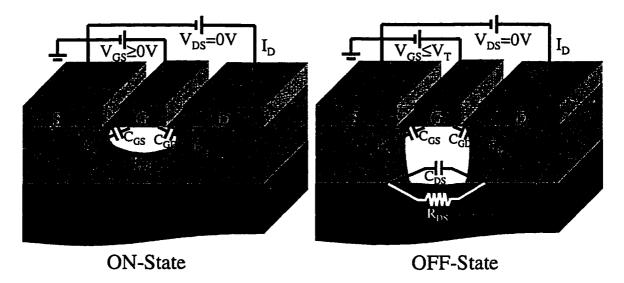

| 6.24. | Schematics of a switching FET in the ON and OFF states with their corresponding small-signal equivalent-circuit elements                                 | 50  |

| 6.25. | $I_D$ - $V_{DS}$ characteristic of a switching FET shows the difference in the channel resistance under the ON- and OFF-state biasing conditions I       | 51  |

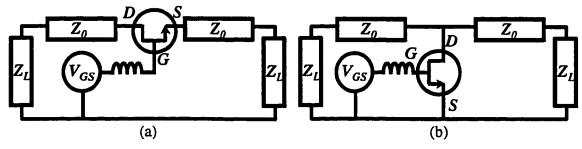

| 6.26. | SPST FET switches with a) a series FET and b) a shunt FET                                                                                                | 53  |

| 6.27. | Schematics of a switching FET in the ON and OFF states with their corresponding small-signal equivalent-circuit elements                                 | .54 |

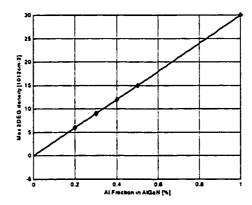

| 6.28. | 2DEG charge density vs. Al fraction in AlGaN/GaN HFETs                                                                                                   | 56  |

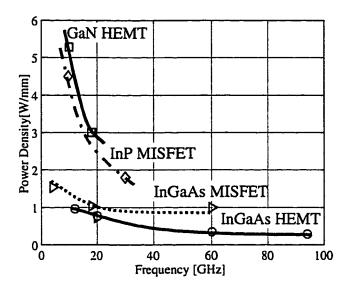

| 6.29. | Output Power density vs. frequency for GaN- and III-V-based FETs l                                                                                       | 58  |

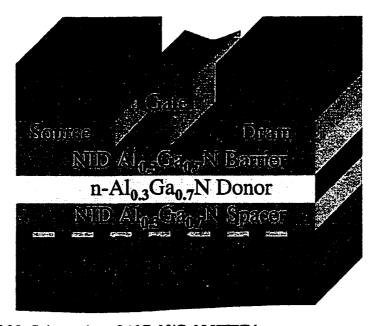

| 6.30. | Schematics of AlGaN/GaN HFET layersl                                                                                                                     | .59 |

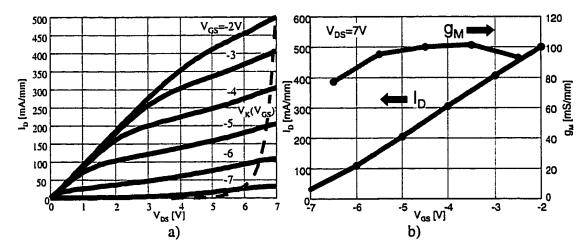

| 6.31. | I <sub>D</sub> -V <sub>DS</sub> (a) and transfer characteristics (b) of AlGaN/GaN HFET with 200μm gate width                                             | .60 |

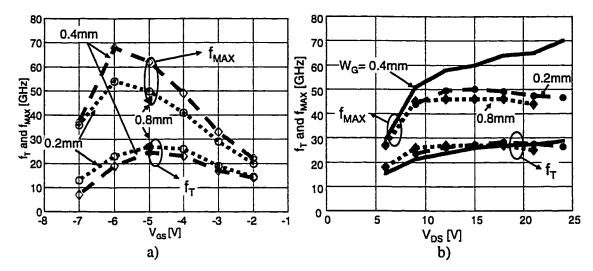

| 6.32. | Bias dependence of $f_{MAX}$ and $f_T$ for AlGaN/GaN HFETs with various gate widths                                                                      | .61 |

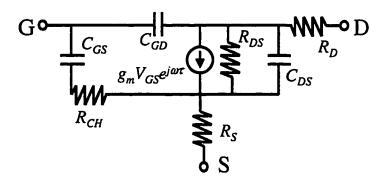

| 6.33. | . Small-signal equivalent-circuit of common-source AlGaN/GaN HFET 1                                                                                      | 61  |

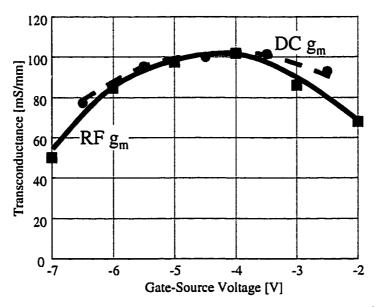

| 6.34. | Dependence of DC and RF transconductance on V <sub>GS</sub> for 0.2mm AlGaN/GaN HFETs                                                                    | .62 |

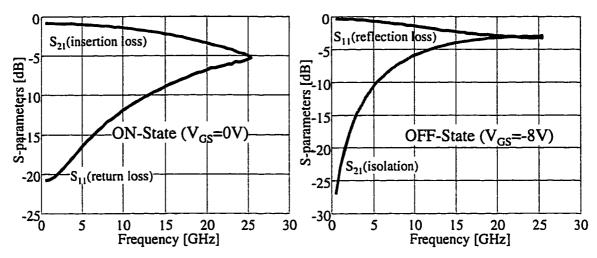

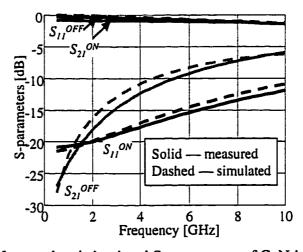

| 6.35. | . Common-Gate S-parameters of GaN-based HFETs 1                                                                                                          | 64  |

| 6.36. | . Measured and simulated S-parameters of GaN-based HFETs 1                                                                                               | 64  |

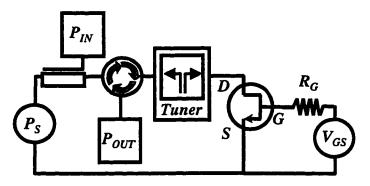

| 6.37. | Automatic On-wafer Reflection Load-Pull Characterization Setup 1                                                                                         | 65  |

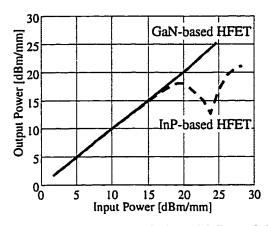

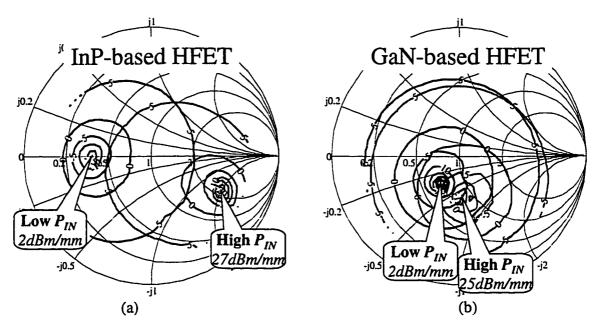

| 6.38. | Saturation power characteristics of InP- and GaN-based HFETs                                                                                                                                  | 166 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.39. | Constant-loss contours evaluated for (a) InP- and (b) GaN-based HFETs under small- and large-signal conditions                                                                                | 167 |

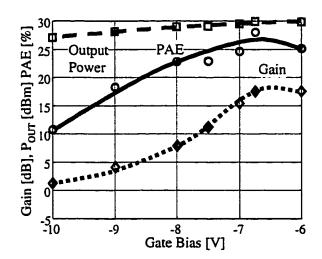

| 6.40. | Dependence of gain, output power, and power-added-efficiency on gate bias of AlGaN/GaN HFET with 1-mm gate width                                                                              | 168 |

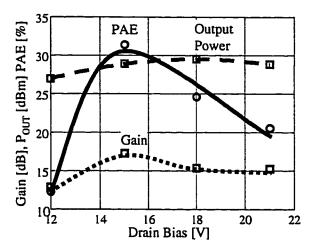

| 6.41. | Dependence of gain, output power, and power-added-efficiency on drain bias of AlGaN/GaN HFET with 1-mm gate width                                                                             | 169 |

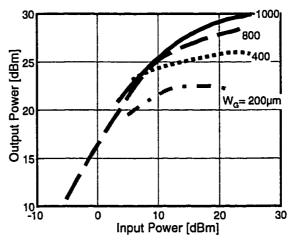

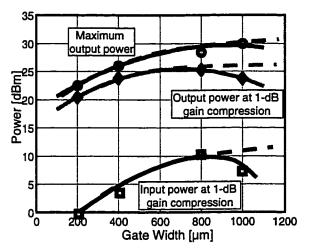

| 6.42. | Power saturation characteristics of AlGaN/GaN HFETs as a function of gate width.                                                                                                              | 170 |

| 6.43. | Scalability of AlGaN/GaN HFET power characteristics shown by the dependence of output and input power at 1-dB gain compression on gate width                                                  | 171 |

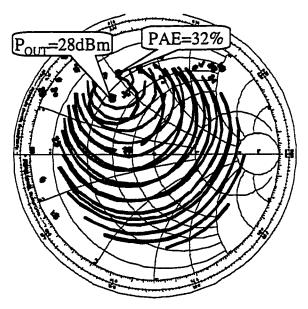

| 6.44. | Constant output power ( $P_{OUT}$ ) and constant power-added efficiency ( $PAE$ ) contours for AlGaN/GaN HFET with $800\mu m$ gate width under $P_{IN}=22dBm$ , $V_{DS}=12V$ , $V_{GS}=-5V$ . | 171 |

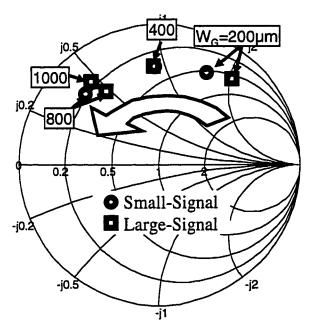

| 6.45. | Dependence of small- and large-signal output impedance of AlGaN/GaN HFETs on gate widths                                                                                                      | 172 |

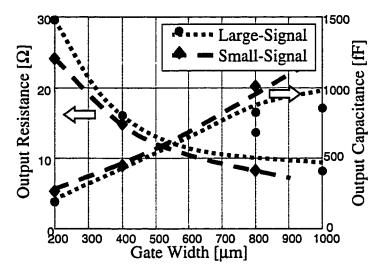

| 6.46. | Small- and large-signal values of the output capacitance and output resistance as a function of gate width                                                                                    | 173 |

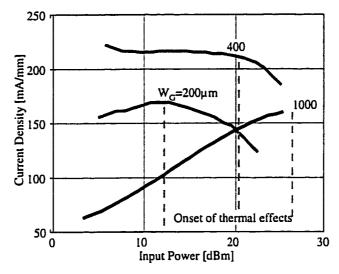

| 6.47. | Dependence of self-biased drain current on input power measured during power saturation measurements of AlGaN/GaN HFETs with various gate widths                                              | 174 |

| 6.48. | High-contrast Nomarsky photographs of AlN/GaN layers                                                                                                                                          | 177 |

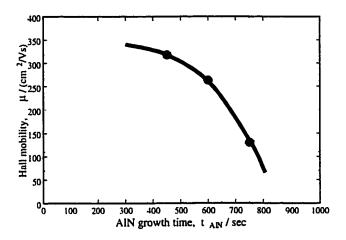

|       | Dependence of electron mobility on the growth time of the AlN barrier layer.                                                                                                                  |     |

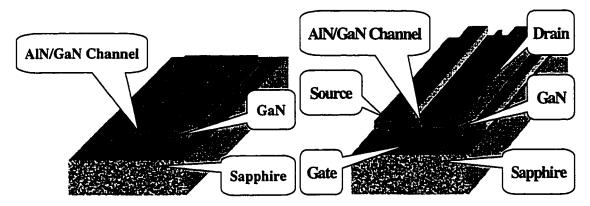

| 6.50. | Process flow of the AlN/GaN MISFET fabrication.                                                                                                                                               | 178 |

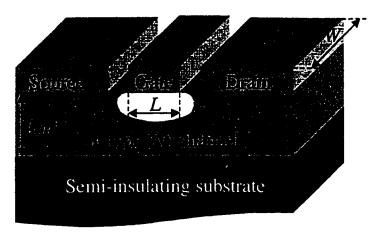

| 6.51. | SEM photograph of a GaN-based FET grown and fabricated at the University of Michigan                                                                                                          | 179 |

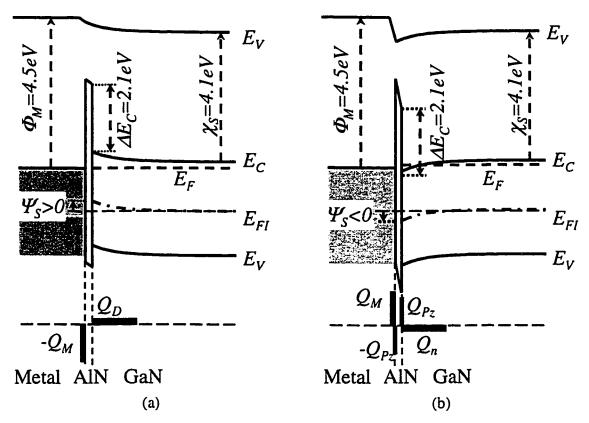

| 6.52. | A schematic of energy band diagram and charge distributions in AlN/GaN MIS structure without (a) and with (b) polarization effects                                                            | 181 |

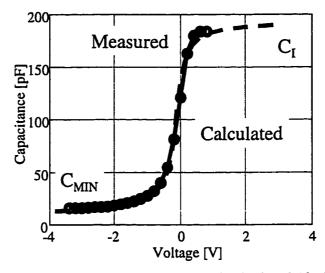

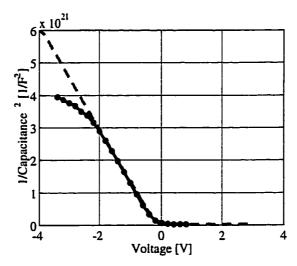

| 6.53. | Measured (solid and markers) and calculated (dashed) C-V characteristics of AlN/GaN MISFET gate diodes                                                                                        | 183 |

| 6.54. | C-V characteristics of AlN/GaN MISFETs used to evaluate the properties of AlN/GaN interface                                                                                                   | 183 |

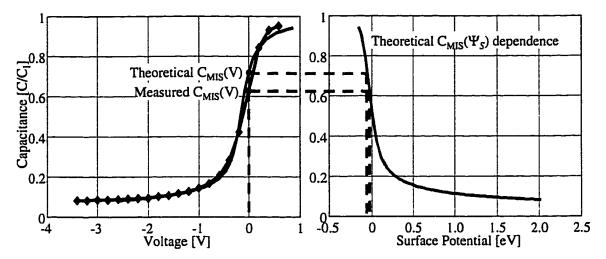

| 6.55. | Determination of experimental and theoretical $\Psi_S$ - $V$ characteristics                                                                                                                  | 185 |

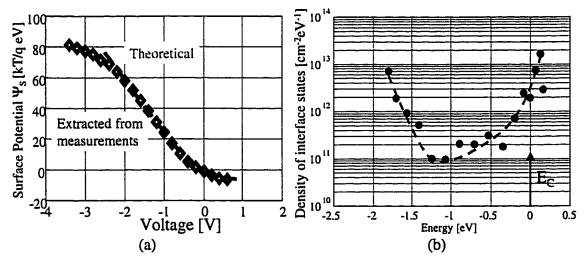

| 6.56. | Theoretical and measured $\Psi_S$ - $V$ characteristics and extracted density of interface states $D_{rr}$ in AlN/GaN MISFETs                                                                 | 185 |

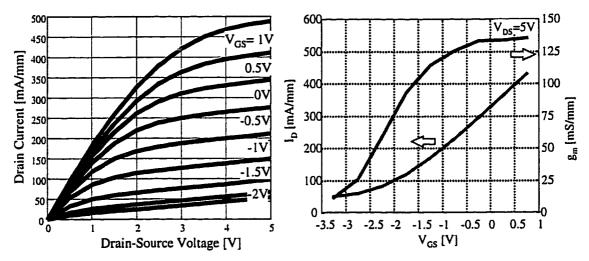

| 6.57.         | DC I-V and transfer characteristics of AlN/GaN MISFETs                                                                                                          | 186 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.58.         | Scaling of $I_{DSS}$ and $g_m$ with gate length                                                                                                                 | 186 |

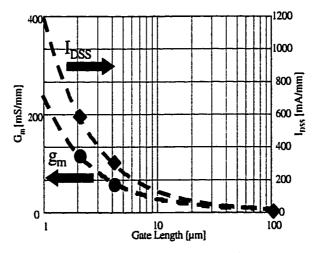

|               | I <sub>DS</sub> -V <sub>DS</sub> characteristics showing the device breakdown features                                                                          |     |

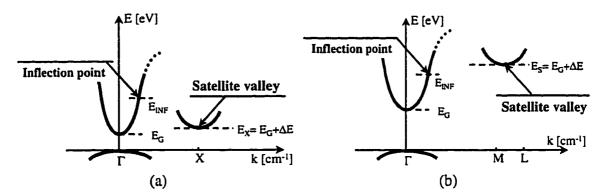

| 7.1. S        | chematic of (a) GaAs and (b) GaN band structure                                                                                                                 | 191 |

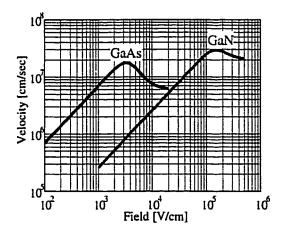

| 7.2. C        | Comparison of v-F characteristics between GaAs and GaN                                                                                                          | 192 |

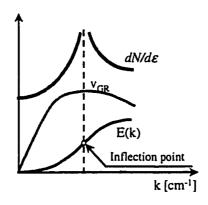

|               | Electron group velocity $(v_{GR})$ and differential density of states $(dN/d\varepsilon)$ in the vicinity of the inflection point of the conduction band $E(k)$ | 194 |

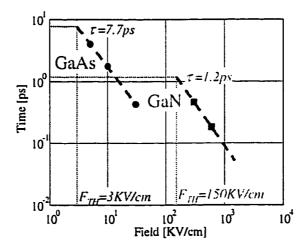

| 7.4. E        | valuation of electron transfer time $\tau_{TE}$ in GaAs and GaN                                                                                                 | 197 |

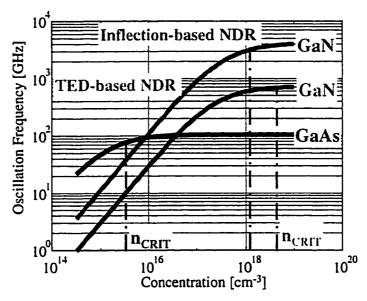

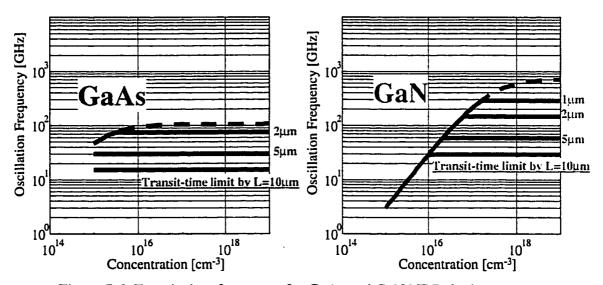

| 7.5. F        | requency constraints of GaAs and GaN NDR devices                                                                                                                | 199 |

| 7.6. T        | ransit-time frequency for GaAs and GaN NDR devices                                                                                                              | 200 |

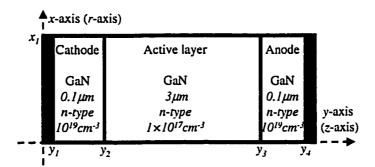

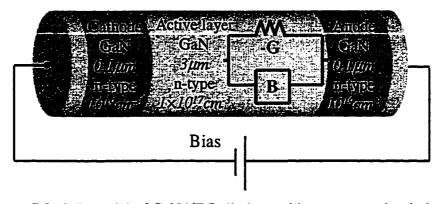

| 7.7. T        | wo-dimensional cross-section of considered GaN NDR diodes                                                                                                       | 205 |

| 7.8. <i>3</i> | -D model of GaN NDR diode used in computer simulations                                                                                                          | 206 |

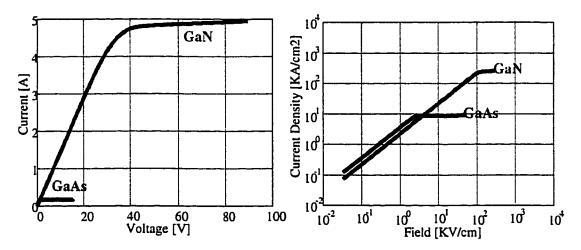

|               | OC I-V and J-F characteristics simulated for a GaN NDR diode and a GaAs Gunn diode                                                                              | 207 |

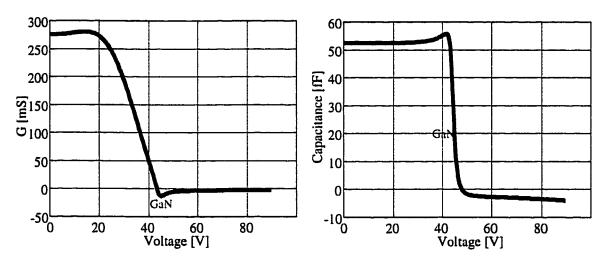

| 7.10.         | Bias dependence of $G_D$ and $C_D$ for a GaN NDR diode                                                                                                          | 208 |

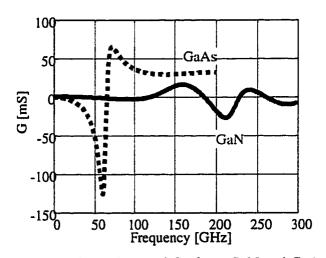

| 7.11.         | Frequency dependence of $G_D$ for a GaN and GaAs NDR diodes                                                                                                     | 209 |

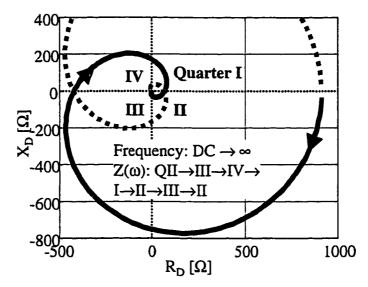

|               | Nyquist diagram of resistance and reactance as a function of frequency for a GaN NDR diode.                                                                     | 211 |

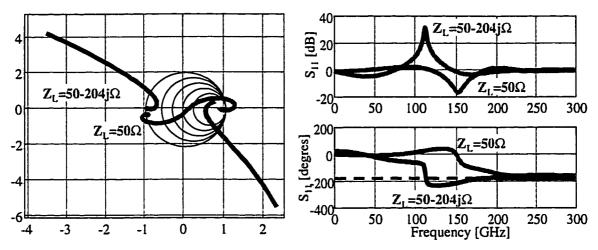

|               | Nyquist diagram and Bode plot of the GaN NDR diode oscillator obtained for $Z_L$ =50 $\Omega$ and $Z_L$ =50-204 $j\Omega$                                       | 212 |

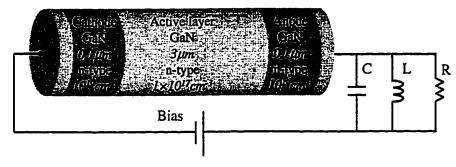

| 7.14.         | Schematics of GaN-based NDR diode oscillator                                                                                                                    | 213 |

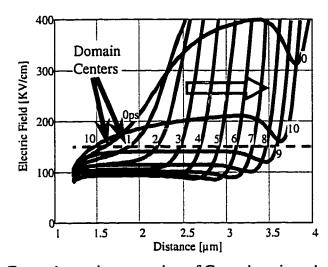

| 7.15.         | Formation and propagation of Gunn domains: electric field                                                                                                       | 214 |

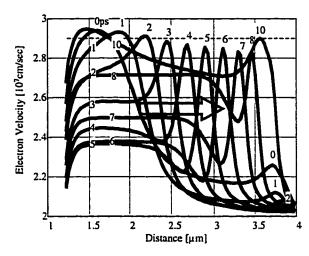

| 7.16.         | Formation and propagation of Gunn domains: electron velocity                                                                                                    | 215 |

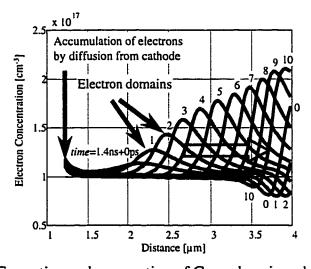

| 7.17.         | Formation and propagation of Gunn domains: electric concentration                                                                                               | 215 |

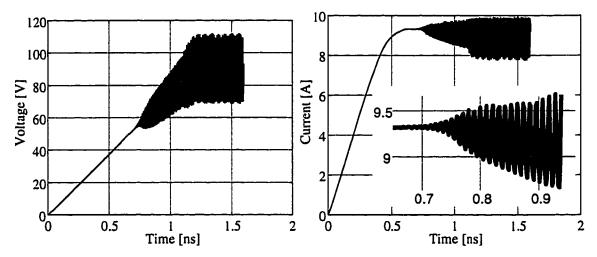

| 7.18.         | Voltage and current waveforms of GaN NDR diode oscillator                                                                                                       | 216 |

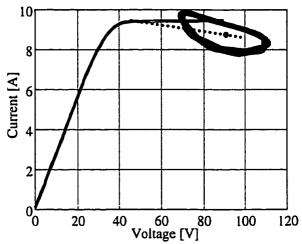

| 7.19.         | Dynamic load-line and I-V characteristic of GaN NDR oscillator                                                                                                  | 217 |

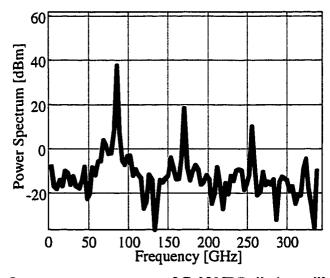

| 7.20.         | Output power spectrum of GaN NDR diode oscillator                                                                                                               | 217 |

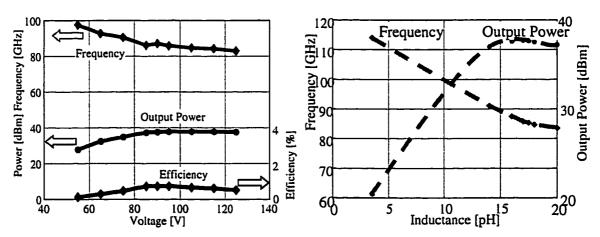

|               | Variation of the output power, frequency, and efficiency of GaN NDR diode oscillator with bias and terminating load                                             | 218 |

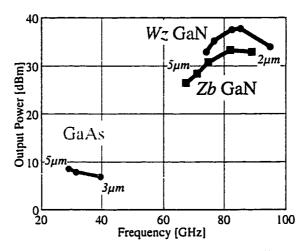

|               | Power-frequency diagram for GaN NDR diode and GaAs Gunn diode oscillator for devices with active layer width between 2 and 5um                                  | 220 |

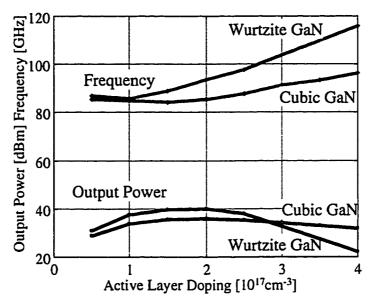

|               | Power and frequency of Wz and Zb GaN NDR diode oscillators as a function of the doping of the active layer                                                      | 221 |

# LIST OF TABLES

| 7   | ٣,   | h | 16 |

|-----|------|---|----|

| - 1 | - 21 | n | 16 |

|      |                                                                                                           | _     |

|------|-----------------------------------------------------------------------------------------------------------|-------|

| 1.1. | Microwave diodes and FETs in microwave control circuits                                                   | 6     |

| 1.2. | Semiconductor material parameters and microwave signal generator of merit for GaAs, InP, and GaN [38,]    | 12    |

| 2.1. | Extraction of the value of parasitic capacitance $C_{PAR}$                                                | 42    |

|      | MOCVD-grown InGaAs PIN Diode Layers                                                                       |       |

| 3.2. | MBE-grown InGaAs PIN Diode Layers                                                                         | 57    |

| 3.3. | MBE-grown GaAs PIN Diode Layers                                                                           | 58    |

| 3.4. | Surface Breakdown of InGaAs PIN layers                                                                    | 59    |

| 3.5. | List of InGaAs PIN wafers and extracted DC I-V parameters                                                 | 65    |

| 3.6. | List of InGaAs PIN diode wafers and extracted C-V parameters                                              | 70    |

| 4.1. | W-band equivalent-circuit elements of InGaAs PIN diodes                                                   | 87    |

| 6.1. | High-Power Capability s of Merit for GaN Normalized to GaAs                                               | . 157 |

| 6.2. | High-Frequency Small-Signal Equivalent Circuit Parameters of HFETs $(V_{DS}=15V \text{ and } V_{GS}=-5V)$ | . 162 |

| 6.3. | Power Saturation Characteristics of AlGaN/GaN Power HFETs for Various Gate Widths                         | . 170 |

| 6.4. | Comparison of DC Predicted and RF Measured Output Power Density of AlGaN/GaN HFETs                        | . 175 |

| 7.1. | Semiconductor material parameters of GaAs and GaN                                                         |       |

|      | (N×L) <sub>0</sub> Products and Critical Doping Levels for GaN and GaAs                                   |       |

# CHAPTER 1 INTRODUCTION

# 1.1. Status of Compound Semiconductor RF Technology

Compound semiconductor technology has in the past served specialized applications dealing primarily with defense systems. Its commercial potential became more evident over the last decade with the increased interest in wireless applications, such as cellular and automotive electronics. Over this period, shipments of III-V-based devices and integrated circuits (IC) have grown four times to almost \$10 billion dollars [1]. Despite the fact that this represents only a small fraction of the semiconductor market where silicon remains the key technology, the expansion of compound-semiconductor applications to commercial systems confirms their vitality and uniqueness. Transition of GaAs- and InP-based technology from research laboratories into commercial sector was prompted by the decrease of government funding and commercialization of microwave and millimeter-wave spectra, which occurred in early 1990s. Shift from performancedriven low-volume military applications to cost-driven high-volume commercial applications was accompanied by departure from labor-intense hybrid technology. Monolithic microwave integrated circuit (MMIC) technology was much more compatible with the low-cost minimum-assembly requirements of the high-volume commercial production and was, therefore, intensively pursued. The use of high-performance devices, such as high-electron mobility transistors (HEMTs) and heterojunction bipolar transistors (HBTs) was on the other hand limited, since it required expensive epitaxial layers. First commercial applications favored low-cost GaAs MESFET MMICs, which were made using ion-implantation techniques and offered performance competitive with and often superior to RF Si electronics. However, strong competition in the commercial market and declining costs of epitaxial growth have revived strong demand for high-performance MMICs employing GaAs- and InP-based HEMTs and HBTs [2]. In fact, today, GaAs-based HBTs is the leading technology for cellular-handset power-amplifier applications [1].

This growth of compound-semiconductor analog electronics is expected to continue in the future, as there is an increasing demand for larger communication bandwidths and higher frequency of operation. Among high-volume emerging applications where compound semiconductor RF technology has a unique role are local multiple-point distribution systems (*LDMS*) at 28GHz [3], next-generation communication and imaging systems at 94GHz [45], and W-band automotive radars at 77GHz [6]. At these frequencies, InP-based HEMT electronics has advantages over GaAs in terms of output power, power-added-efficiency, and noise. InP-based HBTs are also expected to compete with GaAs-based technologies for cellular handset applications since they allow lower voltage operation and improved power-added-efficiency. Provided that cost is not prohibitively high, it is expected that InP-based MMIC technology will find significant commercial application for microwave, millimeter- and sub-millimeter-wave systems projected for the next decade [2].

The 1990s have also been the witness to the emergence of wide bandgap GaN-based semiconductors with increased electrical strength as viable power device technology. Thus, GaN-based HEMTs demonstrated unattainable by conventional III-V materials power density of 12W/mm [7]. Moreover, the use of wide bandgap materials not only allows increased output power, but also extends the temperature tolerance and the radiation hardness [8]. Due to their unique high-power high-frequency characteristics, GaN-based devices are expected to dominate high-power microwave applications [9]. These include base stations for wireless and satellite communications, automotive electronics and defense applications.

This thesis deals with compound semiconductor devices and circuits for signal control and generation applications. The materials considered for this purpose include both InP- and GaN-based semiconductors as outlined in detail in the next sections.

# 1.2. Role of Signal Control and Generation Circuits in W-band Automotive Radars

Millimeter-wave circuits such as switches, phase shifters, amplifiers, and oscillators demonstrating good performance over larger bandwidths are desired for various applications such as emerging W-band collision-warning, collision-avoidance, and adaptive cruise-control systems (CWS, CAS, ACC) system for the automotive industry [6]. Commercial success of automotive radars is largely contingent upon the development of a monolithic millimeter-wave integrated circuit technology suitable for mass production. Monolithic transmitter-receiver modules integrating power and lownoise amplifiers, mixers, and oscillators operating up to W-band frequency are currently being developed [6, 10]. Such MMICs employ high-performance InP- or GaAs-based HEMTs for signal amplification while microwave diodes are used for signal generation, mixing, and switching.

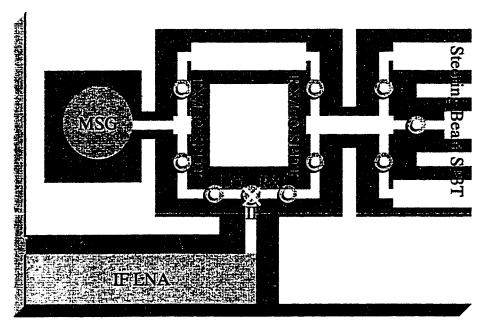

A simplified schematic of a W-band automotive transmitter-receiver front-end module for pulse Doppler configuration is demonstrated in Figure 1.1 following [11]. This design employs a single microwave signal generator (MSG) to provide both transmit (TX) and local oscillator (LO) signals for mixer down-conversion. The signal generation function is implemented using a millimeter-wave oscillator. Two single-pole doublethrow (SPDT) transceiver switches are used to reconfigure the module between "transmit" and "receive" positions. A steering-beam single-pole triple-throw (SP3T) switch is used to select an antenna corresponding to one of the three scanning beams. When the front-end is in the "transmit" (TX) state, the TX signal from the oscillator is directed the selected antenna, while the mixer diode is isolated from all three antennas and the MSG. In the "receive" (RX) state, the transceiver switches connect LO and RX signals to the mixer diode, while the transmission path is blocked. The isolation of the SPDT switches provides the measure of how well the TX or the LO signals are blocked from leaking to undesired ports. The insertion loss is used to characterize power loss in the TX and RF signals incurred due to presence of the switches in the signal path. Low insertion loss ( $\langle IdB \rangle$ ) and high isolation ( $\langle 30dB \rangle$ ) are desired for optimal performance.

Figure 1.1. Block diagram of a W-band automotive front-end module

During the operation, the microwave signal generator is coherently switched between the TX and LO frequencies while the transceiver switches are changed between the TX and RX configurations. The TX signal is sent to a target via one of the selected antennas. After it is reflected from the target, the RF signal is received by the antenna and coherently down-converted by a mixer diode to IF frequencies.

The resolution of the pulse-Doppler radar largely depends on the modulation rate (switching time) of the transceiver switches. Faster switching is required for reduction of "blind range", which measures minimum distance for successful operation. Switching time of *1-2ns* is considered acceptable for automotive applications at present time.

The far range of the radar can be limited the maximum power of the transmitted signal. The transceiver and steering beam switches used in the automotive radars are required to provide switching operation up to high power levels of 13-16dBm [6, 11].

Viable semiconductor devices for implementation of high-power low-loss and high-isolation transceiver switches include microwave PIN diodes and switching FETs. Chapter 4 of this thesis deal with InP-based PIN MMIC switches, while Chapter 6 presents development of wide-bandgap GaN-based HFETs for high-power monolithic switching applications in an attempt to respond to the automotive requirements of low-loss, high-isolation, and high-power switching.

It should be noted that the task of high-power signal generation at W-band is also very challenging. Among various solutions are HEMT- and HBT-based MMICs [10, 12], as well as high-power low-noise Gunn diode oscillators [11]. While the power and frequency capabilities of MMIC oscillators are constantly improving, microwave diode oscillators remain semiconductor devices of choice for W-band and beyond generators. However, the output power available from conventional GaAs- and InP-based Gunn diodes is shown to decrease sharply beyond 100GHz [13]. An application of GaN-based Gunn diodes for high-power signal generation at W-band and higher frequencies is addressed in Chapter 7.

### 1.3. Semiconductor Devices for Control Applications

Monolithic millimeter-wave transceivers integrate signal generators, power amplifiers, down-conversion mixers, low-noise amplifiers, and transceiver switches. High-performance GaAs- and InP-based HEMTs can be used to develop all of the above functions [10], while microwave diodes are best suited for signal generation, down-conversion, and switching applications [6]. Thus, W-band signal generators are often realized using Gunn diodes, while monolithic PIN diode switches are predominantly used for control applications at this frequency.

In general, microwave control circuits can employ FETs (such as MESFETs, MISFETs, and HEMTs), Schottky diodes, or PIN diodes as switching elements. The advantages and disadvantages of using these types of devices are listed in Table 1.1.

MESFETs and HEMTs represent the mainstream millimeter-wave MMIC technology and, thus, FET-based transceiver switches can be easily integrated on the same chip with transmit and receive MMICs. Because the operation of FETs is based on majority carriers with short lifetimes, they generally demonstrate high switching speeds. However, the high resistance of the channel results in large insertion loss and small isolation. The channel resistance is reduced in HEMTs due to the increased 2DEG mobility and charge density in these heterostructure devices, but performance at millimeter-wave frequencies is still poor due to their large OFF-state capacitance inherent in three-terminal devices.

Table 1.1. Microwave diodes and FETs in microwave control circuits

| Devices                           | Advantages                                                                                                                                                                               | Disadvantages                                                                             |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| MESFETs,<br>MISFETs,<br>and HEMTs | <ul> <li>Compatible with MMIC technology</li> <li>Majority carriers operation (fast switching)</li> </ul>                                                                                | <ul><li>High channel resistance</li><li>Low cutoff frequency</li></ul>                    |  |

| Schottky<br>Diodes                | <ul><li>Ease of integration with FETs</li><li>High cutoff frequency</li><li>Majority carrier operation</li></ul>                                                                         | Low power capability                                                                      |  |

| PIN Diodes                        | <ul> <li>High cutoff frequency</li> <li>High power-handling capability</li> <li>Low ON-state resistance</li> <li>Layer structure compatible with<br/>HBTs and optoelectronics</li> </ul> | Minority carrier operation     Layer structure not compatible with FETs                   |  |

| MEM<br>Switches                   | <ul> <li>Very low insertion loss</li> <li>Very high isolation</li> <li>Low DC power consumption</li> </ul>                                                                               | <ul><li>Very slow switching</li><li>High control voltage</li><li>Short lifetime</li></ul> |  |

The power-handling capability of MESFETs and HEMTs is limited by the small breakdown voltage of the Schottky-gate diode and the channel. Excellent microwave power results recently demonstrated using wide bandgap semiconductors [7] suggest a possibility of increasing the power-handling capabilities of FET switches by employing GaN-based HFETs due to increased channel electrical strength, high electron mobility, and excellent 2DEG properties. Wide-bandgap metal-insulator-semiconductor FETs (MISFETs) can be used to further improve power characteristics due to an increased electrical strength of the insulator of the MIS gate. Overall, FETs are best suited for low-frequency low-power applications where insertion losses are not critical while GaN-based HFETs and MISFETs are promising candidates for high-power microwave applications. Use of FET switches at high frequency requires resonance of the OFF-state capacitance with an inductive component. Approaches of this type, combined with the high-breakdown features of GaN-based HFETs offer a possibility of high-power millimeterwave switches using wide bandgap GaN-based semiconductors with high chemical resistance, thermal stability, and radiation hardness [14].

Schottky diodes are easily integrated with active FET-based circuits because the layer structure and fabrication steps are very similar. Diodes with very small OFF-state

capacitance are feasible, but a combination of low breakdown voltage and small area leads to poor power-handling capability. Schottky diodes are best employed in high-speed low-power control circuits.

Microwave PIN diodes combine the advantages of low ON-state resistance and low OFF-state capacitance which leads to very high cutoff frequencies and offers low insertion loss and high isolation performance up and beyond W-band frequencies. High breakdown voltage of PIN structures lends itself to high power-handling capability offered by PIN diodes. However, switching of PIN diodes between the ON and the OFF states occurs by injection and removal minority carriers in and out of the I-layer. Since the switching operation involves minority carriers with long lifetimes, the modulation speeds of PIN diodes is fundamentally slower than in Schottky diodes or FETs. Compound semiconductors demonstrate shorter minority-carrier lifetimes, which allows significantly faster recovery times in GaAs- and InP-based PIN diodes (~1-2ns [15]) compared with Si-based PIN diode switches (~100ns [16]) that is sufficient for most practical radar applications. While PINs and HEMTs use different layer structures, the two devices can be successfully integrated on the same substrate [17]. Moreover, switching PIN diodes can be fabricated as part of standard GaAs or InP-based HBT technology, which extends the range of their applications [18].

Microelectromechanical systems (MEMs) operating using electrostatic and mechanical-tension forces have recently been applied to microwave and millimeter-wave switching [19, 20]. While MEMs do not truly qualify as semiconductor control devices, early results with MEM switches are promising and demonstrate very low insertion losses ( $\sim 0.2 dB$ ), and high isolation ( $\sim 30 dB$ ) up to 40 GHz. MEMs also consume miniscule DC power ( $\sim 1 \mu W$ ), but have severe limitations in terms of switching speed (< 1 MHz), actuation voltages (> 10 V), and reliability ( $\sim 10^6$  switching operations). Further improvements of MEM switches in these areas are expected to take place as this novel technology is matured.

Overall, switching PIN diodes offer the unique combination of high cutoff frequency, low loss, high power-handling and adequate switching-rate capabilities. FETs on the other hand are best employed for lower-power applications. Power handling of

FET switches can be improved by using wide bandgap materials such as GaN in the channel or employing an insulating gate such as in MISFET designs. Both types of devices are addressed in this thesis: PIN diodes are described in Chapters 2 and 3 of this thesis, while wide bandgap GaN-based HFETs and MISFETs are presented in Chapter 6.

#### 1.4. Review of Microwave PIN Diode Switches

High power-handling capability, high cutoff frequency, and low insertion loss won PIN diodes a well deserved central place in the design of microwave control circuits, such as attenuators [21], transceiver switches [4, 16], and phase shifters [22].

In historical perspective, Ge- and Si-based PIN diodes were used for microwave switching as early as in 1956 [23, 24]. Circuits were implemented in a hybrid fashion and successful operation up to millimeter-wave frequencies was demonstrated by 1980s [25]. However, Si devices became less attractive since they were incompatible with the emerging GaAs-based MMIC technology [26]. First successful fabrication of switching GaAs-based PIN diodes was reported in 1983 [27]. In the next several years, various millimeter-wave GaAs PIN diode switches were reported based on different fabrication methods including ion-implanted [16], hybrid-mounted [28], and epitaxially-grown vertical PIN structures [15, 29]. The latter showed superior performance due to the higher quality of the PIN structures and lower parasitics, and quickly replaced FETs as switching elements of choice at millimeter-wave frequencies.

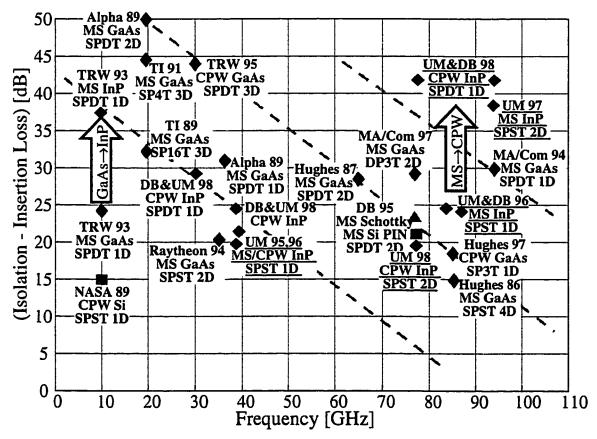

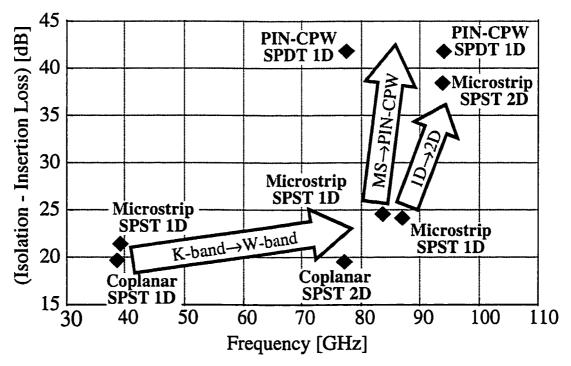

Since single-pole single-throw (SPST) and single-pole double-throw (SPDT) switches are essential elements in design of transmitter-receiver modules, research and development of monolithic PIN switches was continuous all the way through the 90s as demonstrated by the results of Figure 1.2. The diagram, presented in the figure, provides a roadmap of important stages in development of microwave PIN diode switches. Reported in the literature performance of PIN diode switches was plotted on the diagram as a function of frequency. This diagram uses as a measure of performance on/off switching ratio (isolation [dB] *less* insertion loss [dB]). Such definition favors isolation over insertion loss, since high isolation is harder to achieve in a MMIC environment while most MMIC switches have insertion loss between 1 and 2dB. Each reported result is

marked by a three-lines-long legend. The first line lists the name of the company or research lab where the switch was made and the year it was reported. The second line states what monolithic technology — microstrip (MS) or coplanar (CPW) was used in switch design, and what semiconductor was used for fabrication of the switches. Presented data include results obtained with beam-lead Si PINs diodes, GaAs PIN diodes, and InP-based InGaAs PINs of this work. The third line of the captions describes the design of the switch (SPST or SPDT) and number of diodes employed in an SPST arm.

Figure 1.2. Performance-frequency diagram demonstrating development of monolithic PIN diode switches.

Consideration of the switch design and the number of diodes employed are important since, for reasons which will be explained later in this thesis, the isolation in a switch with multiple throws is ~6dB higher than in a single-throw switch and the isolation of an SPST with two diodes (SPST-2D) is roughly twice that of an SPST-1D. Therefore, the performance of an SPST-1D switch with an on/off switching ratio of 24dB is roughly equivalent to that of an SPST-2D with 48dB or that of an SPDT-1D with 30dB.

At the beginning of this work, most research and development work on monolithic microwave switches concentrated on GaAs-based microstrip PIN diode switches [4, 22], while InP-based PIN diodes have been primarily explored for optoelectronic circuits, such as receiver OEICs [17]. Thus, a state-of-the-art microstrip transceiver SPDT switch employing epitaxial GaAs PIN diodes was reported in 1994 and demonstrated *1dB* insertion loss and *30dB* isolation at *94GHz* [4]. However, there are a number of applications where InP-based InGaAs PIN diodes can be more suitable than the conventional GaAs-based PINs. For example, the compatibility of InGaAs PIN diodes with high-frequency InP-based electronics offers several additional advantages for the realization of millimeter-wave functions, such as the possible integration of switching PIN diodes with InP-based HBTs and HEMTs. Thus, integrated photoreceivers with HBT- and HEMT-based amplifiers have been demonstrated using InGaAs PIN photodiodes [17, 30]. The higher operation frequencies achievable with the use of InP-based electronics opens the road to building new imaging-radar systems, as well as to minimizing the size and therefore the cost of automotive collision avoidance systems.

InGaAs also has a high electron mobility (≥10,000cm²/Vs) and, thus, InGaAs PIN diodes can offer reduced series resistance resulting in low-loss and high-isolation switches. Moreover, the low (0.78eV) bandgap of InGaAs is useful for achieving low turn-on voltage, which reduces DC power consumption and offers a better match with the low-power InP-based electronics. X-band InGaAs PIN switches fabricated using the InP-based HBT process confirmed these expectations and demonstrated superior compared with GaAs-based PIN switches performance at only half the power consumption [31]. The insertion loss for InGaAs PIN switch was 0.89dB while the isolation exceeded 35dB compared with 0.82dB and 25dB of GaAs circuit, as shown with an arrow in Figure 1.2.

Up until the 1990s, all reported monolithic PIN diode switches were designed using microstrip technology [4,15-22,31]. Coplanar-waveguide technology offered smaller parasitics and lower-cost processing, but it lacked good circuit elements and models. A first report on coplanar PIN switches using beam-lead diodes was published as early as 1989 [32], but not until 1995 had the coplanar GaAs PIN diode switch been realized [33]. The first results on InGaAs/InP-based PINs at millimeter-wave frequencies

were obtained in the course of this work [34], and excellent switching characteristics up to 40GHz were demonstrated using a coplanar InGaAs PIN SPST switch, described in detail in Chapter 3. This, and further applications of InGaAs PIN diodes to the design and realization of monolithic integrated PIN switches for millimeter-wave operation are marked by underlined captions in Figure 1.2 and are presented in Chapter 4.

A W-band SPST microstrip InGaAs PIN diode switch was developed and demonstrated state-of-the-art performance of 1.3dB insertion loss and 25dB isolation at 83GHz [35]. A high-isolation version of this microstrip SPST switch employing two InGaAs PIN diodes demonstrated a record isolation of >35dB at 94GHz [36]. Based on recent advances in electromagnetic simulators, coplanar circuit models became available for circuit design, and W-band coplanar InGaAs PIN diode SPDT transceiver switches were demonstrated in 1998 with isolation of more than 43dB at 77GHz and 94GHz. [37]. A combination of the low ON-state resistance and a low-inductance of coplanar InGaAs PIN diodes, developed in this work, resulted, in this case, in the highest isolation reported for any W-band PIN switches (see Figure 1.2).

Overall, millimeter-wave InP-based InGaAs PIN diode switches appear to have superior characteristics to that of conventional GaAs-based designs while offering compatibility with high-frequency InP-based HEMT and HBT electronics as desired for emerging W-band radars and imaging systems. This type of switches is extensively investigated in Chapters 3 through 5 of this thesis, which present work on their MMIC implementation at various frequencies as well as studies of their DC, high-frequency, power, and switching properties.

#### 1.5. GaN-Based NDR Diodes for Microwave Signal Generators

Microwave signal generators are essential elements of a millimeter-wave frontend transceiver module as was shown in Section 1.2. Active microwave diodes based on negative differential resistance (NDR) effect are primary devices for high power and lownoise signal generation at millimeter-wave frequencies. Thus, GaAs- and InP-based Gunn diodes based on transferred-electron effect have been successfully employed for microwave and millimeter-wave signal generation up and even beyond W-band frequencies [13, 38]. However, power and frequency capabilities of Gunn diodes made with conventional III-V compound semiconductors are limited, especially at millimeter-wave frequencies.

On the other hand, studies of the fundamental properties of wide bandgap III-V nitrides indicate that velocity-field characteristics in these materials also exhibit negative differential resistance (NDR). Although further confirmation is needed regarding the presence of NDR in GaN, NDR oscillators made with this wide bandgap semiconductor appear to offer several advantages over conventional III-V compounds. These include increased electrical strength and a higher threshold field, which leads to increased output power in GaN-based devices. Table 1.2 summarizes some of these properties in an attempt to show the superior features of GaN-based electronics. A record output power density for any microwave FET of 7W/mm was recently obtained with GaN-based devices [7] in support of the discussed advantages of wide bandgap GaN-based materials.

Table 1.2. Semiconductor material parameters and microwave signal generator figure of merit for GaAs, InP, and GaN [38, 39]

| Material | F <sub>TH</sub> , [KV/cm] | $F_B$ [MV/cm] | VSAT,<br>[cm/sec]   |                     | $Pf^2Z=F_B^2v_{PEAK}^2/4$ [39] [normalized to GaAs] |

|----------|---------------------------|---------------|---------------------|---------------------|-----------------------------------------------------|

| GaAs     | 3.5                       | 0.4           | $0.6 \times 10^{7}$ | 1.5×10 <sup>7</sup> | 1                                                   |

| InP      | 10.5                      | 0.5           | 1.2×10 <sup>7</sup> | 3×10 <sup>7</sup>   | 36                                                  |

| GaN      | ~80-150                   | 2             | 2×10 <sup>7</sup>   | 2.9×10 <sup>7</sup> | 2000-7000                                           |

A first analysis of the use of GaN for NDR diode realization is reported in this thesis. Presented in Chapter 6 results discuss the microwave potential of GaN-based signal generators in terms of the expected frequency and power characteristics of GaN NDR oscillators as a function of bias, doping, frequency, and termination impedance of the resonant cavity.

# 1.6. Objective and Scope of the Thesis

The main objective of this thesis is to advance the development of InP- and GaNbased devices and MMICs for microwave and millimeter-wave applications. For this purpose, switching InP-based InGaAs PIN diodes were developed. Their high-frequency characteristics were studied and device and epitaxial layer design were optimized for millimeter-wave control applications. A low-parasitics high-impedance microstrip and coplanar InP-based MMIC technology was developed in order to enhance performance of InP-based millimeter-wave PIN diode switches. W-band SPST and SPDT transceiver switches were designed and fabricated, and record performance was demonstrated at 77GHz and 94GHz. An automatic on-wafer W-band load-pull system was developed for this purpose and was employed to evaluate the large-signal characteristics of InP-based PIN diodes and W-band MMICs directly at their design frequency. The concept of GaN-based microwave signal generators was proposed and the first analysis of the expected frequency and power capabilities of GaN NDR diode oscillators is presented.

The thesis starts with the description of the fundamental characteristics of switching PIN diodes presented in Chapter 2. The physics of DC and high-frequency characteristics of InGaAs PIN diodes are presented together with the developed numerical simulation approach based on the quasi three-dimensional drift-diffusion method. Chapter 3 starts by optimization of the PIN diode design and epitaxial layers for W-band switching applications, performed on the basis of the developed simulation techniques. The optimization study is followed by description of fabrication technology developed to fabricate monolithic integrated InGaAs PIN diodes. DC and small-signal high-frequency characteristics of the fabricated devices are presented, and small-signal equivalent-circuit parameters of InGaAs PIN diodes are extracted for use in circuit design.

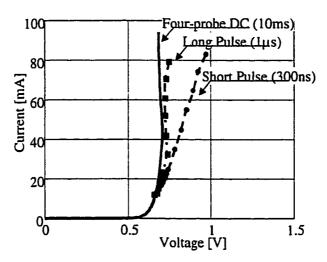

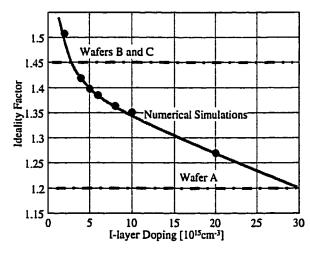

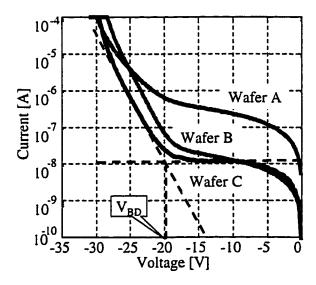

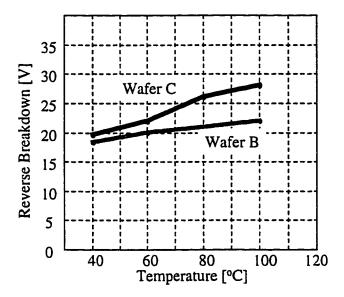

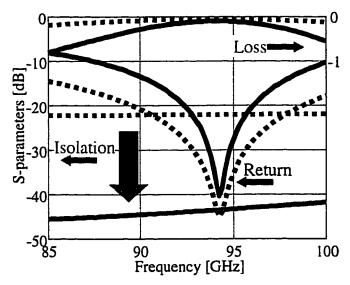

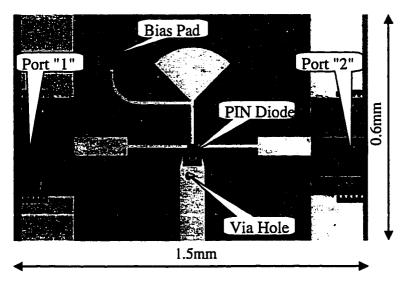

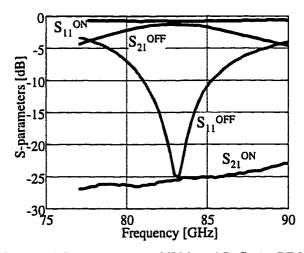

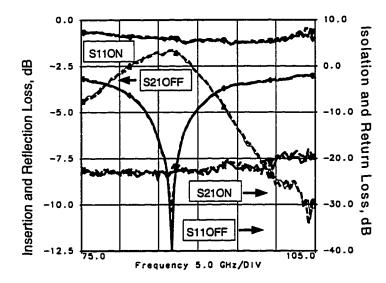

Design, fabrication, and characterization techniques used to realize W-band amplitude- and phase-control MMICs are presented in Chapter 4. Both microstrip and coplanar InP-based MMIC technologies were developed and applied for fabrication of W-band switches and phase-shifters. Record-high isolation of >40dB and low insertion loss of 1.1-1.7dB was demonstrated using InP-based low-parasitics coplanar InGaAs PIN SPDT switches designed for transceiver applications at 77 and 94GHz. The evaluation of PIN diode switching and power-handling capabilities is presented in Chapter 5. The design of an automated on-wafer W-band load-pull measurement system and its application to characterization of large-signal characteristics of W-band InP-based PIN switches are also included in Chapter 5.