# Three Dimensional Integration and Packaging Using Silicon Micromachining

by

#### Alexandros D. Margomenos

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2003

Doctoral Committee:

Professor Linda P.B.Katehi, Chair Assistant Professor Katsuo Kurabayashi Associate Professor Amir Mortazawi Professor Khalil Najafi Professor Kamal Sarabandi © Alexandros D. Margomenos 2003 All Rights Reserved To my family

# ACKNOWLEDGEMENTS

First and foremost, I would like to thank my advisor Prof. Linda Katehi, for her guidance, and continuous support. Her technical expertise and her vast knowledge in the field of silicon micromachining and high frequency design enabled me to perform the tasks required for the completion of this thesis. Prof. Katehi has provided me with instrumental advice and understanding and I feel fortunate to have the opportunity to work with her. I would also like to thank my committee members for their support: Prof. Katsuo Kurabayashi, Prof. Amir Mortazawi, Prof. Khalil Najafi, and Prof. Kamal Sarabandi. I need to especially acknowledge Prof. Najafi for providing assistance on the reliability testing of the fabricated RF MEMS package and Prof. Sarabandi for sharing his expertise and providing key insights into several of the problems that I encountered during this thesis.

None of the work presented in this thesis would have been possible without the contributions of the senior graduate students of the Radiation Laboratory: Dr. Katherine Herrick, who was my mentor in the SSEL laboratory, Dr. Lee Harle, Dr. Jim Becker, Dr. Mark Casciato, Prof. Rhonda Drayton, Dr. Raushanda Henderson, Prof. John Papapolymerou, Prof. Costas Sarris, Prof. Manos Tentzeris, Dr. J.D. Shumpert, Dr. Stefan Legault, Prof. Saeed Mohammadi, Dr. Jeremy Muldavin, Prof. Scott Barker, Dr. Andy Brown, Dr. Guan-Leng Tan, Dr. Joe Hayden, Sergio Pacheco, Dr. Kavita Goverdhanam , Prof. Dejan Filipovic. Thank you to my colleagues for your friendship and advice: Prof. Dimitris Peroulis, Ron Reano, Dimitris Psychoudakis, Yongshik Lee, Prof. Bill Chappell, Yongming Cai, and Dr. Jad Rizk. I have also had the pleasure of working with the new generation of graduate students: Yumin Lu, Rosa Lahiji, Michael Reiha, Abbas Abbaspour, Farshid Aryanfar, Tim Hancock, Kok Yang Lee, Bernhard Schoenliner, Rick Kindt, and Gong Xun. Over the last 7 months I had the pleasure of working with: Dr. Kazem Sabet, Dr. Werner Thiel, Dr. Donghoon Chun, Dr. Kyoung Yang, Eray Yasan, Thomas Chan, Sue Duncan and everyone else at EMAG Technologies.

The work presented will never have been completed without the SSEL technical and administrative staff who work long hours to keep the equipment running: Dr. Dennis Grimard, Jim Kulman, Brian VanDerElzen, Phil Collica, and especially Jorge Himenez for all his help with the EV-501 bonder. I would also like to thank Mr. T.J. Harpster for training me in the use of the autoclave chamber at the MEMS reliability laboratory. Both the presented research and my education were made possible due to the generous funding of: NASA Jet Propulsion Laboratory (NAS7-1407, Task Order 15139), National Science Foundation, and Army Research Laboratory (CTA DAAD-19-01-2-0008).

Thank you to all my friends both here in Ann Arbor and in Thessaloniki, Greece. Last but not least, I am most thankful to my family for their boundless love and support.

# TABLE OF CONTENTS

| DEDICATION  | Ν                                                                          | ii   |

|-------------|----------------------------------------------------------------------------|------|

| ACKNOWLE    | DGEMENTS                                                                   | iii  |

| LIST OF TAE | BLES                                                                       | viii |

| LIST OF FIG | URES                                                                       | ix   |

| LIST OF API | PENDICES                                                                   | xiii |

| CHAPTERS    |                                                                            |      |

| 1 Introd    | uction                                                                     | 1    |

| 1.1         | Motivation                                                                 | 1    |

| 1.2         | Silicon Micromachining                                                     | 2    |

|             | 1.2.1 Physics of Silicon Semiconductors                                    | 2    |

|             | 1.2.2 Wet Anisotropic Etching                                              | 3    |

|             | 1.2.3 Deep Reactive Ion Etching                                            | 5    |

| 1.3         | Packaging for RF MEMS Switches                                             | 6    |

| 1.4         | Simulation Techniques                                                      | 11   |

| 1.5         | Fabrication Facilities                                                     | 11   |

| 1.6         | Measurement Techniques                                                     | 12   |

| 1.7         | Dissertation Overview                                                      | 13   |

| 2 Isolati   | on in Three Dimensional Integrated Circuits                                | 15   |

| 2.1         | Introduction                                                               | 15   |

| 2.2         | Design of Isolation Architectures                                          | 19   |

| 2.3         | Fabrication of Isolation Structures                                        | 20   |

|             | 2.3.1 X-band Designs                                                       | 20   |

|             | 2.3.2 W-band Designs $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 21   |

| 2.4         | Theoretical and Experimental Results                                       | 22   |

|             | 2.4.1 Single-layer Isolation                                               | 24   |

|             | 2.4.2 Multi-layer Isolation                                                | 25   |

| 2.5         | Conclusions                                                                | 34   |

| 3 | Low-L   | oss Interconnects                                                                   | 38 |

|---|---------|-------------------------------------------------------------------------------------|----|

|   | 3.1     | Introduction                                                                        | 38 |

|   | 3.2     | Theoretical Analysis                                                                | 41 |

|   | 3.3     | Coplanar Waveguides on Low-Resistivity Silicon Substrates .                         | 42 |

|   |         | 3.3.1 Fabrication Process                                                           | 42 |

|   |         | 3.3.2 Theoretical and Experimental Results                                          | 43 |

|   |         | 3.3.3 Design Rules                                                                  | 47 |

|   | 3.4     | Thin Film Microstrip Lines on Low-Resistivity Silicon Substrat                      |    |

|   |         | 3.4.1 Fabrication Process                                                           | 48 |

|   |         | 3.4.2 Theoretical and Experimental Results                                          | 50 |

|   | 3.5     | Thin Film Microstrip Lines on Quartz Substrates                                     | 54 |

|   |         | 3.5.1 Optical Polymers                                                              | 54 |

|   |         | 3.5.2 Design and Fabrication Process                                                | 55 |

|   |         | 3.5.3 Theoretical and Experimental Results                                          |    |

|   | 3.6     | Conclusions                                                                         | 58 |

|   |         |                                                                                     |    |

| 4 | Silicon | Micromachined Evanescent Mode Filters                                               | 60 |

|   | 4.1     | Introduction                                                                        | 60 |

|   |         | 4.1.1 Basic Theory                                                                  | 61 |

|   |         | 4.1.2 Quality Factor of an Evanescent Mode Resonator                                | 62 |

|   | 4.2     | Design Process                                                                      | 64 |

|   |         | 4.2.1 Geometrical Properties                                                        | 64 |

|   |         | 4.2.2 External Coupling                                                             | 66 |

|   |         | 4.2.3 Two-pole Filter Design                                                        | 68 |

|   | 4.3     | Fabrication Process                                                                 | 69 |

|   | 4.4     | Silicon Micromachining of Convex Corners                                            | 71 |

|   |         | 4.4.1 Addressing Undercutting of Convex Corners                                     | 71 |

|   |         | 4.4.2 Test Results $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$   | 72 |

|   | 4.5     | Measured Results                                                                    | 73 |

|   | 4.6     | Tunable Evanescent Mode Filters                                                     | 77 |

|   |         | 4.6.1 Tuning of the Capacitive Post                                                 | 79 |

|   |         | 4.6.2 Tuning of the Coupling Slots                                                  | 80 |

|   | 4.7     | Conclusions                                                                         | 81 |

|   |         |                                                                                     |    |

| 5 |         | Micromachined Packages for RF MEMS Switches                                         | 86 |

|   | 5.1     | Introduction                                                                        | 86 |

|   |         | 5.1.1 RF MEMS Switches                                                              | 86 |

|   |         | 5.1.2 Packaging Techniques                                                          | 88 |

|   |         | 5.1.3 Previous Work in Three-Dimensional Interconnects                              | 90 |

|   |         | 5.1.4 On-Wafer Packaging for RF MEMS Switches                                       | 91 |

|   | 5.2     | Initial Attempt for Packaging of RF MEMS                                            | 94 |

|   |         | 5.2.1 Design Process $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 94 |

|   |         | 5.2.2 Fabrication Procedure                                                         |    |

|   |         | 5.2.3 Measured Results                                                              | 97 |

|   | 5.3     | Improved RF Transition                                                              | 99 |

|         |       | 5.3.1 Design Process                                                                            |     | . 99  |

|---------|-------|-------------------------------------------------------------------------------------------------|-----|-------|

|         |       | 5.3.2 Measured Results                                                                          |     | . 102 |

|         | 5.4   | RF Transition Utilizing Multilevel Finite Ground Copl                                           |     |       |

|         |       | Waveguides                                                                                      |     | . 104 |

|         |       | 5.4.1 Introduction                                                                              |     | . 104 |

|         |       | 5.4.2 Fabrication Procedure                                                                     |     | . 106 |

|         |       | 5.4.3 Passivation Issues                                                                        |     | . 109 |

|         |       | 5.4.4 Measured Results                                                                          |     | . 113 |

|         | 5.5   | Conclusions                                                                                     |     | . 115 |

| 6 In    | nprov | ed RF Package for Hermetic Sealing                                                              |     | . 117 |

|         | 6.1   | Introduction                                                                                    |     |       |

|         |       | 6.1.1 Importance of Hermetic Sealing                                                            |     |       |

|         |       | 6.1.2 Thermocompression Bonding                                                                 |     |       |

|         |       | 6.1.3 Accelerated Testing Techniques                                                            |     |       |

|         |       | 6.1.4 Reliability Metrology                                                                     |     |       |

|         | 6.2   | Improved RF Transition Design                                                                   |     |       |

|         |       | 6.2.1 Removal of Parasitic Resonances                                                           |     |       |

|         |       | 6.2.2 Fabrication Procedure for Improved Hermeticity                                            |     |       |

|         |       | 6.2.3 Wafer-to-Wafer Alignment Technique                                                        |     |       |

|         |       | 6.2.4 Measured Results                                                                          |     |       |

|         | 6.3   | Hermeticity Testing                                                                             |     |       |

|         |       | 6.3.1 Testing Structure                                                                         |     |       |

|         |       | 6.3.2 Testing Procedure                                                                         |     |       |

|         |       | 6.3.3 Measured Results                                                                          |     |       |

|         | 6.4   | Conclusions                                                                                     | ••• | . 147 |

| 7 C     |       | sions $\ldots$ |     |       |

|         | 7.1   | Summary                                                                                         |     |       |

|         | 7.2   | Future Work                                                                                     |     |       |

|         |       | 7.2.1 Evanescent Mode Filters                                                                   |     |       |

|         |       | 7.2.2 Packaging of RF MEMS                                                                      | ••• | . 152 |

| APPEND  | ICES  | 5                                                                                               | ••• | . 157 |

| BIBLIOG | RAF   | РНҮ                                                                                             |     | . 167 |

# LIST OF TABLES

#### Table

| 1.1 | Packages for RF MEMS                                                  | 6   |

|-----|-----------------------------------------------------------------------|-----|

| 1.2 | Commercially available RF packages.                                   | 8   |

| 1.3 | Commercially available RF packages (cont.).                           | 9   |

| 1.4 | MEMS Packages.                                                        | 10  |

| 3.1 | Characteristics of optical polymers                                   | 55  |

| 4.1 | Characteristics of compensating structures (e: etch depth, all dimen- |     |

|     | sions are in $\mu$ m)                                                 | 73  |

| 6.1 | Results for packages under vacuum                                     | 145 |

| 6.2 | Results for packages under 1 atm of dry air                           | 148 |

|     |                                                                       |     |

# LIST OF FIGURES

## Figure

| 1.1  | Anisotropically etched features in (100) oriented silicon wafers                  | 4  |

|------|-----------------------------------------------------------------------------------|----|

| 1.2  | Measurement set-up                                                                | 13 |

| 2.1  | Alignment of silicon wafers using glass fibers                                    | 21 |

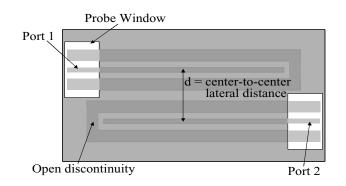

| 2.2  | Schematic for laterally separated FGC lines showing center-to-center              |    |

|      | separation and location of probe windows.                                         | 22 |

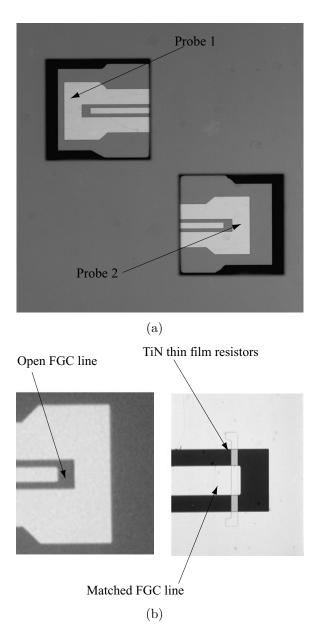

| 2.3  | W-band circuits. (a) Packaged FGC lines printed on a 100 $\mu \mathrm{m}$ silicon |    |

|      | wafer. (b) Detailed view of open and matched FGC line terminations.               | 23 |

| 2.4  | W-band measured and numerical results for laterally separated FGC                 |    |

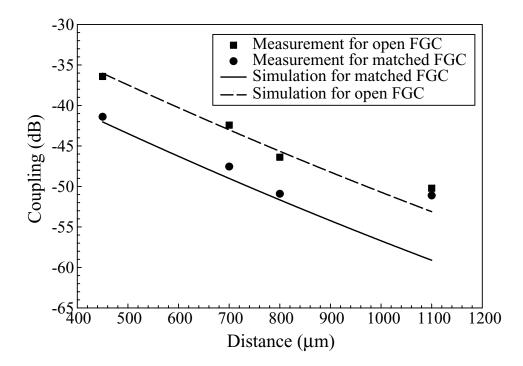

|      | lines showing coupling versus center-to-center spacing                            | 25 |

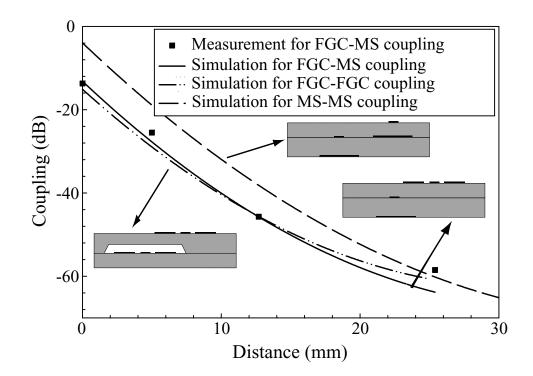

| 2.5  | X-band measured and numerical results for vertically separated FGC                |    |

|      | and microstrip lines showing coupling versus center-to-center spacing.            | 26 |

| 2.6  | W-band FGC lines printed on two 100 $\mu$ m silicon wafers                        | 26 |

| 2.7  | W-band measured and numerical results for vertically separated FGC                |    |

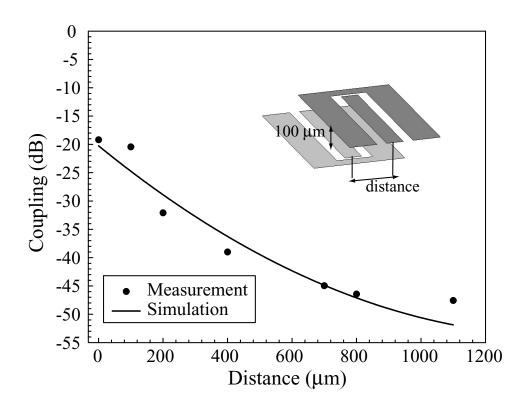

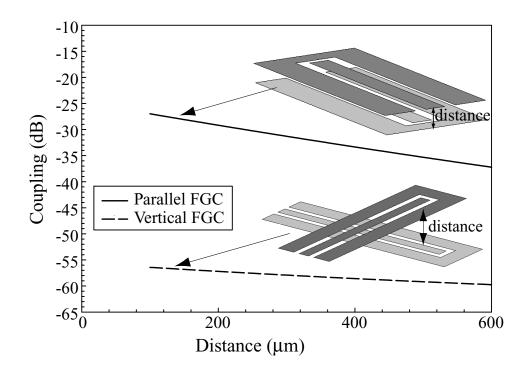

|      | lines showing coupling versus center-to-center spacing                            | 28 |

| 2.8  | Numerical results for vertically separated parallel and perpendicular             |    |

|      | FGC lines comparing coupling versus vertical separation at 8 GHz.                 | 29 |

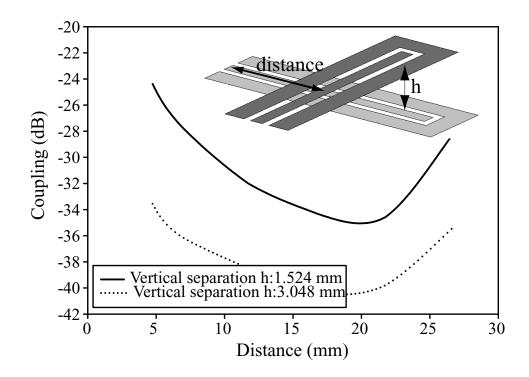

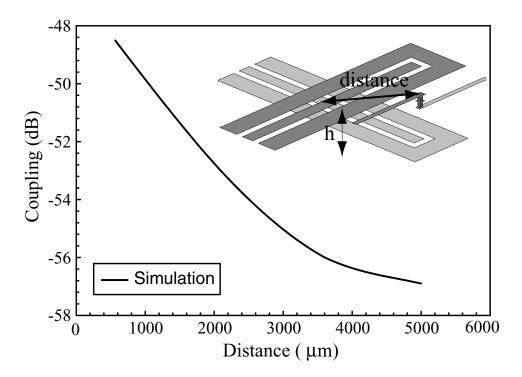

| 2.9  | Numerical results for vertically separated perpendicular FGC lines                |    |

|      | showing coupling versus distance at 8 GHz                                         | 30 |

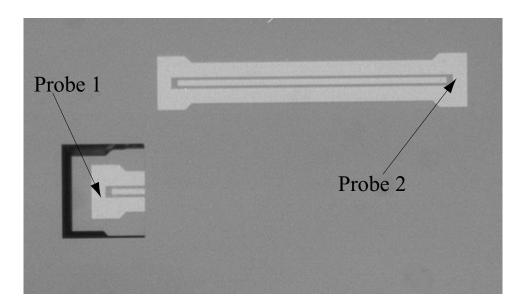

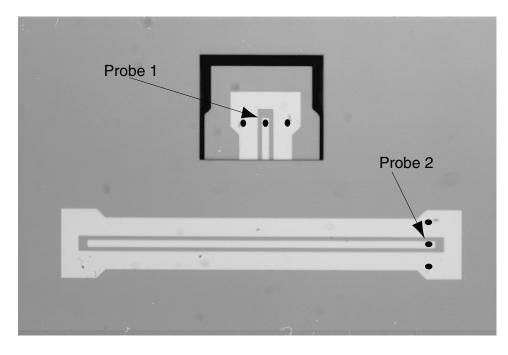

|      | W-band perpendicular FGC lines printed on two 100 $\mu$ m silicon wafers.         | 31 |

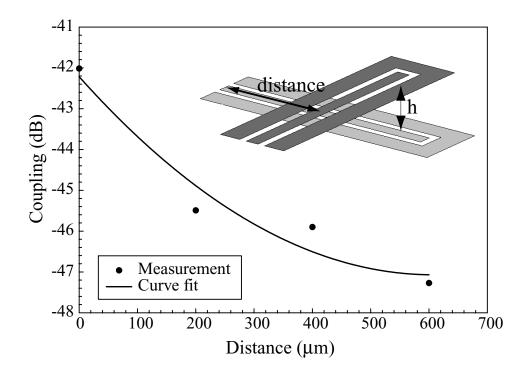

| 2.11 | W-band measured results for vertically separated FGC lines showing                |    |

|      | coupling versus distance                                                          | 31 |

| 2.12 | X-band numerical results for vertically separated FGC lines adjacent              |    |

|      | to via showing coupling versus via to cross-section distance                      | 34 |

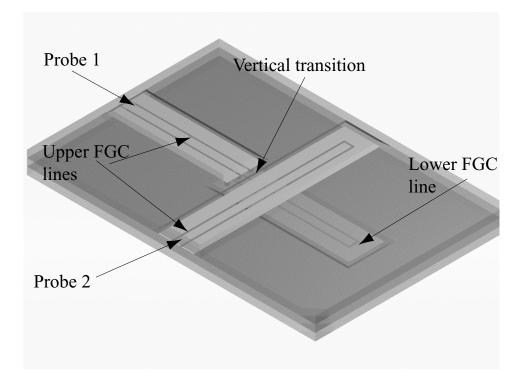

|      | Schematic for X-band FGC to FGC vertical transition.                              | 35 |

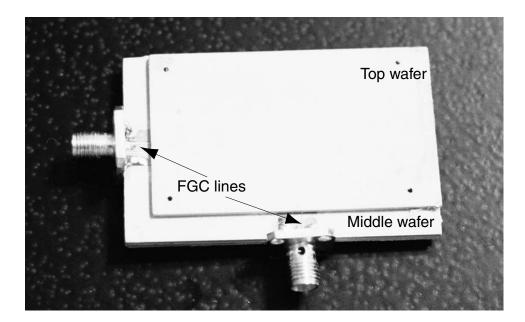

|      | X-band vertical transition.                                                       | 35 |

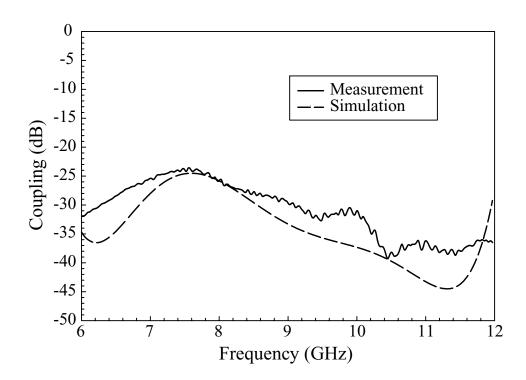

| 2.15 | X-band measured and numerical results for vertically separated FGC                |    |

|      | lines incorporating via transition.                                               | 36 |

|      | Schematics for X-band vertical transitions                                        | 36 |

| 2.17 | Numerical results for vertically separated FGC and microstrip lines               |    |

|      | incorporating via transition showing coupling versus distance at 8 GHz.           | 37 |

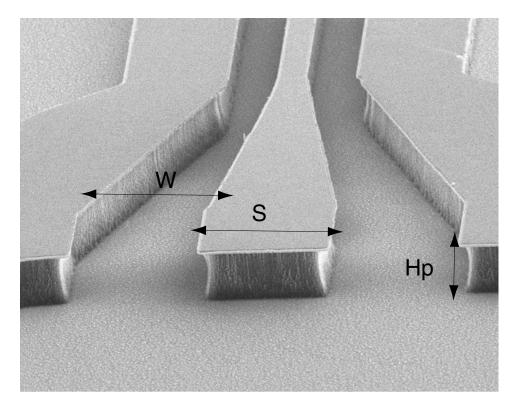

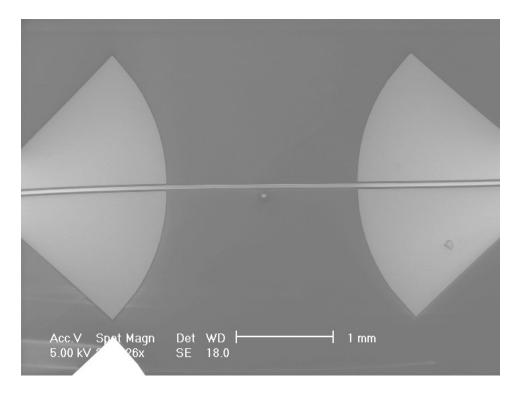

| 3.1  | Scanning electron image of micromachined CPW on low-resistivity Si                            | 43 |

|------|-----------------------------------------------------------------------------------------------|----|

| 3.2  | wafer with an etched polyimide interface                                                      | 40 |

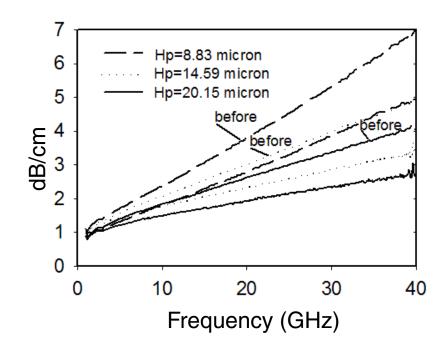

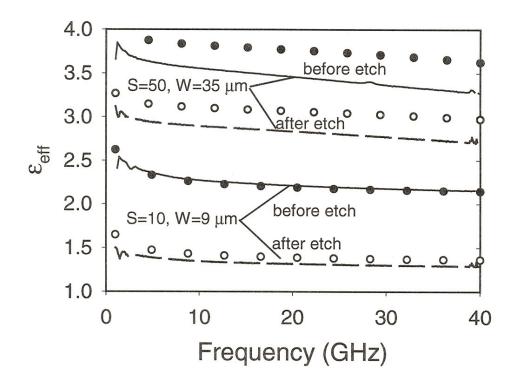

| 3.2  | Measured attenuation of CPW lines (S=10, W=9 $\mu$ m) before and after etching the polyimide. | 44 |

| 3.3  | Measured and calculated effective permittivity of micromachined CPW                           | 44 |

| ე.ე  | lines with Hp=20.15 $\mu$ m                                                                   | 45 |

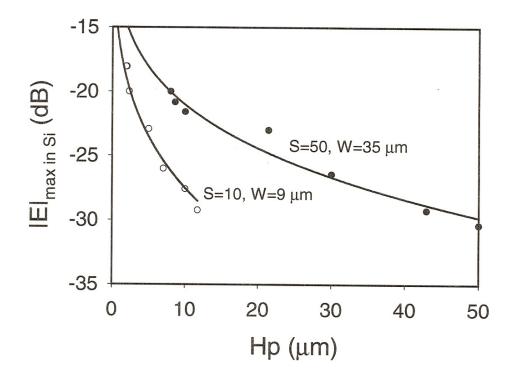

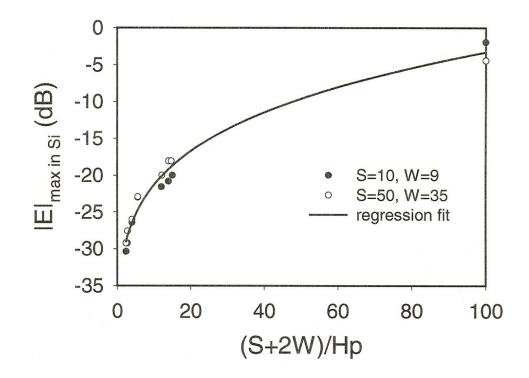

| 3.4  | Maximum electric field in Si after polyimide etching.                                         | 46 |

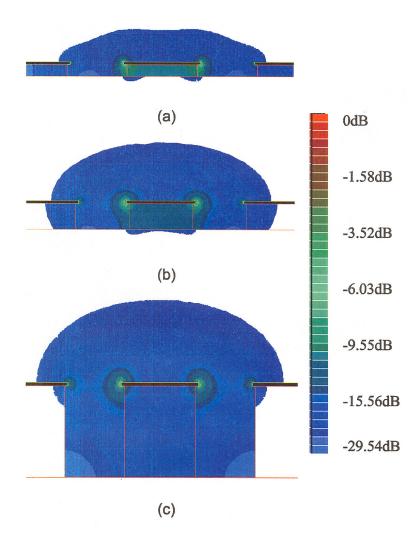

| 3.5  | Calculated electric field magnitude for CPW lines with S=50 $\mu$ m,                          | 40 |

| 0.0  | W=35 $\mu$ m, and (a) Hp=8 $\mu$ m, (b) Hp=20 $\mu$ m, and (c) Hp=50 $\mu$ m.                 | 47 |

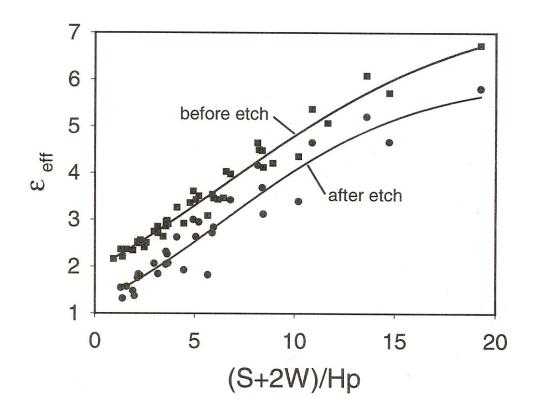

| 3.6  | Measured effective permittivity before and after polyimide etching as                         | ТI |

| 0.0  | a function of $(S+2W)/Hp$ (frequency=20 GHz).                                                 | 48 |

| 3.7  | Maximum electric field in the Si after polyimide etching as a function                        | 10 |

| 0.1  | of $(S+2W)/Hp$ .                                                                              | 49 |

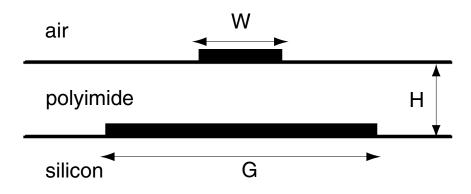

| 3.8  | Schematic of Thin Film Microstrip Lines (TFMS)                                                | 50 |

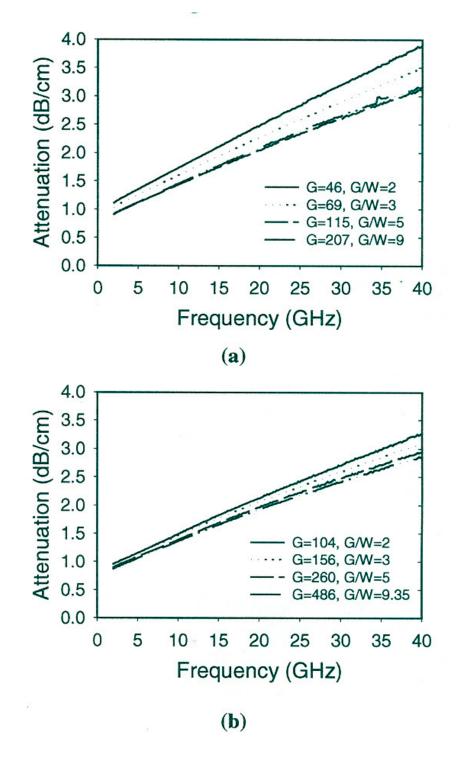

| 3.9  | Measured attenuation of TFMS lines as a function of frequency with                            |    |

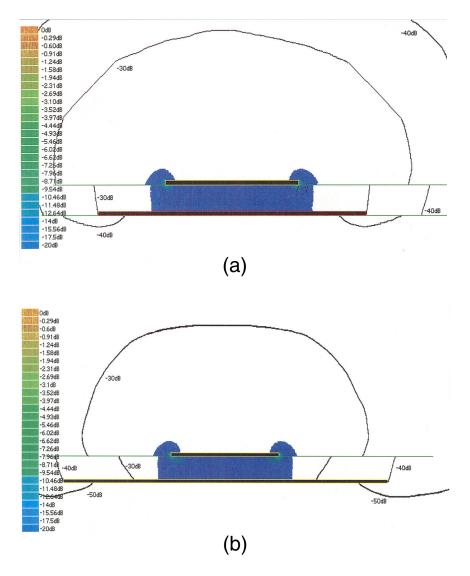

|      | (a) W=23 $\mu$ m and (b) W=52 $\mu$ m                                                         | 51 |

| 3.10 |                                                                                               |    |

|      | (b) G/W=3                                                                                     | 52 |

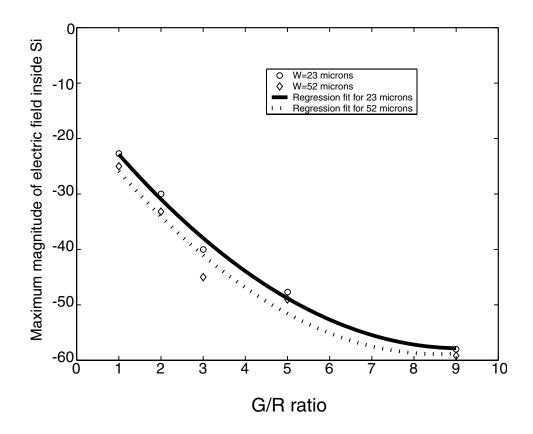

| 3.11 | Maximum electric field inside the Si wafer for $W=23\mu m$ and $W=52\mu m$ .                  | 53 |

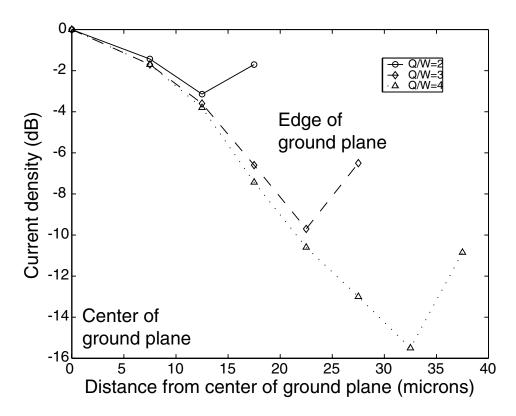

| 3.12 | Calculated current density on ground plane.                                                   | 54 |

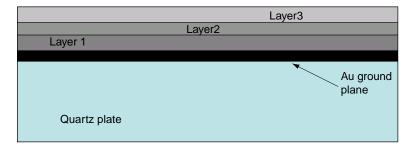

| 3.13 | Cross section of samples with optical polymers.                                               | 55 |

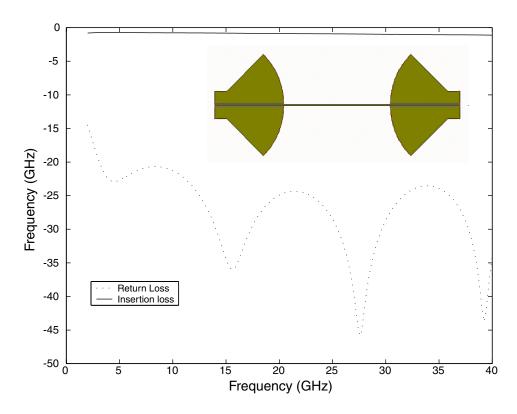

| 3.14 | Simulated response and schematic of CPW-to-microstrip transition.                             | 56 |

| 3.15 | Scanning electron image of fabricated TFMS line                                               | 57 |

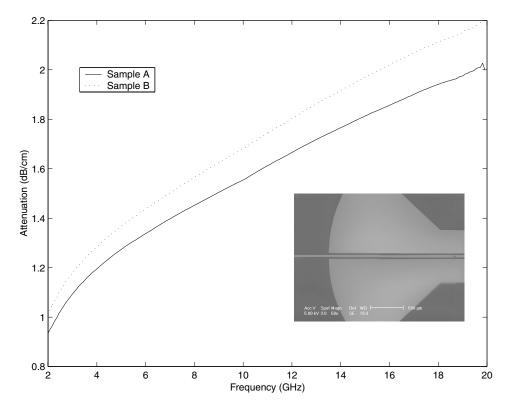

| 3.16 | Measured attenuation of TFMS lines                                                            | 58 |

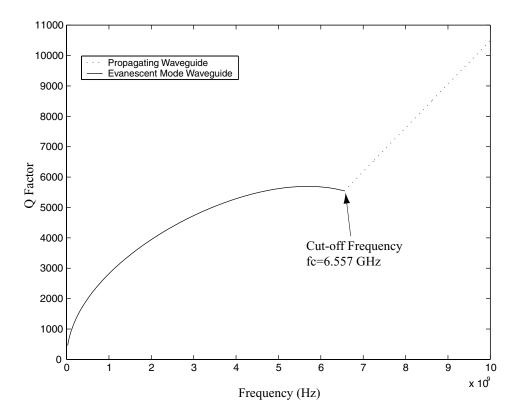

| 4.1  | Quality factor of the $TE_{10}$ mode in a WR90 waveguide                                      | 63 |

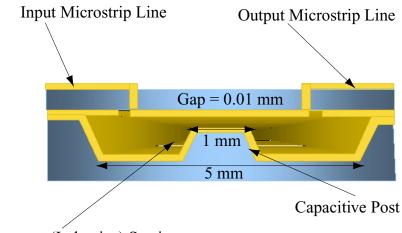

| 4.2  | Schematic of evanescent mode resonator                                                        | 65 |

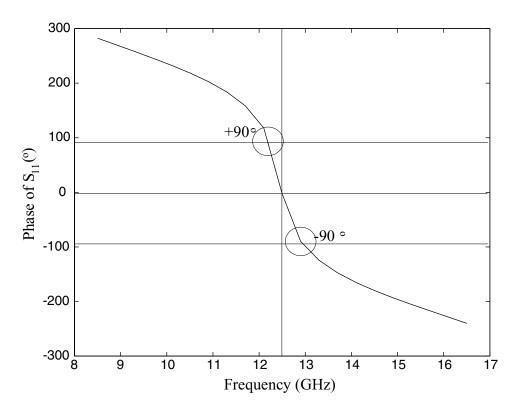

| 4.3  | Simulated phase of insertion loss for extraction of the external quality                      |    |

|      | factor                                                                                        | 66 |

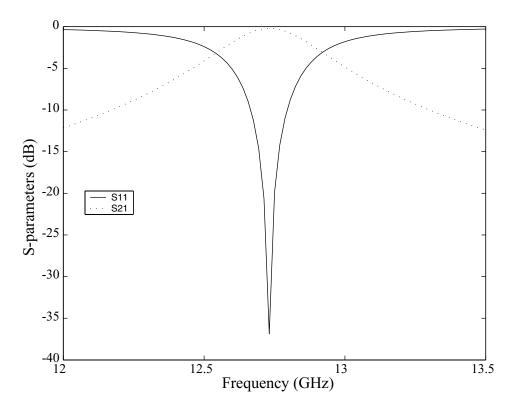

| 4.4  | Simulated response of one-pole evanescent mode resonator                                      | 68 |

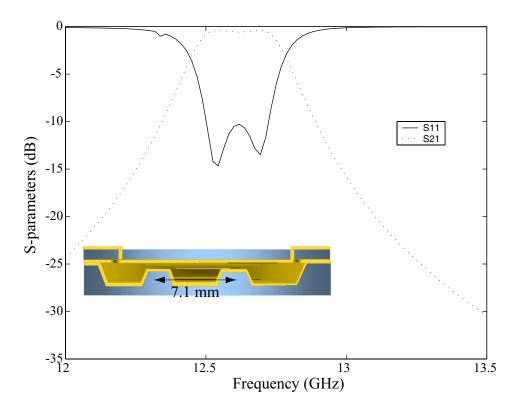

| 4.5  | Simulated response and schematic of two-pole evanescent mode filter.                          | 69 |

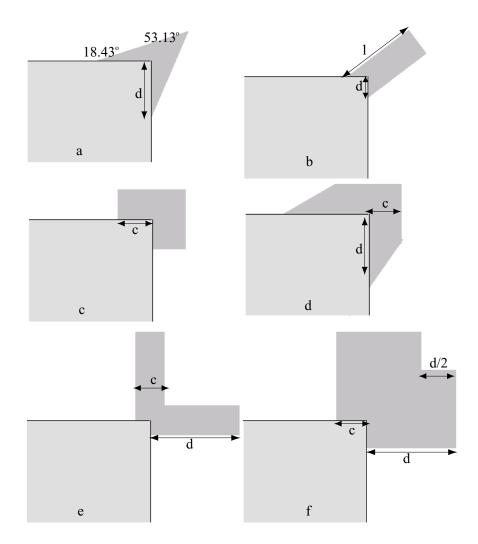

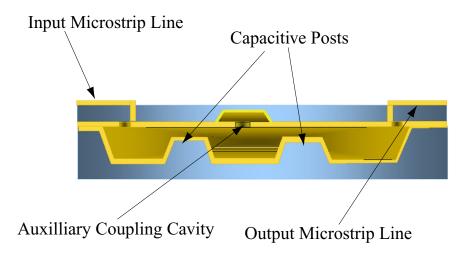

| 4.6  | Compensating structures for convex corners                                                    | 74 |

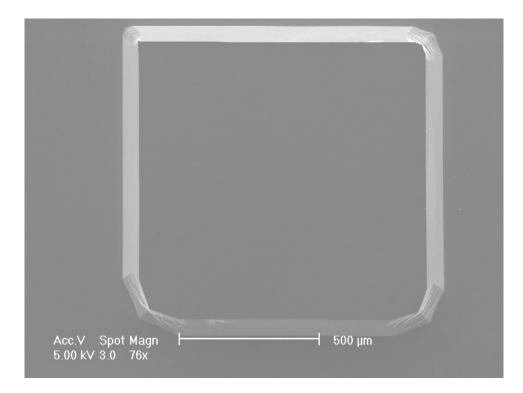

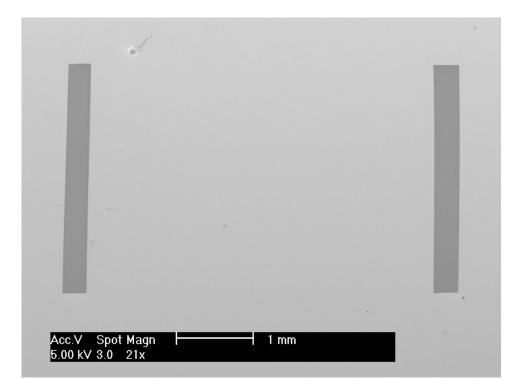

| 4.7  | Scanning electron image of etched rectangular post                                            | 75 |

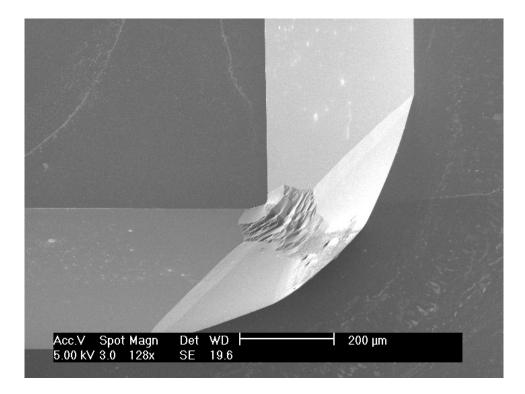

| 4.8  | Scanning electron image of etched angle at 450 $\mu$ m                                        | 76 |

| 4.9  | Scanning electron image of front side of the wafer. The cpw-to-microstrip                     |    |

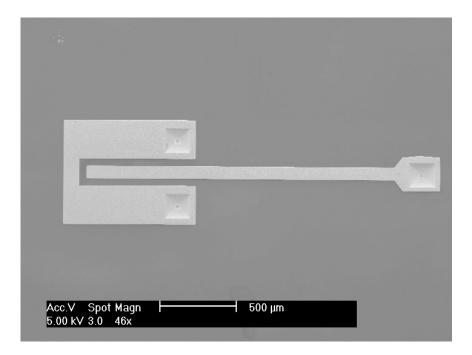

|      | transition is presented along with the shorting via                                           | 77 |

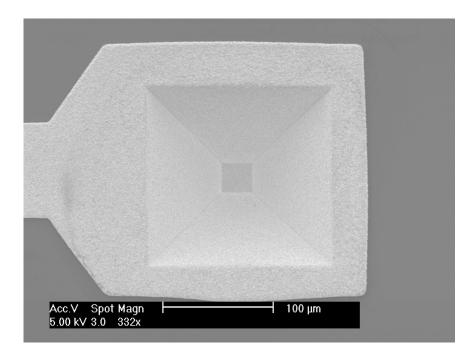

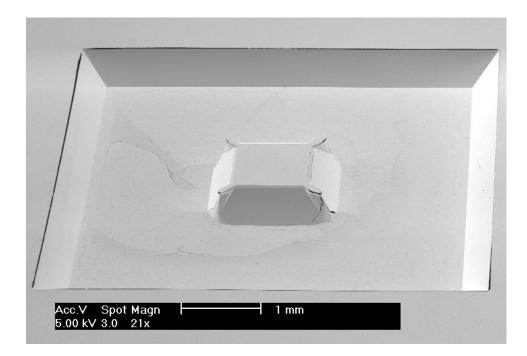

| 4.10 | Scanning electron image of via transition that connects the microstrip                        |    |

|      | line to the ground plane, thus coupling the RF signal to the filter                           | 78 |

| 4.11 | Scanning electron image of back side of the wafer. The two coupling                           |    |

|      | slots are presented.                                                                          | 79 |

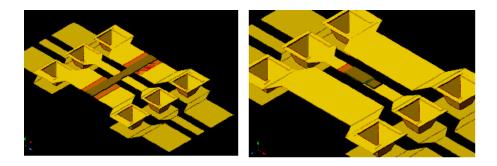

|      | Scanning electron image of the cavity wafer                                                   | 80 |

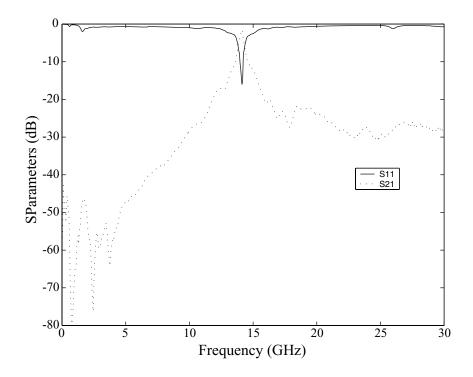

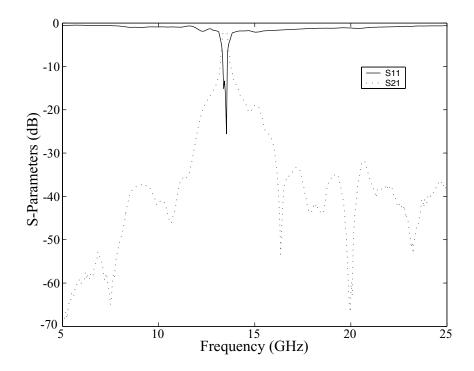

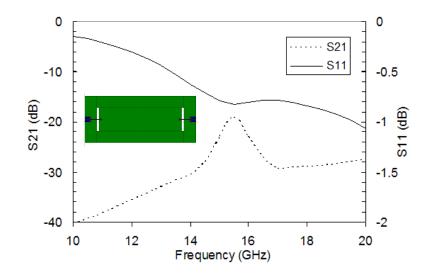

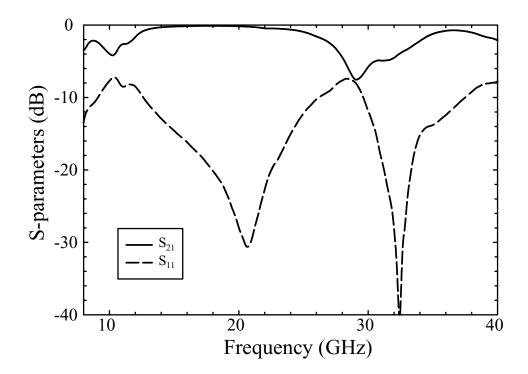

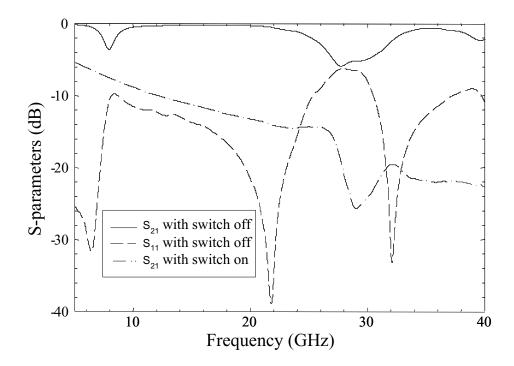

|      | Measured response of evanescent mode resonator                                                | 81 |

| 4.14 | Measured response of evanescent mode two-pole filter                                          | 82 |

| 4.15         | Simulated results of top wafer, including cpw-microstrip and microstrip-<br>slot line transition.                                                                                               | 83  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

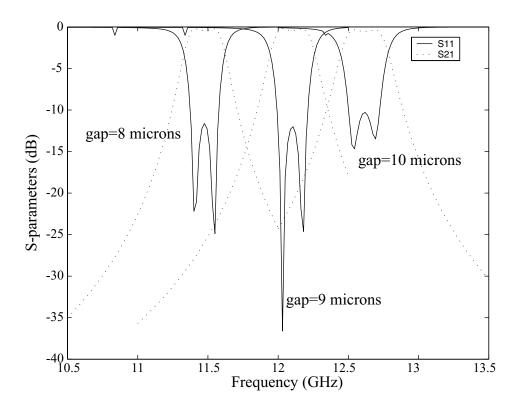

| 4 16         | Simulated response of tunable evanescent mode filter                                                                                                                                            | 83  |

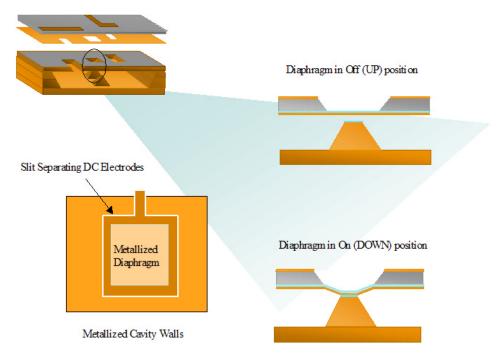

|              | Schematic of the proposed tuning mechanism.                                                                                                                                                     | 84  |

|              | Schematic of the proposed tuning mechanism.                                                                                                                                                     | 84  |

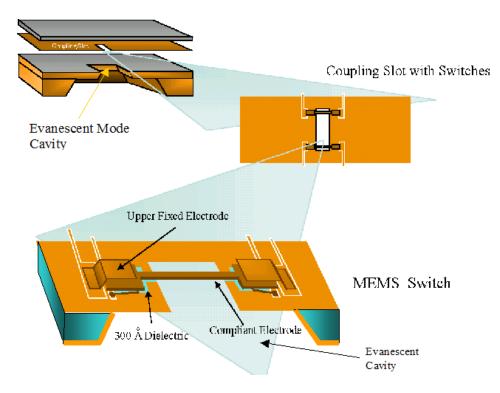

| 4.19         | Tuning an evanescent mode filter via an auxiliary cavity.                                                                                                                                       | 85  |

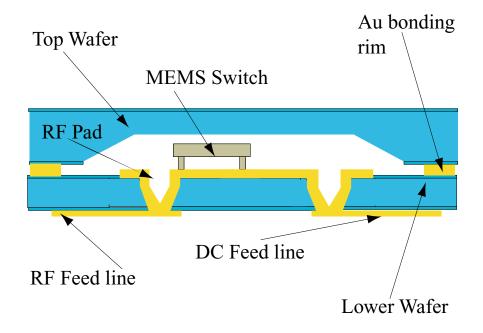

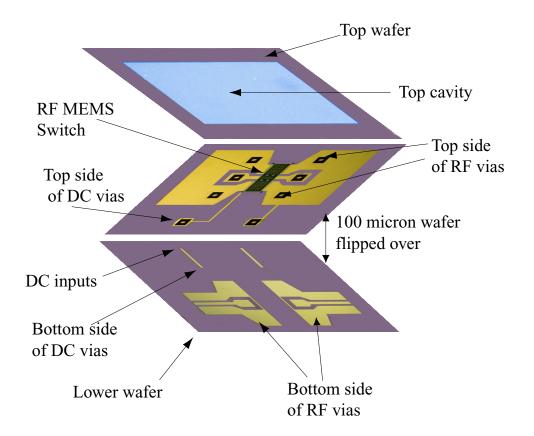

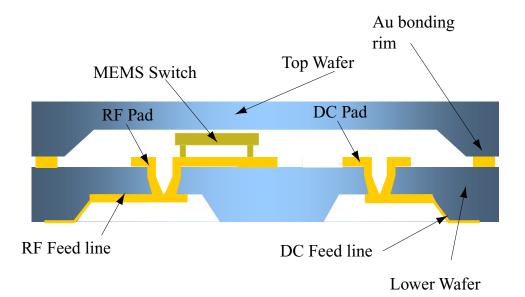

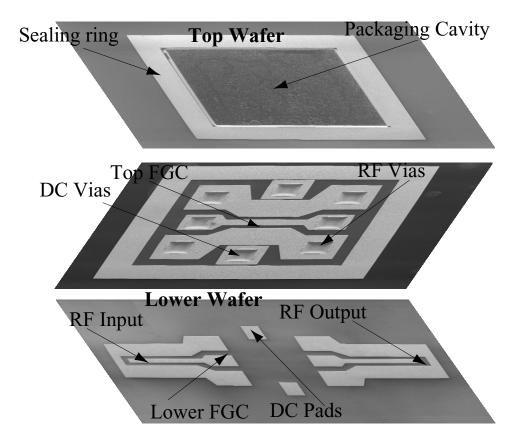

| 5.1          | Schematic of packaged RF switch with DC and RF via transitions                                                                                                                                  | 92  |

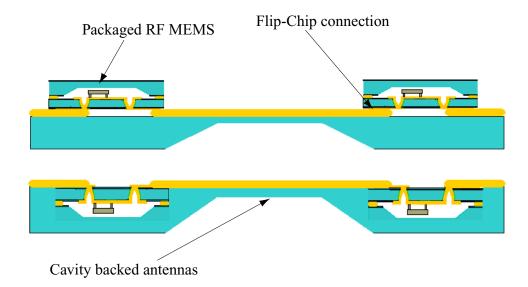

| $5.1 \\ 5.2$ | Schematic of a tunable patch array using packaged RF MEMS                                                                                                                                       | 93  |

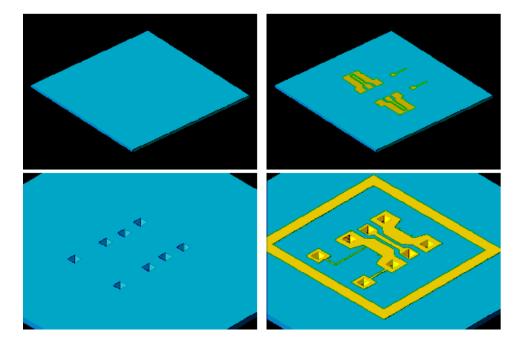

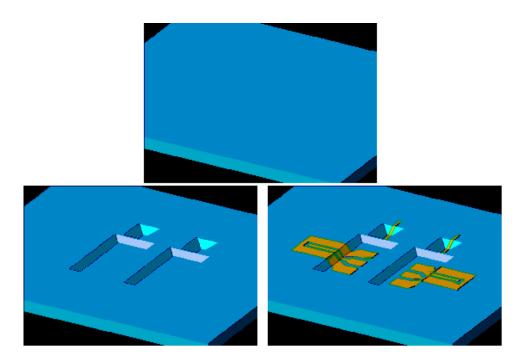

| 5.2          | Fabrication process of lower silicon wafer.                                                                                                                                                     | 95  |

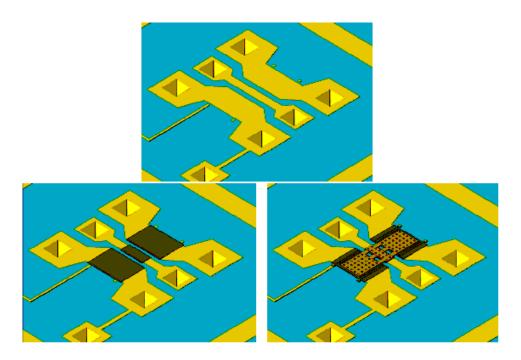

| 5.4          | Fabrication process of RF MEMS.                                                                                                                                                                 | 96  |

| 5.5          | Photograph of fabricated transition, MEMS switch and packaging cavity.                                                                                                                          | 98  |

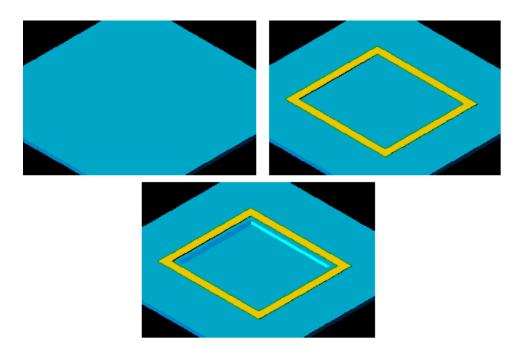

| 5.6          | Fabrication process of top silicon wafer.                                                                                                                                                       | 99  |

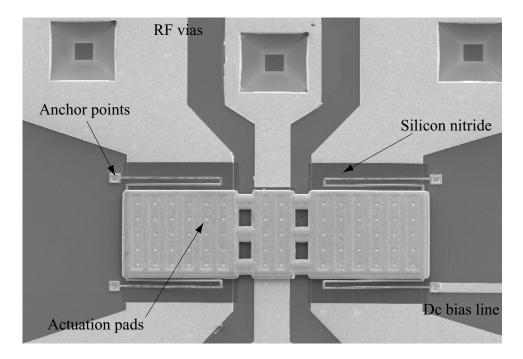

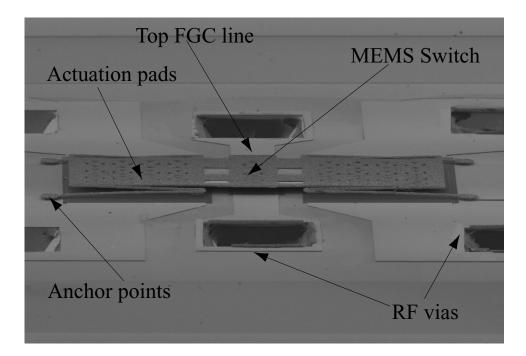

| 5.7          | Scanning electron image of RF MEMS suspended over via-hole transition.                                                                                                                          | 100 |

| 5.8          |                                                                                                                                                                                                 | 101 |

| 5.9          |                                                                                                                                                                                                 | 102 |

| 5.10         |                                                                                                                                                                                                 | 103 |

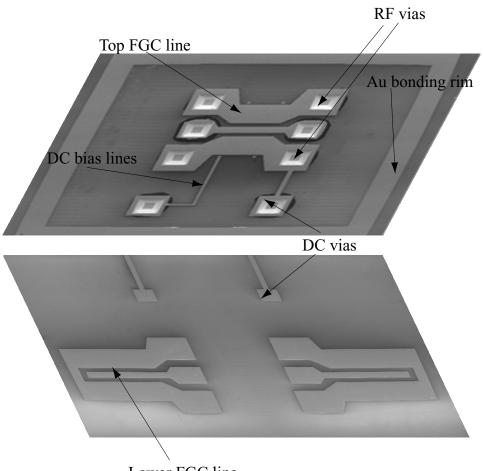

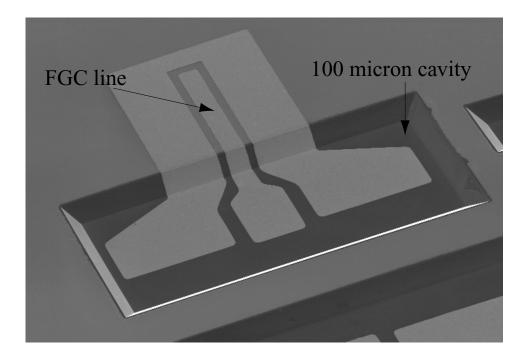

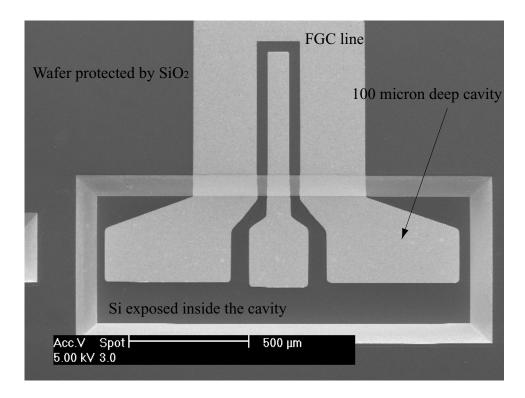

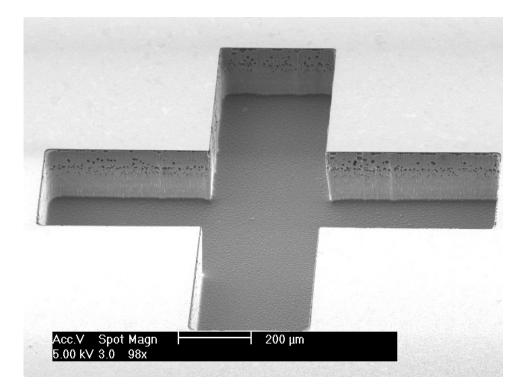

| 5.11         | Scanning Electron Micrograph of RF transition through 100 $\mu$ m Si wafer.                                                                                                                     | 104 |

| 5.12         | Measured response of improved RF back-to-back transition                                                                                                                                        | 105 |

| 5.13         | Scanning electron image of RF MEMS switch suspended over the RF                                                                                                                                 |     |

|              | transition                                                                                                                                                                                      | 106 |

|              | 1                                                                                                                                                                                               | 107 |

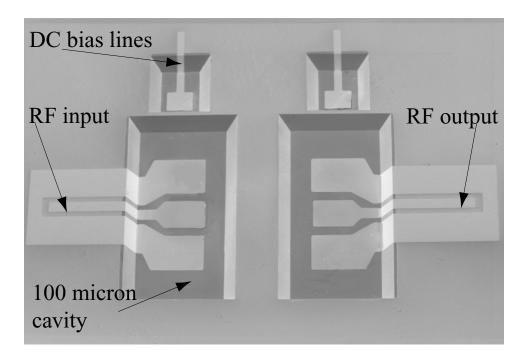

| 5.15         | Schematic of packaged RF MEMS switch with DC and RF via transi-                                                                                                                                 |     |

|              | tions along with multilevel FGC transitions.                                                                                                                                                    | 108 |

|              |                                                                                                                                                                                                 | 109 |

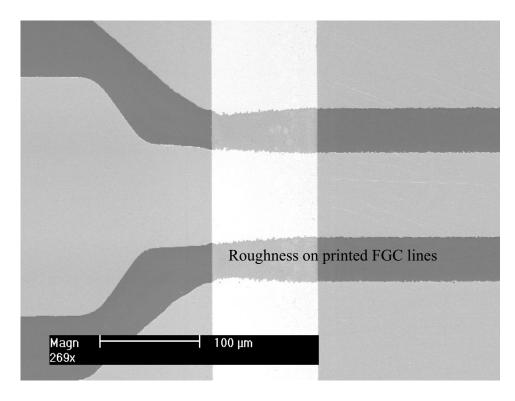

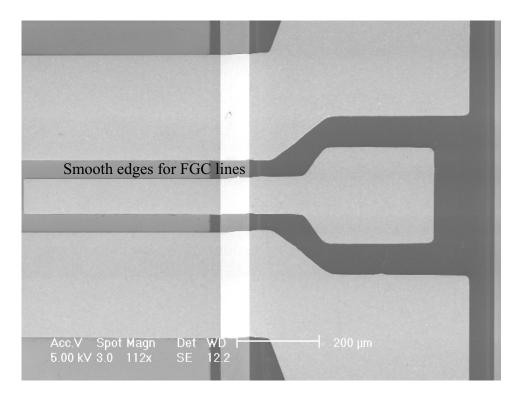

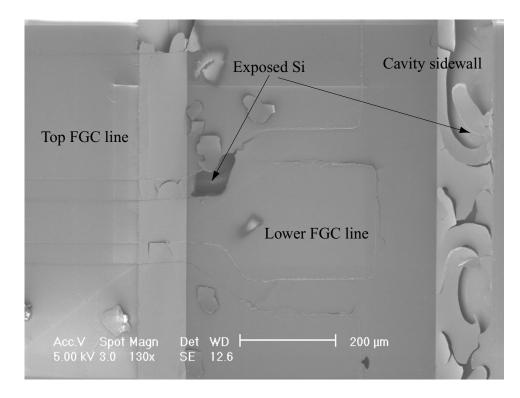

| 5.17         | Fabricated FGC lines after vacuum drying and metal deposition                                                                                                                                   | 110 |

|              | Ĩ                                                                                                                                                                                               | 111 |

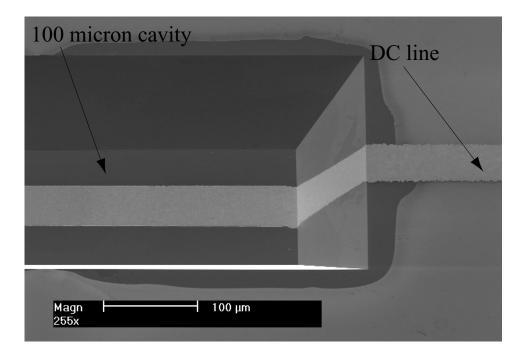

| 5.19         | Scanning electron image of DC bias line transitioning inside a 100 $\mu {\rm m}$                                                                                                                |     |

|              | 1 5                                                                                                                                                                                             | 112 |

| 5.20         | Scanning electron image of a finite ground coplanar waveguide transi-                                                                                                                           |     |

| <b>F</b> 0.1 |                                                                                                                                                                                                 | 113 |

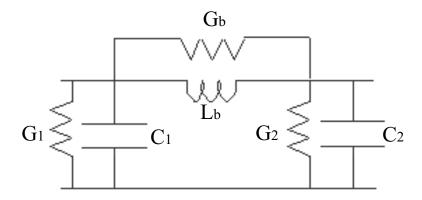

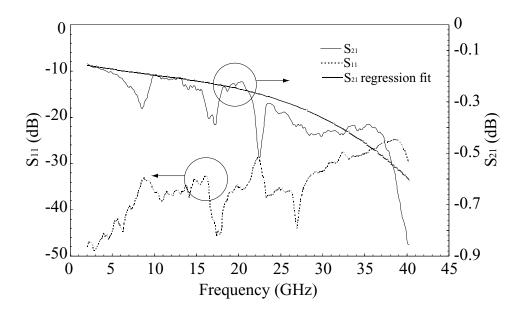

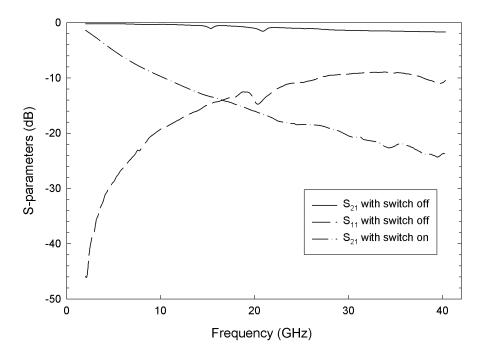

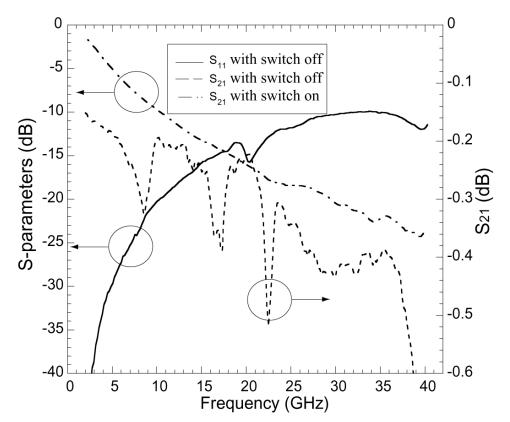

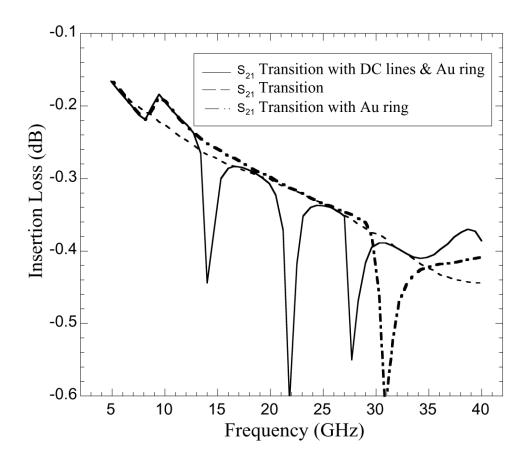

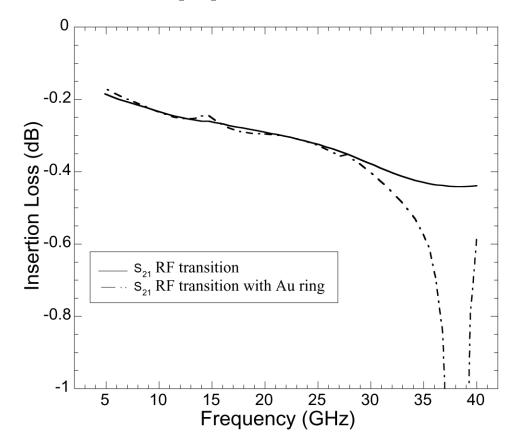

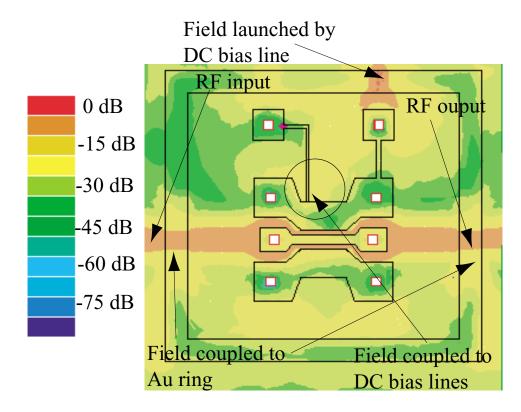

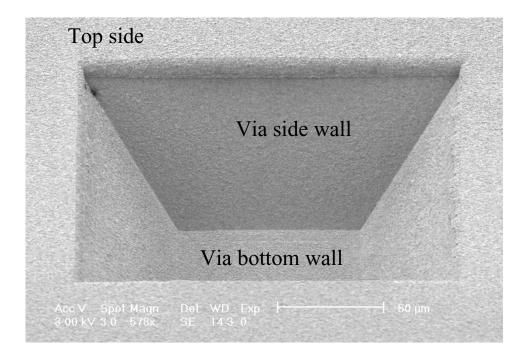

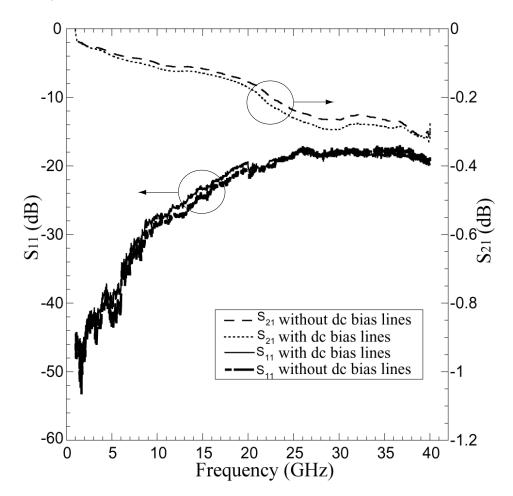

|              |                                                                                                                                                                                                 | 114 |

| 5.22         | Scanning electron image demonstrating the failed attempt to passivate                                                                                                                           | 115 |

| F 00         | 8                                                                                                                                                                                               | 115 |

|              | 0                                                                                                                                                                                               | 116 |

|              | 1                                                                                                                                                                                               | 116 |

| 6.1          |                                                                                                                                                                                                 | 123 |

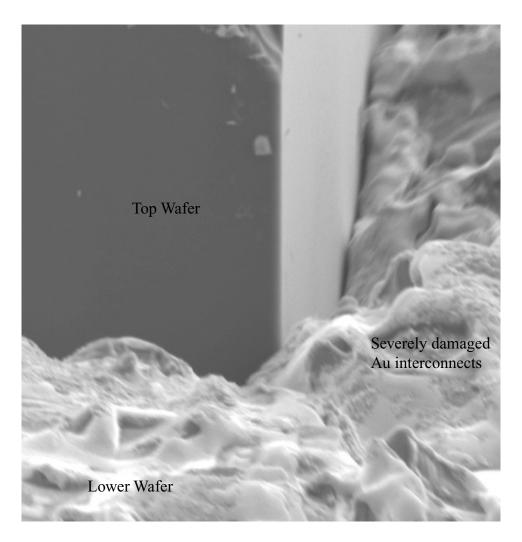

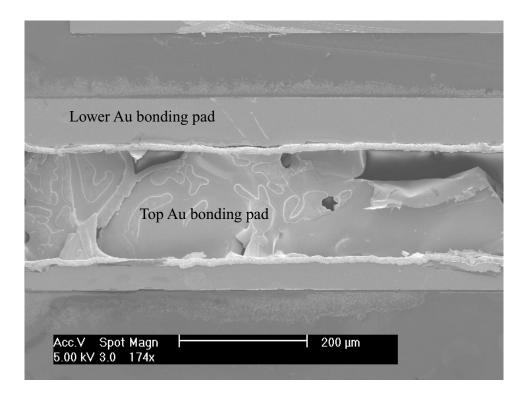

| 6.2          | Scanning electron image of successful thermocompression bond at 380°C.<br>The top wafer is pulled and the Au remained attached to the lower Au<br>layer demonstrating the strength of the bond. | 124 |

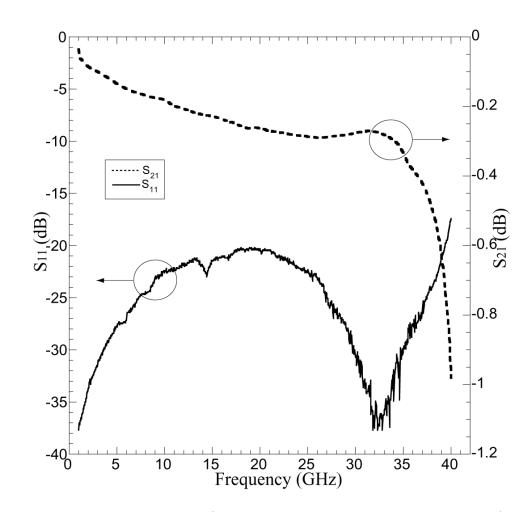

| 6.3          | Measured response of packaged RF back-to-back transition and MEMS                                                                                                                               |     |

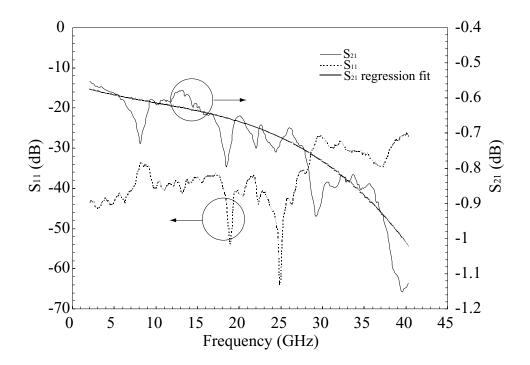

|              |                                                                                                                                                                                                 | 130 |

| 6.4  | Simulated results for RF back-to-back transition.                       | 131  |

|------|-------------------------------------------------------------------------|------|

| 6.5  | Simulated results for improved RF back-to-back transition               | 132  |

| 6.6  | Magnitude of the electric field underneath the Au bonding ring and      |      |

|      | the top FGC line.                                                       | 134  |

| 6.7  | Scanning electron image of electroplated via-hole.                      | 136  |

| 6.8  | Scanning electron image of improved RF transition.                      | 137  |

| 6.9  | Scanning electron image of DRIE etched alignment mark                   | 138  |

| 6.10 | Measured response of RF back-to-back transition with and without DC     |      |

|      | bias lines and vias.                                                    | 139  |

| 6.11 | Measured response of RF back-to-back transition including the Au        |      |

|      | bonding ring.                                                           | 140  |

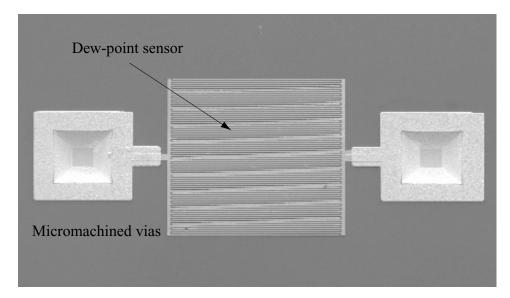

| 6.12 | Fabricated dew-point sensor for hermeticity testing                     | 142  |

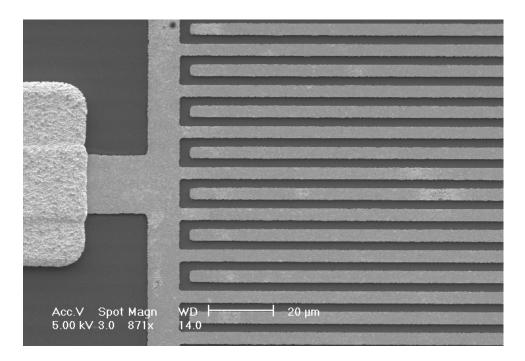

| 6.13 | Detail of the fabricated dew-point sensor                               | 143  |

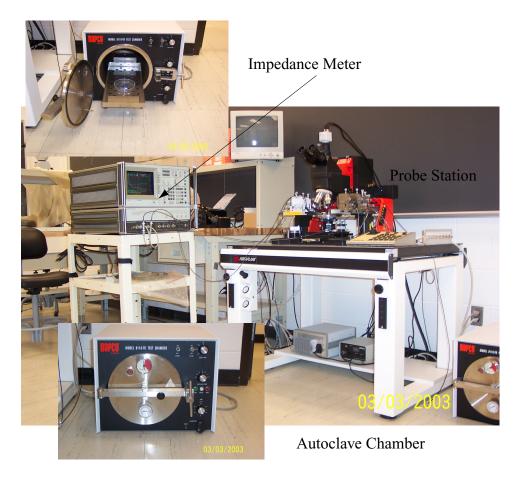

| 6.14 | Measurement set up for accelerated tests                                | 144  |

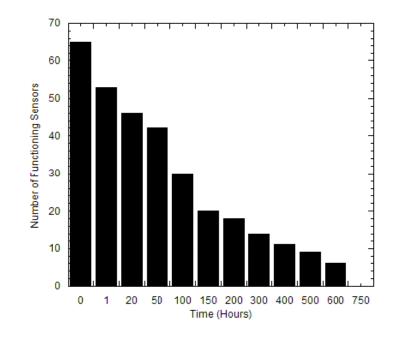

| 6.15 | Operating dew-point sensors with respect to time                        | 145  |

| 6.16 | Typical response of dew-point sensor versus time inside the autoclave   |      |

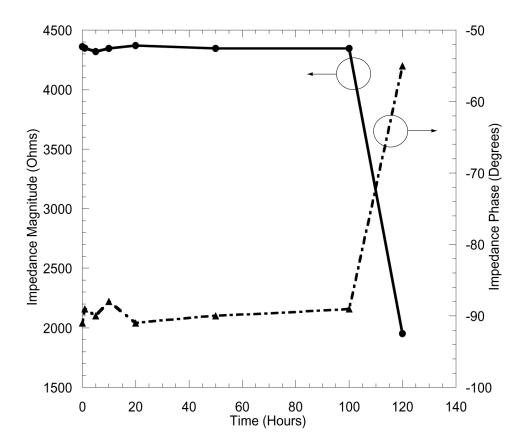

|      | chamber                                                                 | 146  |

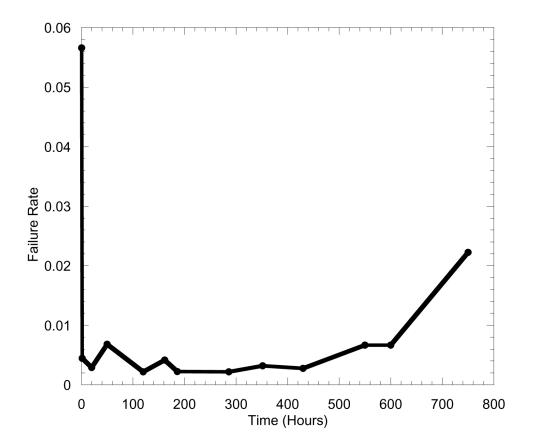

| 6.17 | Failure rate for vacuum sealed sensors                                  | 147  |

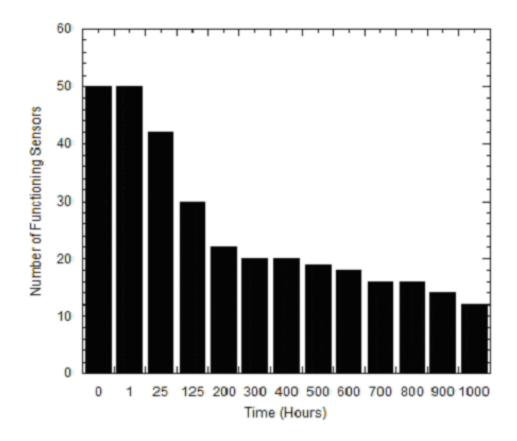

| 6.18 | Operating dew-point sensors with respect to time                        | 148  |

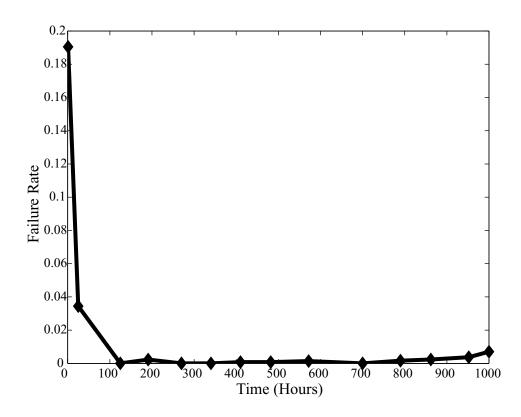

| 6.19 | Failure rate for sensors packaged in dry air                            | 149  |

| 7.1  | Schematic of the proposed MEMS based structures for reliability testing | .155 |

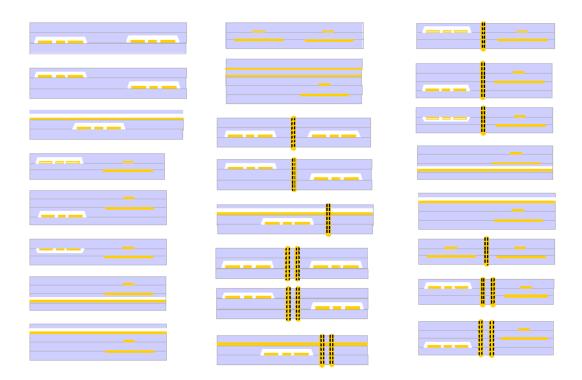

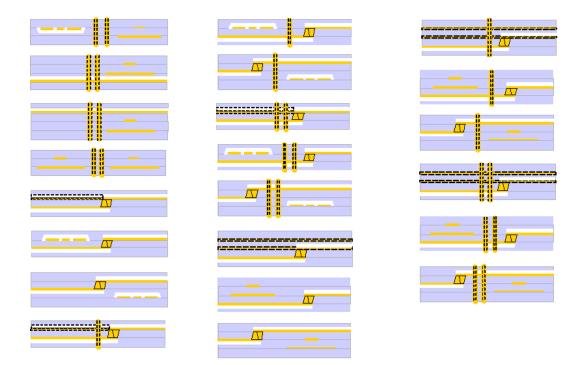

| A.1  | Structures analyzed for isolation at 8 and 32 GHz                       | 158  |

| A.2  | Structures analyzed for isolation at 8 and 32 GHz                       | 159  |

# LIST OF APPENDICES

## Appendix

| А | Isolation Study       | 158 |

|---|-----------------------|-----|

| В | Fabrication Processes | 160 |

# CHAPTER 1

# Introduction

### 1.1 Motivation

**E** MERGING needs in military and civilian high frequency applications have prompted researchers to investigate silicon micromachining as a novel and innovative way to achieve higher levels of three-dimensional integration, optimum RF performance, low-size and weight. Defense and national security have usually been the driving forces behind recent advantages in communication, radar and sensing systems. However, future solutions for military applications must address two new challenges: (a) offer compatibility to commercially available technologies as a cost saving measure and (b) offer increased flexibility to accommodate the rapid changes imposed by technology market forces. Silicon micromachining introduces a variety of technologies such as Microelectromechanical (MEMS) systems, on-wafer packaging, three-dimensional interconnects, cavity resonators and filters. The integration of all these enabling technologies can lead to miniature multi-functional systems that will include antennas, tuning mechanisms, filters, passive interconnects, and active components on a single chip. Such highly compact systems-on-a-chip can have an abundance of applications both for the military and the civilian market.

## **1.2** Silicon Micromachining

#### **1.2.1** Physics of Silicon Semiconductors

From the early days of IC industry, silicon has been the substrate of choice. Its thermal and mechanical properties, along with its excellent electrical performance make Si the most appealing candidate for creating integrated circuitry. The maturity of surface and bulk silicon micromachining techniques gave silicon an additional advantage over other substrate materials. Understanding the physics behind silicon micromachining is necessary in order to correctly and fully utilize the superiority of this set of fabrication techniques.

Crystalline silicon forms a covalently bonded structure, the diamond-cubic structure, which has the same atomic arrangement as carbon in diamond form and belongs to the more general zinc-blend classification [1]. The lattice constant for Si is 5.4309 Å and its diamond-cubic lattice is surprisingly wide, with a packing density of 34% compared to 74% of the regular face-centered cubic lattice (fcc). The {111} planes present the highest packing density and the atoms are oriented in such a way that three bonds are below the plane. This explains why the {111} planes are virtually untouched by wet anisotropic etchants.

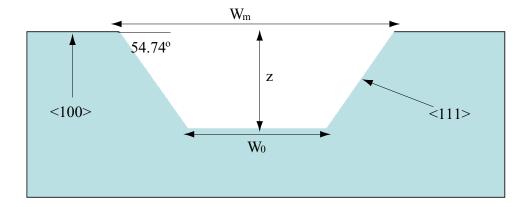

Silicon micromachining, the ability to fabricate microstructures on the surface or the interior of Si wafers is mainly based on <100> oriented wafers. It is well understood [2] that the intersections of the non-etching {111} planes with the {100} planes (e.g. the wafer surface) are mutually perpendicular and lying along the <110> orientations. Provided a mask opening is accurately aligned with the <100> orientation, which is set by the primary flat of the silicon wafer, only {111} planes will be introduced as sidewalls from the very beginning of the etch. Therefore during etching, truncated pyramids (via-holes) can become deeper, but never wider. After prolonged etching the {111} family of planes is exposed down to their common intersection and the (100) bottom plane disappears creating a pyramidal pit. The slope of these sidewalls (Fig.1.1) is determined by the angle between the (111) sidewall and the (110) plane and is equal to 54.74°. As a result of that the width of a rectangular or square cavity bottom plane,  $W_0$ , is completely defined by the etch depth, z, and the mask opening,  $W_m$ .

$$W_0 = W_m - 2\cot(54.74^o)z \tag{1.1}$$

or

$$W_0 = W_m - \sqrt{2}z \tag{1.2}$$

Vertical walls can also be etched in (100) oriented silicon wafers. If the mask opening is aligned to the  $\langle 100 \rangle$  orientations (45° angle with the wafer primary flat) the {100} planes are introduced as sidewalls. Since both the bottom and the sidewalls are from the same {100} group, lateral undercutting equals the vertical etch rate and therefore rectangular channels are created.

Other materials such as glass or ceramics, can be used as substrates at a much lower cost. However, non of these offer the capability to precisely fabricate extremely small features. For many years silicon has been the substrate of choice for the IC industry. The maturity of micromachining techniques, added to silicon's mechanical stability and good thermal properties, can provide a very appealing and profitable combination.

#### **1.2.2** Wet Anisotropic Etching

Wet anisotropic etching is a low-cost, and very accurate method for bulk micromachining of silicon wafers. The etching has three major steps: (a) reactant transport to the surface; (b) surface reaction; and (c) reaction product transport away from the surface. If the rate determining factors are (a) and (c) etching is diffusion limited and

Figure 1.1: Anisotropically etched features in (100) oriented silicon wafers.

may be increased by stirring. If, on the other hand, (b) is the rate determining step, etching is reaction rate limited and depends strongly on temperature, etching material and solution composition [3]. Anisotropic etching, when performed properly, results in geometric shapes bounded by perfectly defined crystallographic planes. Additionally, contrary to isotropic wet etching, it offers excellent lateral dimension control. Unfortunately it is a relatively slow and high temperature process, and therefore appropriate masking techniques are necessary to protect the wafer. A wide variety of etchants have been used for anisotropic etching of silicon, including alkaline aqueous solutions of KOH, NaOH, TMAH, LiOH, CsOH,  $NH_4OH$  and quaternary amonium hydroxides, with the possible addition of alcohol. Alkaline organics such as ethylenediamine, choline or hydrazine with additives such as pyrocathecol and pyrazine are employed as well [4]. From the above the more commonly used anisotropic etchants are KOH and TMAH. Their etch rate is reaction rate controlled and therefore temperature dependent. These chemicals have differences in the etch rate of  $SiO_2$  and the surface roughness that they create, thus, depending on the application, the appropriate solution is selected.

As will be analyzed in Chapter 4, where the issue of wet etching will be revisited, there are a lot of conflicting data in the literature on the anisotropic etch rates of the various silicon crystal planes, especially the higher index ones. This is not too surprising, given the multiple parameters influencing individual results: temperature, stirring, size of etching features, solution concentration, addition of alcohol and other organic materials, surface defects etc. More rigorous experimentation and standardization will be necessary in order to better understand the influence of all these parameters to the etch rates. Nevertheless, several models attempting to explain the anisotropy in the etch rates of the different Si planes have been proposed [5, 6, 7, 8, 9].

#### **1.2.3** Deep Reactive Ion Etching

Wet anisotropic etching is limited by the orientation of the silicon crystal planes. Fabricating smaller features with higher aspect ratios requires a more selective etching technique such as the Deep Reactive Ion Etching (DRIE). The dry anisotropic etching in this work is performed with the use of a Surface Technology Systems (STS) reactive ion etcher. For this system the etch process consists of a repeated cycling between successive etching and passivation steps, using two different gases ( $C_4F_8$  for passivation and  $SF_6$  for etching) and appropriate bias voltage in order to generate plasma. The geometric restrictions imposed by anisotropic wet etching are lifted in the case of DRIE. The sidewall profile departs from the normal by approximately  $5^{\circ}$ , but it can be controlled to a great extend by judicious choice of such parameters as etching time, passivation time and RF power. The biggest drawback of DRIE however, is the roughness of the resulting sidewalls. Due to the time-multiplexed gasfeeding process, a horizontal scalloping of the sidewall occurs. This scalloping also varies with the material that is used for masking (hard mask or oxide), therefore an extensive characterization of the process is necessary in order to fully understand the influence that all these parameters have both on the etch profile and the roughness of the sidewalls.

#### Table 1.1: Packages for RF MEMS

| Frequency band    | DC-50 GHz for metal-to-metal,10GHz-W band for Capacitive    |  |  |

|-------------------|-------------------------------------------------------------|--|--|

| Insertion loss    | <0.1 dB                                                     |  |  |

| Return loss       | <-10 dB                                                     |  |  |

| Bonding Procedure | Low Temperature, Reduced outgassing                         |  |  |

| Sealing           | Hermetic or near hermetic                                   |  |  |

| Ambient           | Nitrogen or non-reactive gasses                             |  |  |

| Materials         | Thin film metals, $SiO_2$ , Silicon nitride, no polysilicon |  |  |

# 1.3 Packaging for RF MEMS Switches

In the last decade the maturity of surface and bulk micromachining enabled the development of Microelectromechanical systems (MEMS). In the RF area MEMS are mainly used as switches that utilize mechanical movement to achieve a short or an open circuit in a RF transmission line. While excellent performance has been reported for these devices, their operation is very sensitive to environmental factors, such as humidity and small particles. Therefore their integration to real-life systems can be problematic without a low-cost, low-loss hermetic package. Such a packaging scheme should follow some basic requirements, which are summarized in Table 1.1.

One of the major advantages of RF MEMS, compared to their solid state counterparts, is their low insertion loss. In order to retain this capability the total loss introduced by the package, excluding the losses of the feeding lines, should be kept below 0.1 dB, while the return loss should be below -10 dB at the frequency band of operation. In order to keep the loss below that limit the number of necessary interconnects in order to access the device should be kept at a minimum. Moreover use of wire or ribbon bonds should be avoided due to the parasitic inductance that they add.

Regarding the bandwidth of the package two alternatives exist. One it to create a broadband design, allowing the use of one design for different types of switches (metal-

to-metal or capacitive). The second approach is to intensionally introduce resonances in the response, thus achieving excellent performance in a narrower frequency band. The RF transition to the MEMS can be done either using via-holes or by passing the lines directly under the sealing ring. The second approach, although easier to fabricate, offers lower RF and hermeticity performance. The reason is that the feeding line needs to be embedded in some type of dielectric (SiO<sub>2</sub> or BCB) in order to isolate it from the sealing ring. This changes the characteristic impedance of the interconnect and therefore appropriate matching networks need to be introduced. Furthermore, the isolation layer is deposited over the printed interconnect, which is a 2-3  $\mu$ m thick microstrip or FGC line. This means that the final structure might not be planar and step coverage could create microcracks on the layer. Clearly more research is needed for this type of RF connection to a MEMS device in order to evaluate both its RF performance and long-term hermeticity.

MEMS accelerometers and gyroscopes are been fabricated using thick polysilicon layers which can withstand very high post-processing temperatures. In contrast, RF MEMS are usually created out of thin film metal membranes (thickness:  $0.5-2 \ \mu m$ , length: 250-350  $\mu m$ ) suspended a few  $\mu m$  over the substrate. Such a released structure is extremely sensitive to both bonding temperatures and outgassing and therefore not all available sealing techniques are applicable. Currently several technologies are been proposed for packaging of RF MEMS such as epoxy seal, metal-to-metal solder bonding, silicon-glass eutectic using localized heating, gold-gold thermocompression bonding, LPCVD sealing, and surface activated bonding. Low-temperature bonding techniques need to be thoroughly investigated in order to provide a reliable method for sealing RF MEMS.

Finally, in contrast to other MEMS structures RF MEMS need to be packaged in an ambient of nitrogen or other non-reactive gas. This is due to the fact that the gas will act as a damping mechanism for the structure resulting in a low mechanical Q

| Company    | Alpha                           | HEI                             | Shinco     | Stratedge                       | MCS                 |

|------------|---------------------------------|---------------------------------|------------|---------------------------------|---------------------|

| Material   | Alumina                         | Laminate                        | Ceramic    | Alumina                         | Alumina             |

|            | Ceramic                         | Substrate                       |            | Ceramic                         |                     |

| Intercon.  | 3-via cpw,                      | 3-via cpw,                      | 3-via cpw, | 3-via cpw,                      | Bump                |

|            | wirebonds,                      | wirebonds,                      | wirebonds, | wirebonds,                      | Grid Array          |

|            | flip-chip                       | flip-chip                       | flip-chip  | flip-chip                       |                     |

| $IL(dB)^a$ | 0.6dB at                        | 1  dB at $46$                   | n/a        | 0.6  dB at                      | 1dB at              |

|            | $20  \mathrm{GHz}$              | GHz                             |            | 45 GHz $^{b}$                   | $31.5~\mathrm{GHz}$ |

| RL(dB)     | $10 \mathrm{dB} \mathrm{at} 24$ | $15 \mathrm{dB} \mathrm{at} 46$ | n/a        | $18 \mathrm{dB} \mathrm{at} 45$ | 20dB at             |

|            | GHz                             | GHz                             |            | GHz                             | $31.5~\mathrm{GHz}$ |

| Hermet.    | n/a                             | No                              | Yes        | Near                            | n/a                 |

| Ambient    | Air                             | Air                             | n/a        | Air                             | Air                 |

Table 1.2: Commercially available RF packages.

<sup>a</sup>Measurements are performed on different materials, different line lengths, and different metal thicknesses therefore are not comparable.

<sup>b</sup>Measurements for this package were performed on a single (not back-to-back) transition.

value and thus increase the reliability of the MEMS. In addition to that, a pressure equilibrium between the inside of the package and the outside environment will make it even more difficult for humidity to flow inside of the package, in the case where a leak channel is present.

Significant work has already been done in RF packages for use with solid state amplifiers, diodes or filters. Some of the available packages are summarized in Tables 1.2 and 1.3. These packages are been offered in a variety of configurations with wide bandwidth of operation and are mainly non-hermetic. Unfortunately, as was mentioned in the previous paragraphs, these packages are not applicable for RF MEMS. Some available packages for MEMS are mentioned in Table 1.4. Many more companies and laboratories are working in this area. However, in most cases, this is research currently under investigation and therefore intellectual properties and trade secrets significantly reduce the available information.

This thesis will present the first published on-wafer packaging scheme for RF MEMS switches for operation up to 40 GHz and beyond. The deembeded measured

| Company    | UMS                             | Gergia                          | Alcatel                         | FBH/EADS           | Northrop   |

|------------|---------------------------------|---------------------------------|---------------------------------|--------------------|------------|

|            |                                 | Tech                            |                                 |                    | Grumman    |

| Material   | Alumina                         | LTCC                            | HTCC                            | Si/BCB             | LTCC       |

|            | Ceramic                         |                                 |                                 |                    |            |

| Intercon.  | 3-via cpw,                      | 3-via cpw,                      | microstrip,                     | 3-via cpw,         | 3-via cpw, |

|            | wirebonds,                      | flip-chip                       | ribbon                          | wirebonds,         | flip-chip  |

|            | flip-chip                       |                                 | bonds                           | flip-chip          |            |

| $IL(dB)^a$ | 1  dB at $46$                   | 3  dB at $12$                   | 1.5 dB at                       | 0.6  dB at         | n/a        |

|            | GHz                             | GHz                             | $40 \mathrm{GHz}$               | $30  \mathrm{GHz}$ |            |

| RL(dB)     | $15 \mathrm{dB} \mathrm{at} 46$ | $10 \mathrm{dB} \mathrm{at} 12$ | $27 \mathrm{dB} \mathrm{at} 40$ | 25dB at $45$       | n/a        |

|            | GHz                             | GHz                             | GHz                             | GHz                |            |

| Hermet.    | No                              | n/a                             | Yes                             | NO                 | n/a        |

| Ambient    | Air                             | n/a                             | n/a                             | n/a                | n/a        |

Table 1.3: Commercially available RF packages (cont.).

<sup>a</sup>Measurements are performed on different materials, different line lengths, and different metal thicknesses therefore are not comparable.

insertion loss of the transition is 0.06 dB and according to the publicly available data this is the lowest reported loss for any MEMS package. The measured return loss is below -18 dB up to 40 GHz. In compliance with the information summarized in Table 1.1 the RF performance is well within the limits set by the MEMS device. The transition to the device is done through via-holes etched in silicon, meaning that the sealing ring and the feeding lines do not intersect. Its fabrication process is based on standard micromachining techniques and therefore the same architecture can be used with a variety of RF MEMS structures. Additionally, keeping the sealing ring and the feed lines separate provides unprecedented flexibility on the bonding technique used. The only limitation set by the architecture is that the temperature can not go beyond 400° C since that severely deforms the Au plated lines. However, as was mentioned previously, RF MEMS are also fabricated by thin film metals such as gold or nickel and therefore any temperature above 400° C will severely deteriorate the MEMS performance as well.

In addition to the aforementioned properties the packaging architecture presented

| Company     | Use        | Material    | Sealing     | Hermet. | Ambient |

|-------------|------------|-------------|-------------|---------|---------|

| Michigan    | Resonators | Si/Glass/Si | Localized   | Yes     | Air     |

| Prof.Najafi |            |             | Heating     |         |         |

| Michigan    | Resonators | Ni          | Thin Films  | Yes     | Vacuum  |

| Prof.Najafi |            |             |             |         |         |

| Michigan    | Resonators | Si/Glass    | LPCVD       | Yes     | Silane  |

| Prof.Wise   |            |             |             |         |         |

| Berkeley    | Resonators | Si/Glass    | Rapid       | Yes     | Air     |

| Prof.Lin    |            |             | Thermal     |         |         |

| Berkeley    | Resonators | Si/PSG/     | LPCVD       | Yes     | Vacuum  |

| Prof.Lin    |            | SiNi        |             |         |         |

| Omron       | RF<2GHz    | Glass       | Glass Frit  | Yes     | n/a     |

| IMEC vzw    | RF IL 0.7  | Si/ BCB/    | BCB         | No      | n/a     |

|             | dB, RL 22  | AF45        | epoxy       |         |         |

|             | dB at $40$ |             | CPW         |         |         |

|             | GHz        |             | under seal  |         |         |

| IMEC vzw    | RF         | Solder      | Indent Re-  | Yes     | n/a     |

|             |            |             | flow        |         |         |

| Rockwell    | Resonators | SOI Si      | Epoxy       | Yes     | Liquid  |

| Raytheon    | Resonators | Si          | Thermo-     | Yes     | Vacuum  |

|             |            |             | compression |         |         |

| Lockheed    | RF         | Si/GaAs/    | Stage B     | No      | n/a     |

| Martin      |            | Polyimide   | epoxy       |         |         |

| Tokyo Univ. | Resonators | Si          | Surface     | Yes     | Vacuum  |

|             |            |             | Activated   |         |         |

Table 1.4: MEMS Packages.

in this thesis is fabricated on the same wafer as the RF MEMS, thus reducing the number of necessary interconnects to a minimum. This topic will be revisited in Chapter 6 where the advantages of this on-wafer approach will be analyzed in detail. Even though the design is compatible with multiple sealing techniques thermocompression bonding is selected. The RF MEMS is hermetically packaged in an ambient of nitrogen. Accelerated tests demonstrated that the mean time to failure of the package is over 200 years in "tropical" conditions.

### **1.4** Simulation Techniques

High performance electromagnetic simulation tools have been extensively used in this thesis for design and characterization of silicon micromachined components. Since the majority of the investigated structures are three-dimensional in nature High Frequency Structure Simulator (HFSS) [10] is broadly utilized for analyzing vertical transitions, filters and packages. This software allows the user to design arbitrary three-dimensional structures composed of various materials and to excite them with an appropriate electromagnetic source. The architecture is then solved using an adaptive meshing procedure and Finite Element Method (FEM) to provide the electric and magnetics field within the problem region. By post-processing these field values the user can extract the S-parameters,  $\epsilon_{eff}$ , characteristic impedance of the interconnects, and many other parameters of interest. A two-dimensional FEM solver [11] has also been used for portions of this thesis, mainly for estimating input impedances of various transmission lines.

Planar structures have been analyzed using Method of Moments (MOM) based solvers [12, 13]. MOM relies in solving for the electric current on the structures, instead of the electric field, and is therefore more efficient for two dimensional problems. Additionally, for simulating lumped components and distributed elements Agilent Advanced Design System (ADS) has been used [14].

### **1.5** Fabrication Facilities

Extensive fabrication is necessary for the completion of this thesis. Most of the experimental work involved is carried out in the Solid State Electronics Laboratory (SSEL) of the University of Michigan. This is a \$25 million facility funded by state support and fees generated by industry and academic usage. Central to solid-state electronics research is the microelectronics processing facility. This laboratory, which

is housed in 6000 sq. ft. of class 1000, class 100, and class 10 clean space, is equipped with state-of-the-art tools for materials preparation and characterization with in-situ diagnostics, epitaxial growth, device fabrication with feature sizes smaller than 0.1  $\mu$ m, and device characterization. The entire facility, is used by over one hundred students and researchers and is managed and maintained by a well-qualified staff. The lab contains all of the major pieces of processing equipment needed to build the components presented in this study. These include mask making, front and backside photolithography, furnace oxidation systems, dry pattern transfer (plasma, RIE), ion-beam deposition and milling, vacuum evaporation and sputtering, chemical vapor deposition, and bonding.

Additional fabrication steps such as anisotropic wet etching (KOH and TMAH), electroplating, and supercritical  $CO_2$  drying of MEMS devices is performed at the fabrication facilities of the Radiation Laboratory, at the University of Michigan. Finally, for the first part of this thesis, some microwave lines are printed using a milling machine located at the same laboratory.

## **1.6** Measurement Techniques

The high frequency circuit measurements presented in this thesis are acquired using a HP 8510C Vector Network Analyzer connected to an Alessi probe station. A photograph of the measurement set up is presented in Fig.1.2. For 2-40 GHz measurements the system consists of a HP8350B sweep oscillator connected to a HP8516A S-parameter test set. Model 40A GGB picoprobes are used for on-wafer measurements. For W-band measurements a HP W85104A millimeter-wave test set is supplying signals though WR-10 waveguides and model 120A-BT GGB picoprobes. For all calibrations the Though-Reflect-Line (TRL) method is used with on-wafer calibrations standards fabricated in conjunction with the circuits to be tested. Multical, developed by NIST, is used to implement the TRL calibration [15]. For the hermeticity tests the reliability testing facilities of the Wireless Integrated Microsystems (WIMS) Center at the University of Michigan are used.

Figure 1.2: Measurement set-up.

## 1.7 Dissertation Overview

This thesis explores the development of a low-loss, on-wafer package for RF MEMS switches. The use of silicon micromachining and novel photolithographic processing are also investigated to further the case of silicon-based microwave and millimeter wave circuitry.

Chapter 2 examines the problem of cross-talk between adjoining interconnects printed on the same wafer. X and W-band circuits will be theoretically and experimentally investigated, along with the effects of open-end discontinuities, vias printed in close proximity to RF lines, and parasitic fields launched from vertical transitions.

Chapter 3 is devoted to the design and fabrication of low-loss interconnects on low-

resistivity silicon wafers. The purpose of this investigation is to research the possibility of creating high performance lines on low-quality silicon using intermediate polyimide layers micromachined using reactive ion etching. Both theoretical and experimental results will be presented.

Chapter 4 analyzes evanescent mode resonators and filters designed for micromachined silicon wafers. These filters have excellent performance, minute size and are easily integrated with other planar circuits, thus making them very attractive for system-on-a-chip configurations.

Chapter 5 explores the possibility of creating an on-wafer packaging scheme for RF MEMS switches utilizing silicon micromachining. The design and fabrication process for a low insertion loss RF transition will be analyzed in detail along with the measured response of the packaged RF MEMS. Moreover, the use of electrodeposited photoresist for creating multilevel transmission lines will be investigated.

Chapter 6 provides a brief overview of the importance of hermetic packaging along with some details related to reliability metrology and accelerated testing. It concludes with the presentation of the hermeticity tests for the on-wafer packaging scheme developed in this thesis.

Chapter 7 summarizes the accomplishments detailed in this dissertation, illustrates other potential applications of evanescent mode filters, summarizes some potential MEMS tuning mechanisms and introduces the extensive reliability tests to be undertaken for evaluating the hermeticity and durability of the on-wafer package.

# CHAPTER 2

# **Isolation in Three Dimensional Integrated Circuits**

## 2.1 Introduction

W ITH ever increasing demands to produce high-density microwave modules, achieving adequate isolation between circuit elements becomes more difficult. This is a particular concern for transceiver applications where high isolation is necessary to ensure receiver sensitivity and prevent leakage between channels. Multi-layer architectures incorporating complex circuits in a common substrate material pose the most challenging isolation problem. When circuits are printed on a common substrate, surface waves excited by planar discontinuities or leaky modes tend to induce parasitic currents on neighboring interconnects and circuits leading to unwanted interference. This parasitic coupling becomes increasingly more problematic as circuits are printed on multi-layered structures for higher density and smaller size. In such structures, proximity effects are dependent on interconnect geometry. Appropriate layout design and relative placement of lines, vias, and vertical transitions is necessary in order to reduce any unwanted interference. It is the purpose of this study to identify the limits imposed in isolation by three-dimensional integration and on-wafer packaging, utilizing silicon micromachining.

As microstrip was the prevalent transmission line in the early 80's investigation

of microstrip-to-microstrip crosstalk and electromagnetic coupling became a critical issue for design and simulation of MMICs [16]. The inaccuracies between the theoretical results and the measured data observed initiated an extensive study of crosstalk using various analytical tools and employing both quasi-static approximations and full-wave solvers. Spectral domain methods are used at [17, 18, 19] where the surface waves are related with the presence of poles in the spectral Green's function associated with the problem. The parasitic cross-talk between various line configurations has also been addressed using the Method of Moments [20], along with Finite Element Method [21] and Finite Difference Time Domain method [22]. In addition, for the same problem, potential and induced EMF methods have been utilized in [23] and the GCM (Generalized Coupling Model) has been used by Swanson [24]. The results of the aforementioned studies are consistent and are corroborated by the present study.

Crosstalk between adjoining interconnects is caused by a variety of mechanisms. Thus, when the distance between the lines is small compared to a dielectric wavelength, the predominant reason for decreased isolation is near-field coupling due to open-end effects and discontinuities. However, when the separation between interconnects increases, the coupling occurs due to the surface waves  $(TM_0 \text{ or } TE_0)$  propagating inside the dielectric substrate. Such modes can be excited by discontinuities but can also be launched by leaky dominant modes. Published studies [17, 18] show that a leaky dominant mode is present at higher frequencies on conventional microstrip lines printed on an isotropic substrate. This mode has a leakage into the  $TM_0$  surface wave and exists independently of and in addition to the usual dominant mode. An important observation is that near the strip the leaky mode has a field distribution that closely resembles that of the bound mode. Therefore, both modes can be excited by conventional microstrip feeds. The critical frequency where the leakage onset occurs is reported to be as low as a few gigahertz depending on the substrate characteristics (thickness and dielectric constant). This leaky mode may interact with other lines or components in the microstrip package, thus accounting for an increase in crosstalk. As seen in [17, 18], reduction of the thickness and dielectric constant of the substrate can decrease the leakage effects either by moving the critical frequency out of the band of operation or by diminishing the leakage constant. Both can be achieved by local reduction of the substrate thickness. Silicon micromachining with wet etching (potassium hydroxide or tetramethyl amonium hydroxide) can be utilized to create small cavities under the microstrip lines.

The coplanar waveguide, proposed by Wen in 1969, consists of two slots printed on a dielectric substrate. Its principal advantage is that it is well suited for use with field effect transistors, especially at mm-wave frequencies where RF grounding must be close to the device. Via-holes are not necessary for ground equalization and fragile semiconductors need not be made excessively thin. As shown in [25], the loss and dispersion of the CPW are comparable and in some cases better than the ones exhibited by the microstrip lines. For an infinite ground plane the lowest order surface wave mode is the  $TM_0$  and at the frequency where the phase velocity of the surface wave becomes equal or smaller than the velocity of the CPW mode highly dispersion behavior is observed. For conventional substrate thickness between 100  $\mu$ m and 500  $\mu m$  this frequency is of the order of hundreds of GHz. However, this is true only for infinite architectures (substrate and interconnects) and straight lines, without any bends or discontinuities. In a realistic structure multiple lines of finite length are printed on a common substrate of finite dimensions [26]. Additionally, these structures are usually packaged including backside metallization, top and/or side metallic walls. The finite dimension of the interconnects, along with the packaging effects can change the leakage properties of the lines significantly and can cause leakage to occur at much lower frequencies than expected [27, 28].

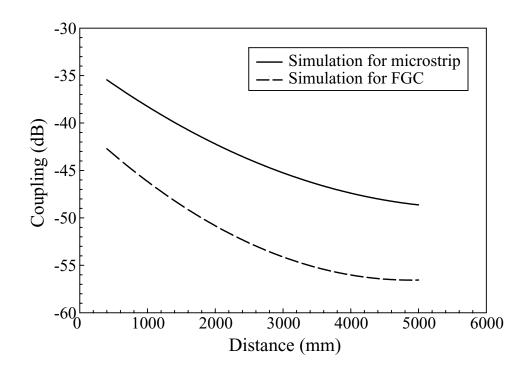

The finite ground coplanar waveguide (FGC) has an additional major advantage in its ability to suppress parasitic modes. If symmetry around the center conductor is maintained or airbridges are used to equalize the potential on the two ground planes, the coupled slotline mode is eliminated. Reducing the total width of the line bellow  $\lambda_g/2$  can move the cut-off frequency out of the band of operation, thus suppressing all higher order modes. Therefore, the FGC line does not require vias for ground equalization, and its propagation characteristics are not sensitive to the substrate thickness and presence of backside metallization. Moreover, the finite ground CPW has lower leakage constant compared with the infinite CPW [19]. In the case of the FGC line the lowest surface wave mode is the TE<sub>0</sub> and therefore leakage occurs at higher frequencies compared to the infinite ground plane CPW line. Tsuji in [19] also illustrates that the reduction of the ground plane width can significantly reduce the leakage constant. A similar observation is made in [29] where the reduction of the ground plane width increased the isolation between two FGC lines. This similarity reveals the strong relationship among the leaky modes and the crosstalk between lines.

According to previous results the onset of leaky modes occurs at much higher frequencies for the FGC line compared with the microstrip line and therefore FGC lines provide a wider single-mode frequency range of operation [18, 19]. Moreover, the FGC line has less field overlap with the surface wave modes than microstrip, and interacts weakly with them [30]. As is illustrated in this reference the coplanar waveguide field overlaps depend strongly on the value of the total width of the line. In this respect the main difference between the two types of interconnects is the degree of freedom in their physical layouts. On a given substrate the microstrip has two degrees of freedom: line width and substrate thickness. Changing both of these, while keeping the line impedance constant, does not change the field overlaps. In contrast, the total width of the CPW (ground plane, slot and line width) can be varied independently of line impedance in order to minimize the field overlap with surface wave modes. After examining all the aforementioned theoretical and experimental results it is expected that the FGC line will demonstrate better isolation as compared to a microstrip line. Consequently, the following study will focus on FGC interconnects and their behavior.

Details of this study are presented in the subsequent sections. The design and fabrication process for the X and W-band structures is described first, followed by the results for single and multi-layer architectures. The chapter proceeds with the investigation of open-end effects, along with the deterioration in isolation caused by the existence of vias in close proximity to interconnects. Finally, it has been shown [31] that vertical transitions may launch parasitic fields, which couple to adjoining lines and result in increased coupling, if designed improperly. The understanding of these effects on coupling and the required separation to achieve desired isolation is investigated in this research. The outcome of this investigation, as presented in [32], is the creation of an extensive list of three dimensional interconnect architectures and their respective isolation. These results, mainly theoretical in nature, are focused on two frequencies 8 and 32 GHz, since these are the Deep Space frequency bands used by JPL. This chapter describes the experimental and a few of the theoretical results that are acquired. Appendix A is a comprehensive list of all the analyzed architectures.

## 2.2 Design of Isolation Architectures

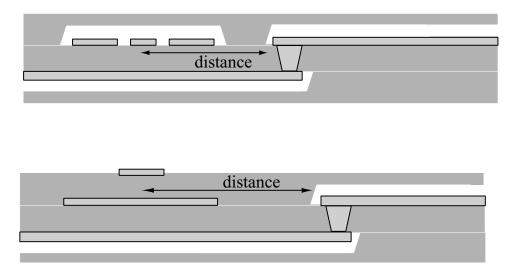

In view of the above, this study addresses coupling in multi-layer circuits with microstrip or coplanar waveguide as the underlying interconnect. The circuits under study are designed for X-band (8-12 GHz) as well as W-band (75-110 GHz), and thus different substrates are used. The X-band circuits are fabricated on 1.524 mm thick Duroid with dielectric constant ( $\epsilon$ ) of 2.92. The W-band circuits are fabricated on high-resistivity 100  $\mu$ m thick silicon with dielectric constant of 11.7. High resistivity silicon wafers with resistivity of 2500  $\Omega$ -cm, measured by a four point probe, are used in order to reduce the losses. Due to the high design frequency of 94 GHz the losses are a major factor in the performance of the circuits. A static 2-D electromagnetic solver is used to design a 50  $\Omega$  line for each substrate and line type (Duroid or silicon, microstrip or FGC) [11]. All FGC X-band transmission lines are of dimensions 1520-380-2540  $\mu$ m (center conductor-aperture-ground), while all microstrip X-band transmission lines presented are of dimensions 2540-7620  $\mu$ m (signal conductor-ground plane). In W-band, only FGC lines are examined of dimensions 40-24-106  $\mu$ m (center conductor-aperture-ground).

An efficient tool for analyzing coupling structures should allow analysis of three dimensional topologies with vertical transitions [16] and it should account for frequency dependent effects such as dispersion, radiation, and higher-order mode propagation. All the simulation results presented in this study are obtained with HFSS, which has all of the above characteristics [10]. The structures are analyzed including conductor and dielectric losses and are surrounded by a radiation boundary, which absorbs all the incident fields simulating a free-space environment. However, the fabricated circuits have always finite dimensions and some reflections are bound to happen at the edges of the wafer due to the air-dielectric interface. These reflected fields can couple back to the lines giving slightly different measured data. Nevertheless the simulations performed with this type of modelling gave results that very closely approximate the measurements in the majority of the cases.

# 2.3 Fabrication of Isolation Structures

#### 2.3.1 X-band Designs

The X-band circuits are fabricated on Rogers Duroid ( $\epsilon$ =2.94, thickness:1.524 mm) with the use of a milling machine. The interconnects are milled on separate wafers which are then bonded together in order to create the multilayered structures. Cavi-

ties and vias for the vertical transitions have been drilled in the dielectric substrate using appropriate milling tools. SMA connectors are soldered at the one end of each line, leaving the other open. This creates a standing wave, which, as will be shown shortly, increases the coupling by 6 dB if compared to a matched line.

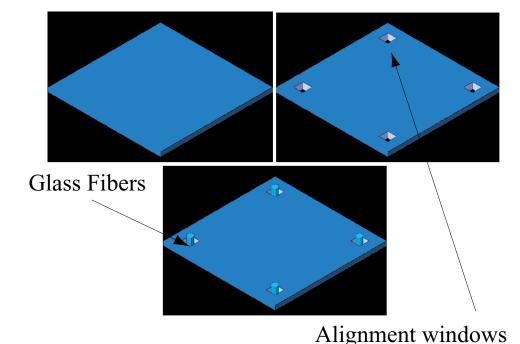

Figure 2.1: Alignment of silicon wafers using glass fibers.

#### 2.3.2 W-band Designs

The W-band circuits are printed on 100  $\mu$ m thick high-resistivity double-side polished silicon wafers with 6600 Å SiO<sub>2</sub> on both sides. Three wafers are used for the packaged isolation study and are fabricated separately. The four main fabrication steps are thin film resistor deposition, circuit metallization, aperture definition, and anisotropic wet etching of the protective air cavities and probe windows.