### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

## **NOTE TO USERS**

This reproduction is the best copy available.

UMI°

### Design and Analysis of Series and Shunt MEMS Switches

by

### Jeremy Bert Muldavin

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2001

### Doctoral Committee:

Professor Gabriel M. Rebeiz, Chair Professor Linda P. B. Katehi Professor Khalil Najafi Associate Professor Steve Yalisove UMI Number: 3016923

### UMI Microform 3016923

Copyright 2001 by Bell & Howell Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346 © Jeremy Bert Muldavin 2001 All Rights Reserved To my mother and father, Jean and Roger Muldavin.

### ACKNOWLEDGEMENTS

I would like to thank all of the people who have helped me through the difficult task of creating this dissertation. First and foremost, I would like to thank my advisor, Professor Gabriel Rebeiz, for encouraging me to attend graduate school and pursue a doctoral degree. Professor Rebeiz has provided me with instrumental advice and understanding over the years. I would also like to thank my committee members for their time and support: Professor Linda Katehi, Professor Khalil Najafi, and Professor Steve Yalisove.

Thank you to the students who showed me the way: Sanjay Raman, Andy Brown. N. Scott Barker, and Dr. Leo DeDominico just to name a few. Thank you to my colleagues for your friendship and advice: Joe Hayden, Bill Chappell, Jad Rizk, Lee Harle, Jim Becker, Alex Margomenos, Bernhard Schoenlinner, Dimitrios Peroulis, Ron Reano, and Guan Leng Tan. I wish you all the best of luck.

Thank you to my family and friends, especially Mark and Zoë Sakalauskas for feeding for letting me live with them while I finished up.

Thank you to my parents who were always caring and supportive. They gave me the love of learning and the freedom to pursue it.

Lastly, I would like to thank my wife, Katherine Herrick, for her embracing love, support, and strength. I would not have finished without her.

### **PREFACE**

This thesis presents series and shunt RF Mirco-Electro-Mechanical (MEMS) switches and varactors, emphasizing the electromagentic modeling and design as well as mechanical modeling. Comprehensive modeling and design are verified by extensive fabrication and testing of both series and shunt MEMS devices. These devices were implemented into high-isolation (-60 to -40 dB from 2 to 40 GHz) switch circuits. Also, a detailed electro-mechanical 1-dimensional dynamic simulation has been done for MEMS switches and varactors. It is also the author's goal to establish general performance parameters and limitations of MEMS devices.

## TABLE OF CONTENTS

| DEDIC  | ATIO               | N                                                               | ii            |

|--------|--------------------|-----------------------------------------------------------------|---------------|

| ACKN   | OWLE               | DGEMENTS                                                        | iii           |

| PREFA  | <b>CE</b>          |                                                                 | iv            |

| LIST O | F TAE              | BLES                                                            | viii          |

| LIST O | F FIG              | URES                                                            | ix            |

| LIST O | F APF              | PENDICES                                                        | xv            |

| CHAPT  | TERS               |                                                                 |               |

| 1      | INTR<br>1.1<br>1.2 | What are MEMS Switches and What are They Good For?              | 1<br>1<br>s 5 |

|        | 1.3                | MEMS Market                                                     | 6             |

|        | 1.4                | State of the Art                                                | 7             |

|        | 1.5                | Fabrication Techniques                                          | 9             |

|        | 1.6                | Measurement Techniques                                          | 9             |

|        | 1.7                | Thesis Overview                                                 | 11            |

| 2      | ELEC               | TROMAGNETIC MODELING OF SHUNT SWITCHES .                        | 12            |

|        | 2.1                | Introduction                                                    | 12            |

|        | 2.2                | Physical Description of MEMS Shunt Switches                     | 13            |

|        | 2.3                | Circuit Model of the MEMS Capacitive Shunt Switch               | 14            |

|        | 2.4                | Electromagnetic Modeling of MEMS Shunt Switches                 | 16            |

|        |                    | 2.4.1 Off-State Capacitance                                     | 16            |

|        |                    | 2.4.2 Down-State Capacitance and Capacitance Ratio              | 17            |

|        |                    | 2.4.3 Current Distribution                                      | 19            |

|        |                    | 2.4.4 Series Resistance                                         | 20            |

|        |                    | 2.4.5 Inductance                                                | 22            |

|        |                    | 2.4.6 Loss                                                      | 26            |

|        | 2.5                | Fitting CLR Parameters to S-Parameter Shunt-Switch Measurements | 27            |

|        |                    | 2.5.1 Up-State Capacitance                                      | 29            |

|        |                    | 2.5.2 Down-State Capacitance and Inductance                     | 29            |

|        |                    | 2.5.3 Series Resistance of the MEMS bridge                      | 32            |

|   | 2.6  | Inline MEMS Capacitive Shunt Switches                     | 34 |

|---|------|-----------------------------------------------------------|----|

|   | 2.7  | DC-Contact MEMS Shunt Switches                            | 35 |

| 3 | MEM  | IS SHUNT SWITCHES AND HIGH-ISOLATION SWITCH               |    |

|   | CIRC | CUITS                                                     | 37 |

|   | 3.1  | Introduction                                              | 37 |

|   | 3.2  | Biasing of MEMS Switches                                  | 38 |

|   | 3.3  |                                                           | 39 |

|   |      | 3.3.1 C-band to X-Band Designs                            | 39 |

|   |      | 3.3.2 X-Band Switch Examples                              | 41 |

|   |      | 3.3.3 Millimeter-Wave Shunt Switches                      | 46 |

|   |      | 3.3.4 W-Band Shunt Switches                               | 48 |

|   |      | 3.3.5 Novel Metal-to-Metal Contact Inline Shunt Switch    | 48 |

|   | 3.4  | Inductively-Resonant High-Isolation X-Band Shunt Switches | 52 |

|   | 0.4  | 3.4.1 Standard Configuration                              | 54 |

|   |      | 3.4.2 Inline Configuration                                | 57 |

|   |      |                                                           | 58 |

|   |      |                                                           |    |

|   | 9 5  | 3.4.4 Inline Double-Capacitance Design                    | 58 |

|   | 3.5  | Matching of Shunt Capacitive Switches                     | 60 |

|   |      | 3.5.1 The T-match                                         | 61 |

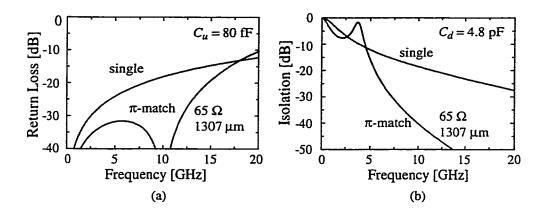

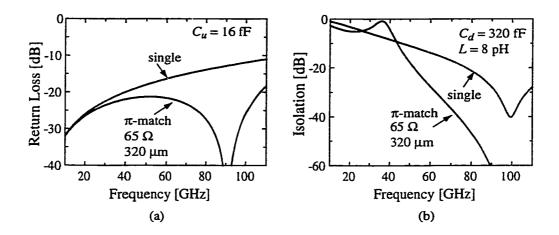

|   | 0.0  | 3.5.2 The $\pi$ Match                                     | 64 |

|   | 3.6  | Design of High-Isolation Tuned Shunt Switches             | 66 |

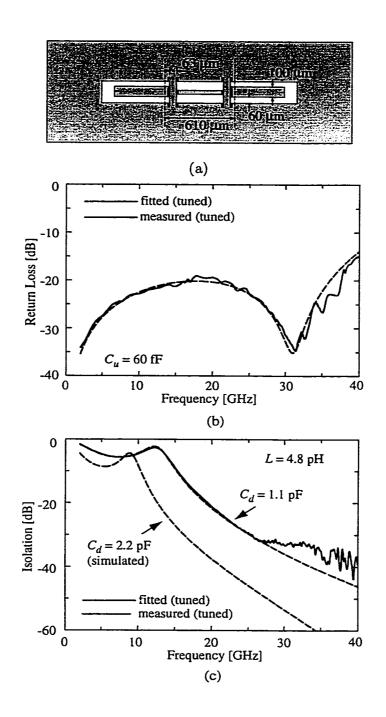

|   |      | 3.6.1 A Ka-Band Tuned Switch                              | 67 |

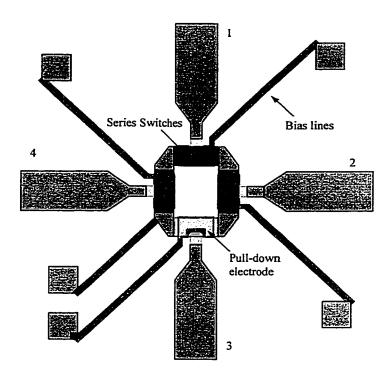

|   | 3.7  | The Cross Switch                                          | 68 |

|   | 3.8  | The Double Tuned Switch                                   | 71 |

| 4 | ELEC | CTROMAGNETIC MODELING OF SERIES SWITCHES .                | 73 |

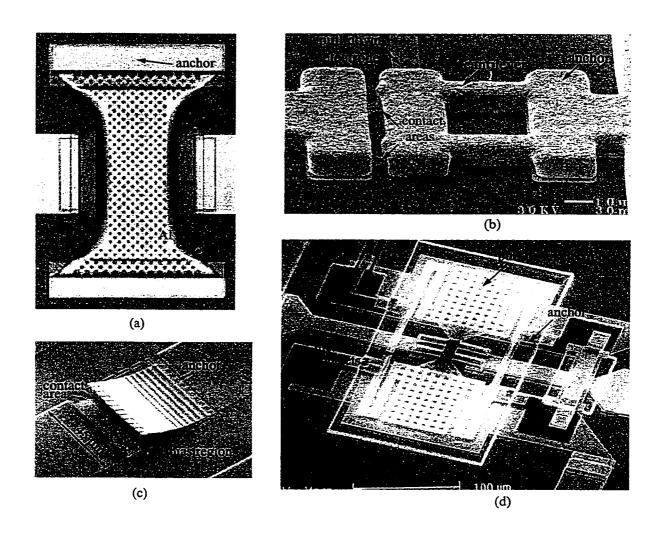

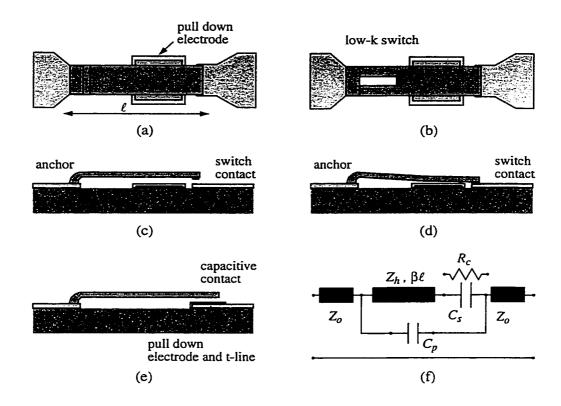

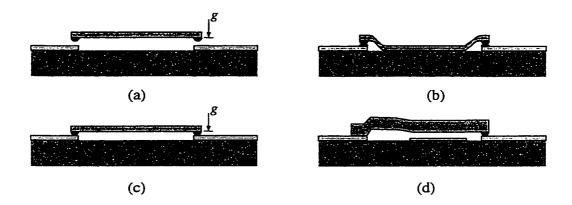

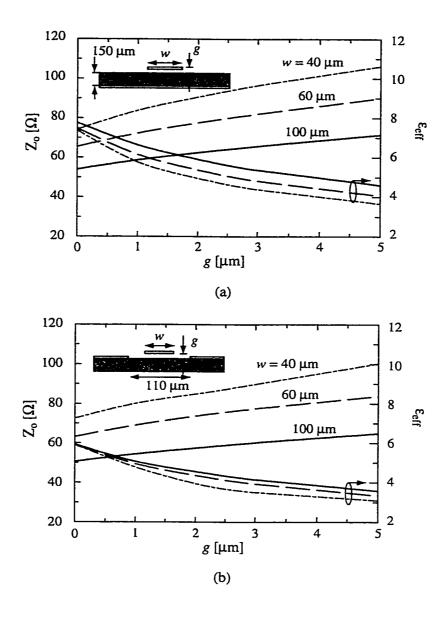

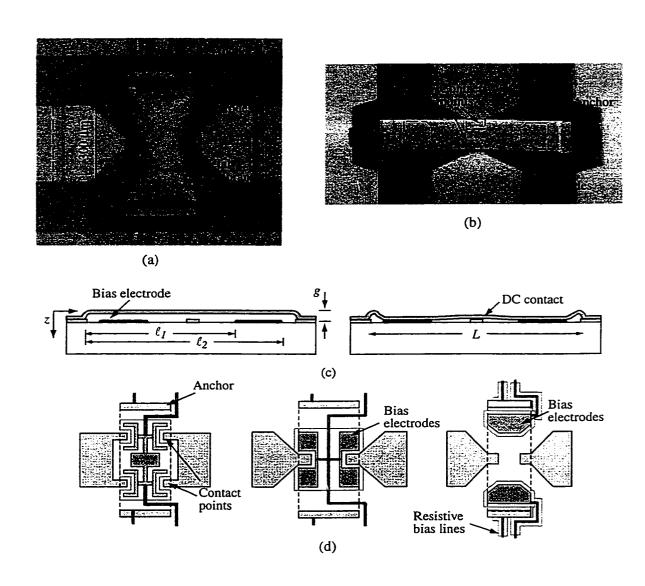

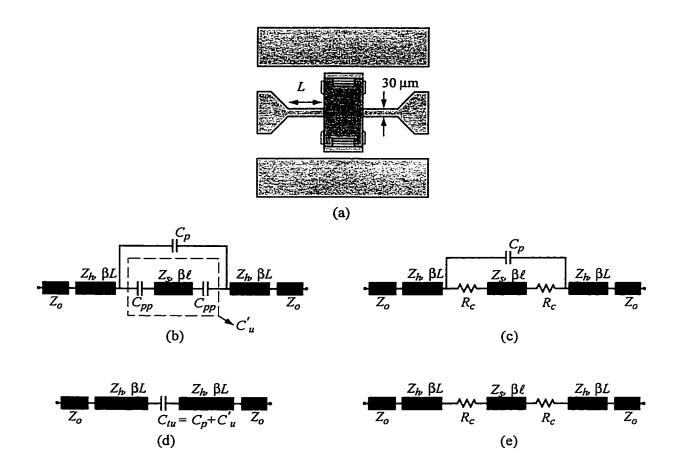

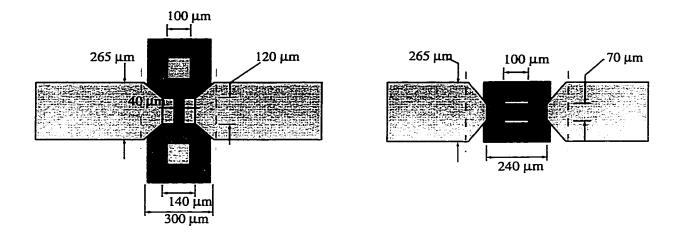

|   | 4.1  | Physical Description of MEMS Series Switches              | 73 |

|   | 4.2  | Electromagnetic Modeling of MEMS Series Switches          | 77 |

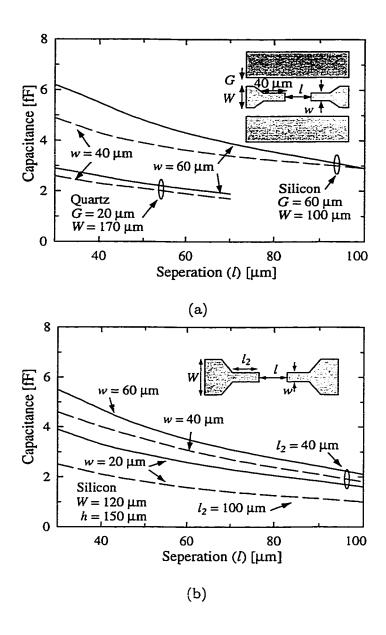

|   |      | 4.2.1 Up-State Capacitance:                               | 77 |

|   |      | 4.2.2 Current Distribution                                | 78 |

|   |      | 4.2.3 Down-State Resistance                               | 78 |

|   |      |                                                           | 81 |

|   |      |                                                           | 81 |

|   | 4.3  |                                                           | 85 |

|   | 2.0  | •                                                         | 85 |

|   |      | •                                                         | 87 |

|   | 4.4  |                                                           | 88 |

|   | 4.5  | •                                                         | 89 |

|   |      | •                                                         |    |

| 5 |      | IS SERIES SWITCHES AND HIGH ISOLATION SWITCH              |    |

|   |      |                                                           | 91 |

|   | 5.1  |                                                           | 91 |

|   | 5.2  |                                                           | 91 |

|   | 5.3  |                                                           | 94 |

|   | 5.4  | •                                                         | 00 |

|   | 5.5  |                                                           | 02 |

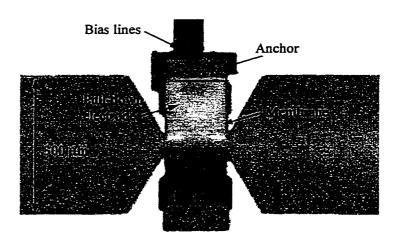

|   |      | 5.5.1 All-Metal Series/Shunt MEMS Switches                | 02 |

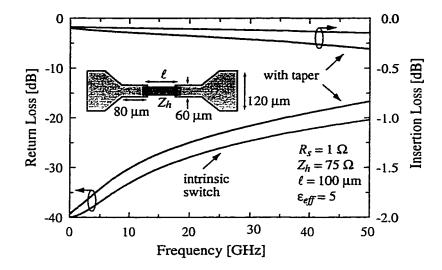

|         | 5.6  | Design of MEMS Capacitive Series Switches                    | 105 |

|---------|------|--------------------------------------------------------------|-----|

| 6       | MEC  | HANICAL MODELING                                             | 110 |

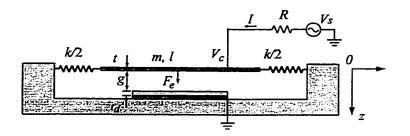

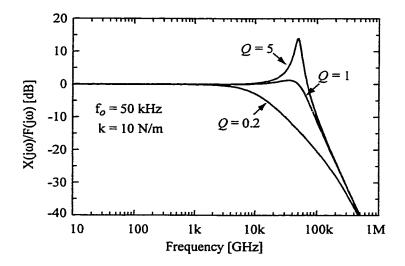

|         | 6.1  | Introduction                                                 | 110 |

|         | 6.2  | Electro-Mechanical Model of MEMS Switches                    | 111 |

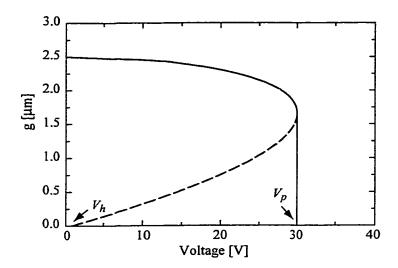

|         | 6.3  | Static Analysis                                              | 113 |

|         | 6.4  | Limit Expressions for Switching Time                         | 115 |

|         | 6.5  | Details of the Viscous Damping Mechanism                     | 116 |

|         | 6.6  | Numerical Simulations of the Switching Mechanics             | 119 |

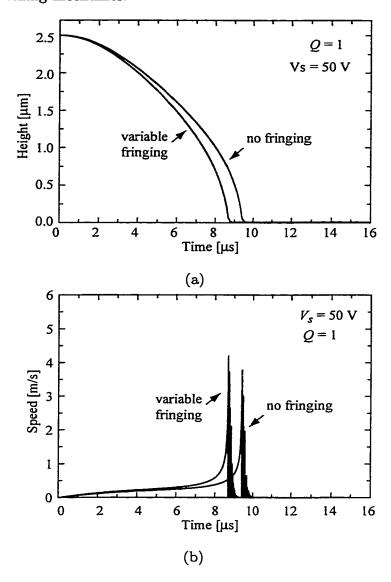

|         |      | 6.6.1 Switching Time                                         | 120 |

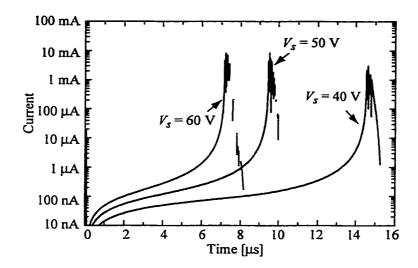

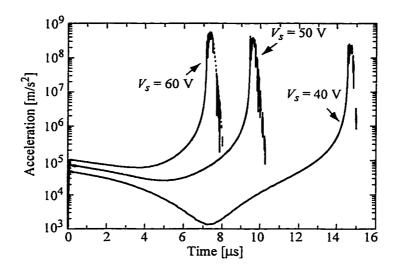

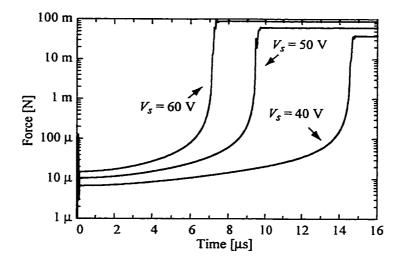

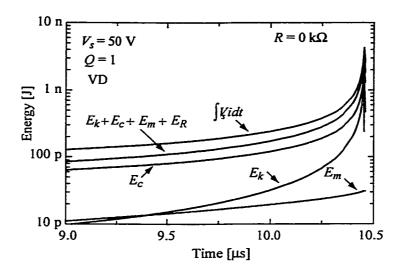

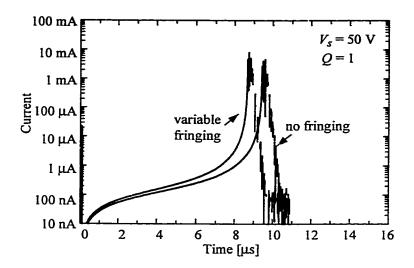

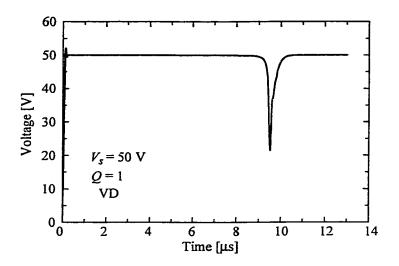

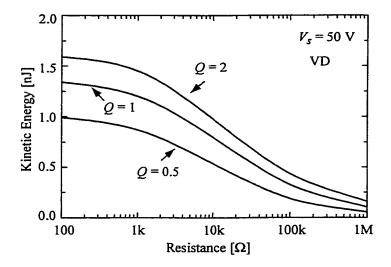

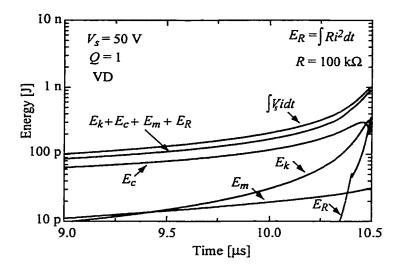

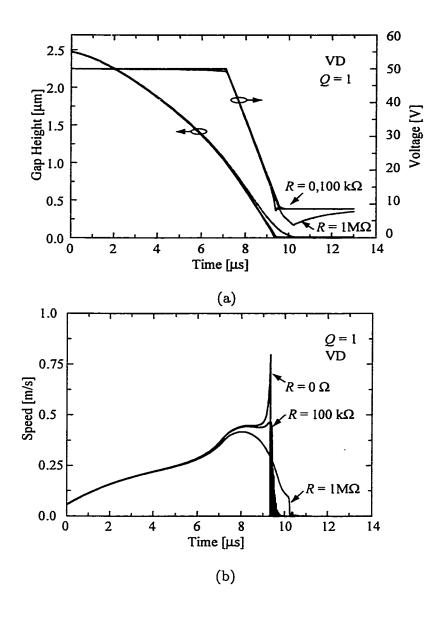

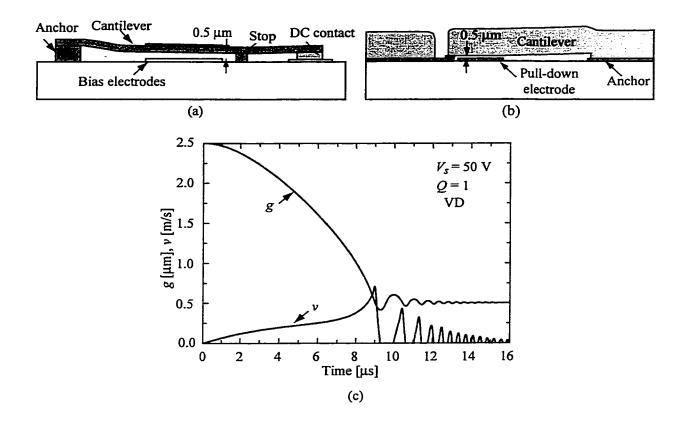

|         |      | 6.6.2 Switching Velocity, Acceleration, Current, and Energy  | 124 |

|         |      | 6.6.3 Effect of Fringing Capacitance                         | 128 |

|         |      | 6.6.4 Resistive Damping                                      | 130 |

|         |      | 6.6.5 Voltage Shaping                                        | 133 |

|         |      | 6.6.6 Gap-Stop Measures                                      | 133 |

|         | 6.7  | RF Model of MEMS Switches                                    | 136 |

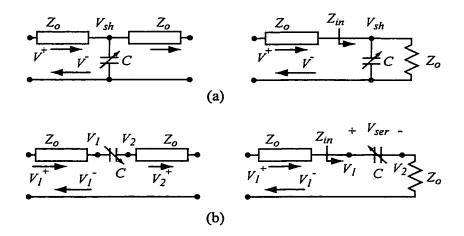

|         |      | 6.7.1 RF voltage across a MEMS shunt switch                  | 137 |

|         |      | 6.7.2 RF voltage across a MEMS series switch                 | 138 |

|         |      | 6.7.3 RF Power Handling                                      | 139 |

|         |      | 6.7.4 Source Voltage Noise, Intermodulation, and Phase Noise | 141 |

|         | 6.8  | Conclusions                                                  | 143 |

| 7       | FUTU | URE WORK                                                     | 144 |

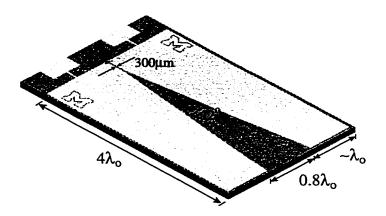

|         | 7.1  | All-Metal Series Switch for Microstrip                       | 144 |

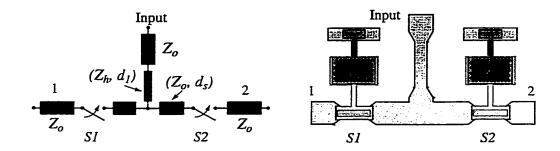

|         | 7.2  | Design of Single-Pole Multiple-Throw Series Switches         | 145 |

|         | 7.3  | 76 GHz M/A-COM Switch Examples                               | 149 |

|         | 7.4  | Increased Tuning Range and Switched State Varactors          | 149 |

|         | 7.5  | Tunable Resonators and Filters                               | 150 |

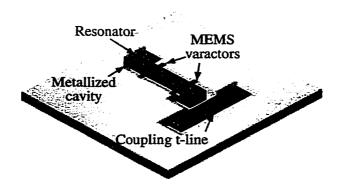

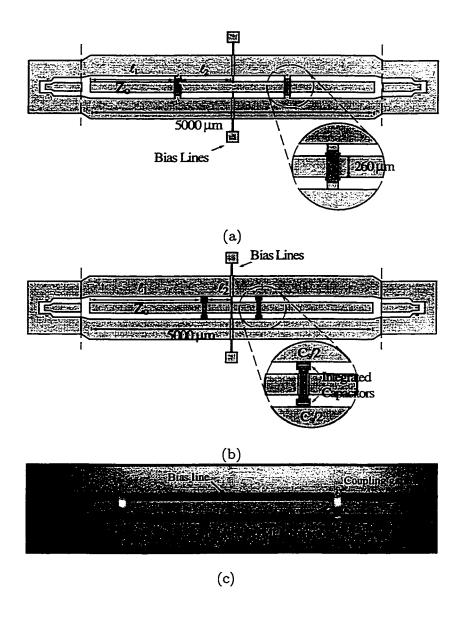

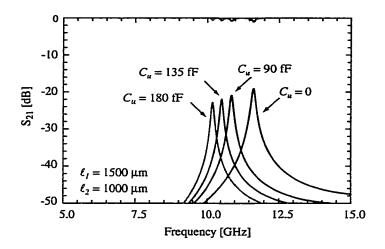

|         |      | 7.5.1 Variable Resonator                                     | 152 |

|         |      | 7.5.2 Switched Mode Resonator                                | 154 |

|         |      | 7.5.3 Inter-resonator Coupling Structures                    | 155 |

|         | 7.6  | Tunable Oscillators                                          | 155 |

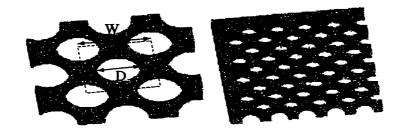

|         | 7.7  | Packaging                                                    | 156 |

| APPEN   | MICE | S                                                            | 157 |

| AL LUIV |      | ······································                       | 191 |

| BIBLIO  | GRAI | PHY                                                          | 180 |

## LIST OF TABLES

| <b>Table</b> |                                                                                                                                                                                     |     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1          | Performance comparison of FETs, PIN diode, and RF MEMS switches                                                                                                                     | 7   |

| 2.1          | Simulated static capacitance of a MEMS bridge ( $L=300~\mu\text{m},~t=2~\mu\text{m},~t_d=1500~\text{Å},~\epsilon_r=7.6$ )                                                           | 16  |

| 2.2          | MEMS bridge inductance for several bridges with various widths ( $L=300~\mu\text{m}$ , $t=2~\mu\text{m}$ ). The CPW line dimensions are $G/W/G=60/100/60~\mu\text{m}$ on high-      | 00  |

| 2.3          | resistivity silicon                                                                                                                                                                 | 23  |

| 2 1          | $t = 2 \mu \text{m}$ ) and $G/W/G = 60/100/60 \mu \text{m}$ ( $L = 300 \mu \text{m}$ , $t = 2 \mu \text{m}$ )                                                                       | 24  |

| 3.1          | Fitted MEMS switch inductance (L) for several designs with various inductive section geometries. The CPW line dimensions are $G/W/G = 96/160/96 \mu m$ on high-resistivity silicon. | 57  |

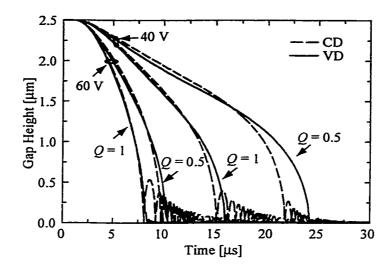

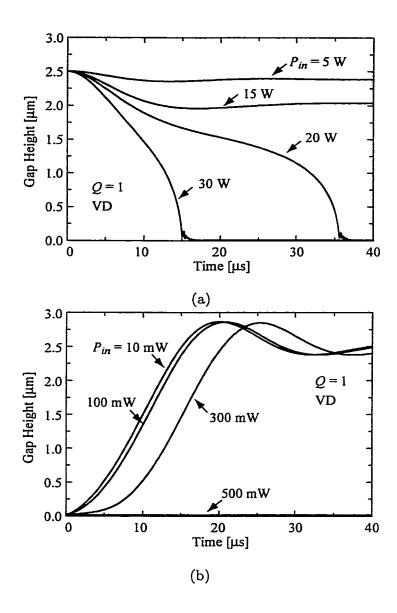

| 6.1          | Comparison of pull-down times for variable damping (VD) and constant damping (CD) of a gold MEMS switch described in Section 6.6                                                    | 121 |

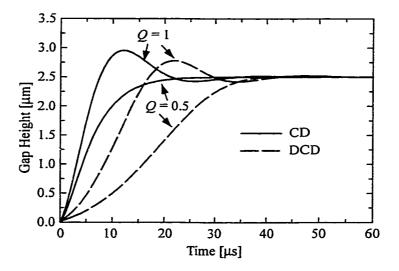

| 6.2          | Comparison of release times for variable damping (VD) and constant damping (CD) of a gold MEMS switch described above.                                                              | 122 |

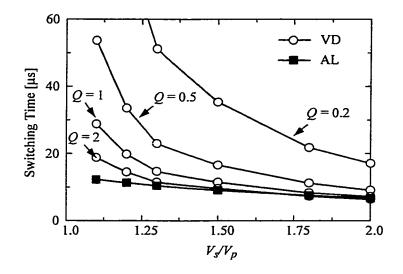

| 6.3          | Comparison of pull-down times for variable damping (VD) and damping-limited (DL $_1$ and DL $_2$ ) estimates of a gold MEMS switch described in Sec-                                | 122 |

| 6.4          | tion 6.6 (DL <sub>1</sub> is Eq. 6.18 and DL <sub>2</sub> is Eq. 6.19)                                                                                                              | 123 |

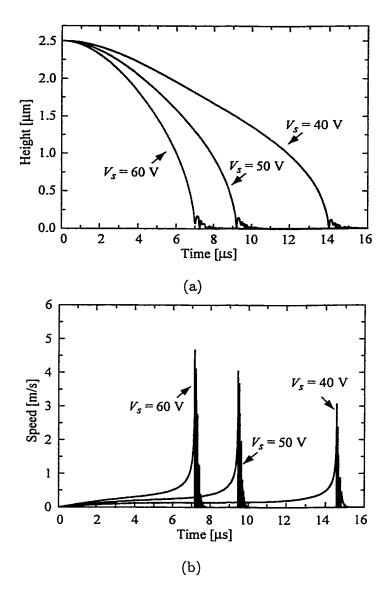

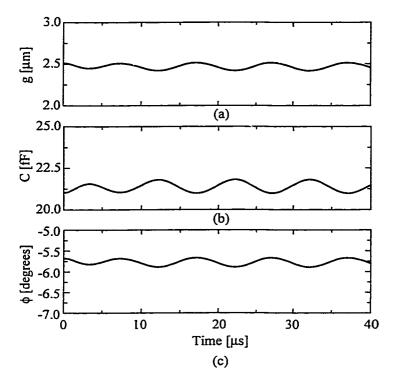

| 0.4          | 10 N/m, $f_o = 43$ kHz, $V_p = 30$ V, and a capacitive area of $100 \times 60 \ \mu\text{m}^2$ .                                                                                    |     |

| D 1          | Energy is in nJ                                                                                                                                                                     | 127 |

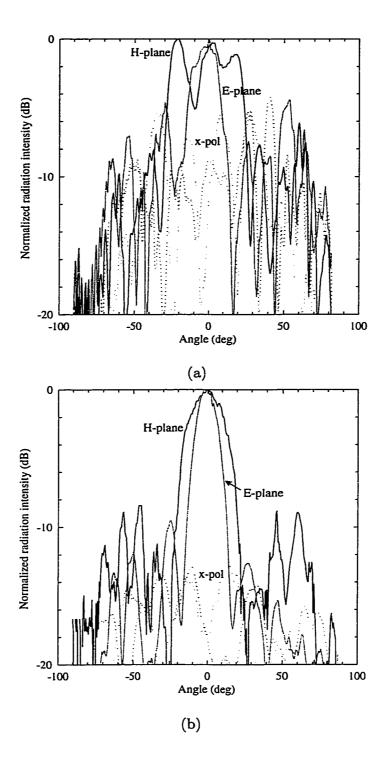

| B.1          | Comparison of the 3-dB and 10-dB beamwidths for three different 30 GHz TSA substrates                                                                                               | 176 |

## LIST OF FIGURES

| Figure |                                                                                                                                                          |            |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.1    | Photomicrograph of a MEMS device on a penny. (Courtesy Sandia National Labs.)                                                                            | 2          |

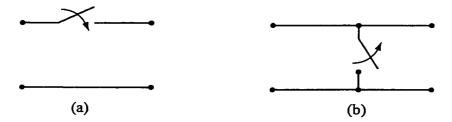

| 1.2    | Series (a) and shunt (b) configurations of MEMS switches                                                                                                 | 3          |

| 1.3    | Some application areas of MEMS switches: Phased arrays (a), switched-filter banks for wireless applications (b) and SP2T T/R switches (c)                | $\epsilon$ |

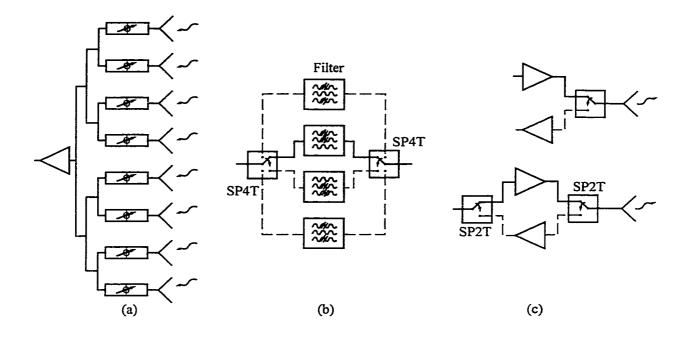

| 1.4    | Photomicrographs of the Raytheon shunt capacitive (a), Analog Devices series (b), Lincoln Labs series (c), and Rockwell Science Center series (d)        |            |

|        | MEMS switches.                                                                                                                                           | 8          |

| 1.5    | On wafer probe station (a) and HP8510C VNA (b) used at the University of                                                                                 |            |

|        | Michigan.                                                                                                                                                | 10         |

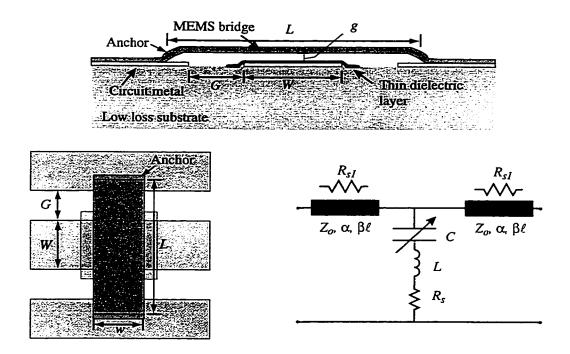

| 2.1    | Illustration of a typical MEMS shunt switch shown in cross-section and planview. The equivalent circuit is also shown                                    | 14         |

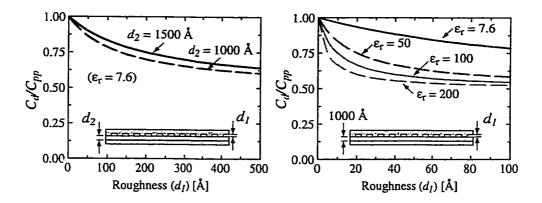

| 2.2    | Simulated down-state capacitance degradation versus roughness in the over-                                                                               |            |

|        | lying bridge layer for low (a) and high (b) dielectric constant materials                                                                                | 19         |

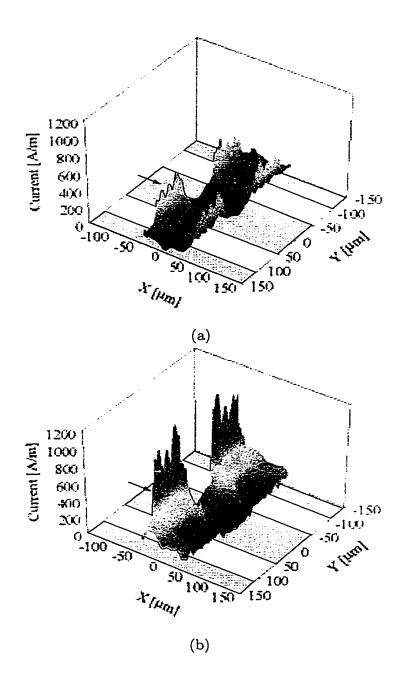

| 2.3    | Simulated current distribution on the MEMS bridge in (a) the up-state and (b) the down-state for an 80 $\mu$ m wide MEMS bridge over a 60/100/60 $\mu$ m |            |

|        | CPW line. A 1 W wave is incident from the left and travels in the +x-direction.                                                                          | 21         |

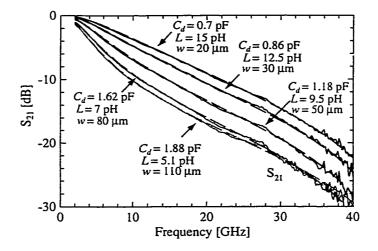

| 2.4    | Measured and fitted down-state S-parameters for MEMS switches of various                                                                                 |            |

|        | widths                                                                                                                                                   | 23         |

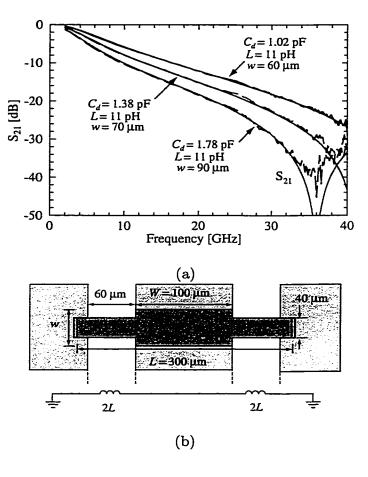

| 2.5    | Down-state measured and fitted S-parameters for MEMS switches where the                                                                                  |            |

|        | width of the section over the center conductor is varied and the portion over                                                                            |            |

|        | the CPW gap is held constant (a). The schematic and equivalent circuit for the inductance is shown in (b)                                                | 25         |

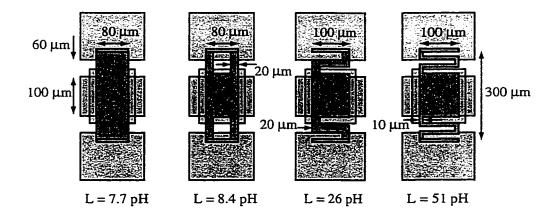

| 2.6    | • •                                                                                                                                                      | 25<br>25   |

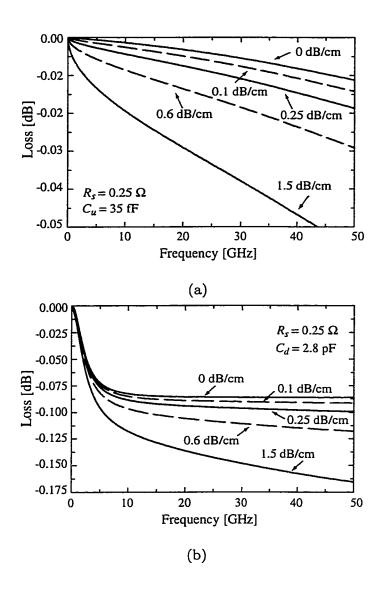

| 2.7    | Up-state (a) and down-state (b) simulated loss for various values of $R_s$ and                                                                           | 20         |

| 2.1    | $\alpha$ . The reference planes are 20 $\mu$ m from the edge of the MEMS switch                                                                          |            |

|        | $(w = 80 \ \mu\text{m})$                                                                                                                                 | 28         |

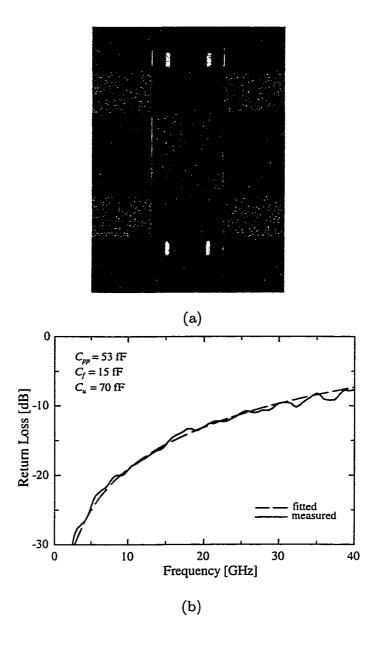

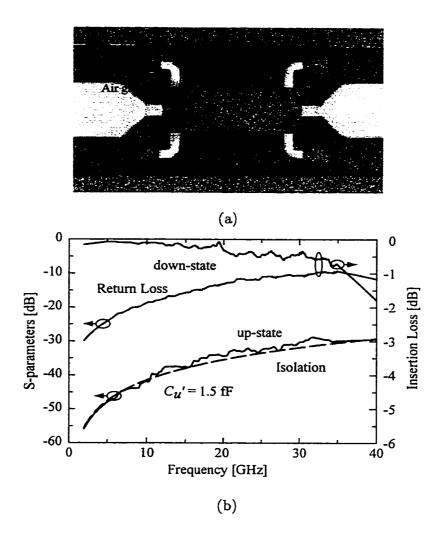

| 2.8    | Photomicrograph (a) of a MEMS shunt switch and (b) the up-state measured                                                                                 |            |

|        | and fitted return loss for an 80 $\mu$ m wide bridge with a nominal gap height of                                                                        |            |

|        | 1.5 $\mu$ m. The CPW center conductor is 100 $\mu$ m wide                                                                                                | 30         |

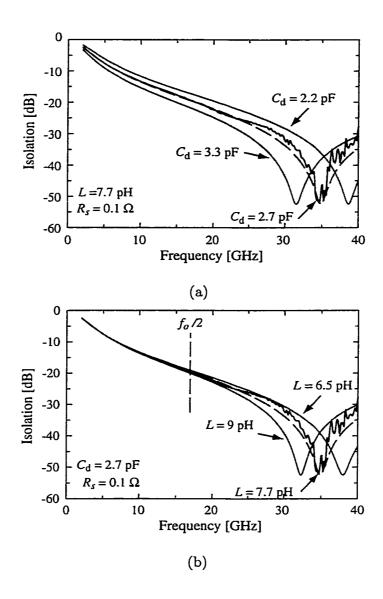

| 2.9    | Down-state measured and fitted isolation for a MEMS shunt switch, showing                                                                                |            |

|        | the accuracy of the $CLR$ fit over 1-40 GHz. ( $L=300~\mu\mathrm{m},~w=80~\mu\mathrm{m},$                                                                |            |

|        | $W = 100 \ \mu \text{m}, t_d = 1500 \ \text{Å}.$                                                                                                         | 31         |

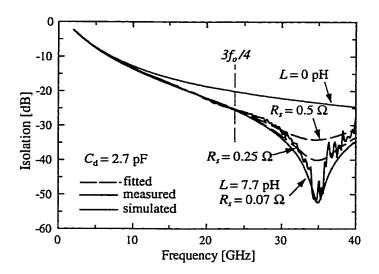

| 2.10  | Down-state measured and fitted isolation for a MEMS shunt switch, showing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | the effect of the inductance and resistance $(R_s)$ on the fit. $(L = 300 \ \mu\text{m},$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0 11  | $w = 80 \ \mu\text{m}, W = 100 \ \mu\text{m}, t_d = 1500 \ \text{Å.}) \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

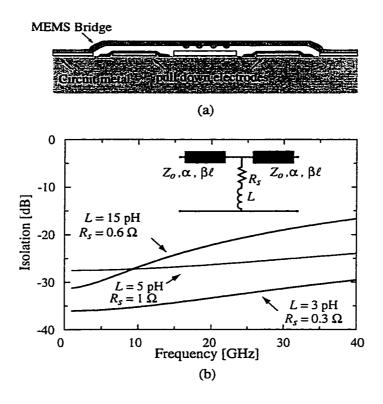

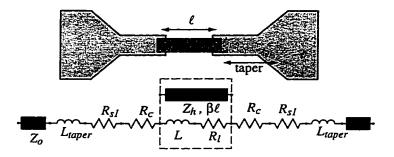

|       | Illustration of a MEMS inline shunt capacitive switch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

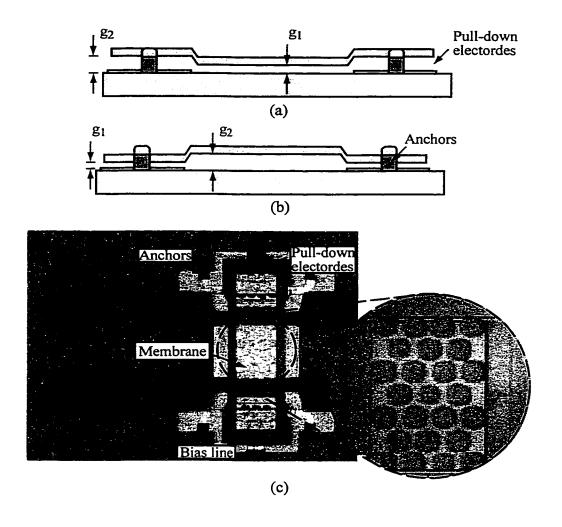

| 2.12  | A DC-contact MEMS shunt switch with two pulldown electrodes, and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0.1   | simulated isolation in the down-state position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

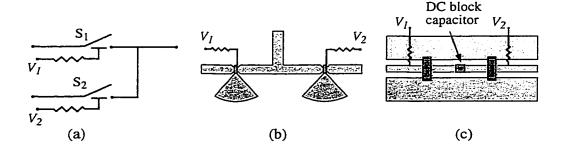

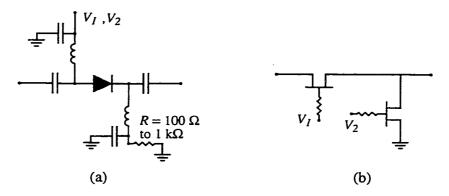

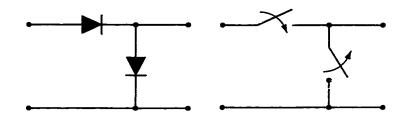

| 3.1   | Bias arrangement for (a) series switches, (b) microstrip capacitive switches, and (c) CPW capacitive switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.2   | Bias arrangement for (a) PIN diode, and (b) a transistor switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

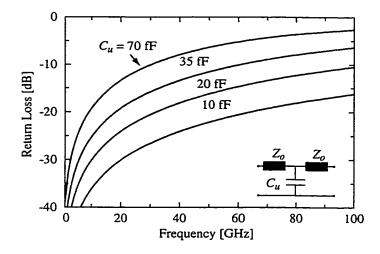

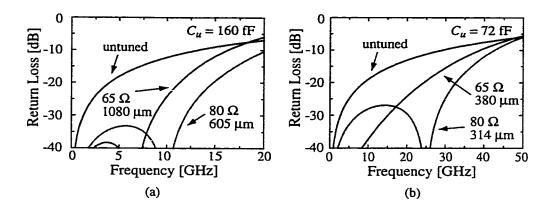

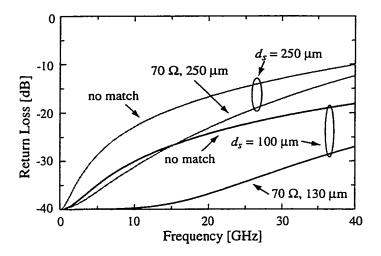

| 3.3   | Calculated reflection coefficient for different up-state bridge capacitances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

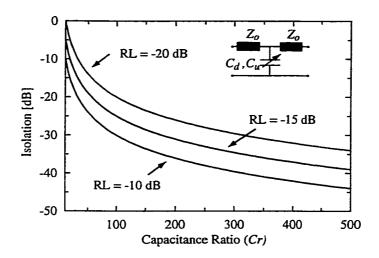

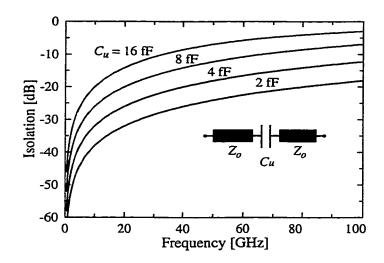

| 3.4   | Calculated isolation versus allowable off-state reflection coefficient and capacitive ratio for a CPW shunt MEMS switch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

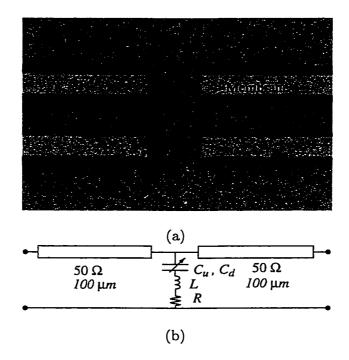

| 3.5   | Photomicrograph of a X/K-band standard shunt capacitive switch (a) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | equivalent model (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

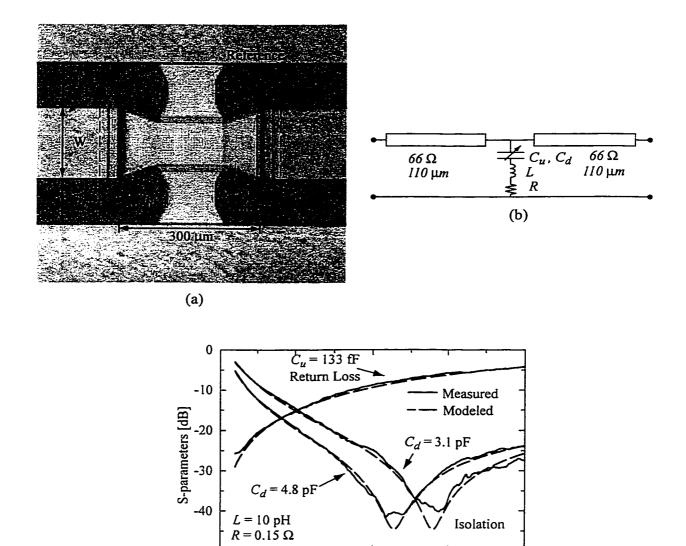

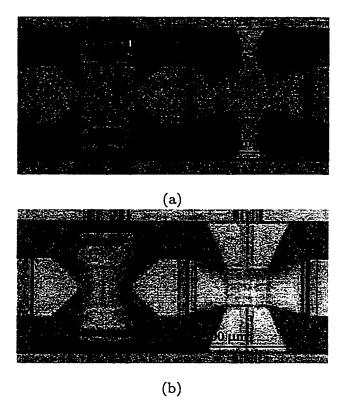

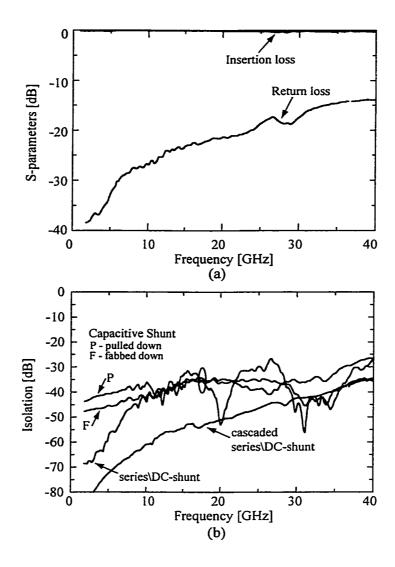

| 3.6   | Photomicrograph of a X/K-band inline shunt capacitive switch (a), equivalent model (b), and measured S-parameters of a X/K-band inline shunt capacitive MEMS switch with a pulled-down switch ( $C_d = 3.1$ pF) and a fabricated-down switch ( $C_d = 4.8$ pF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

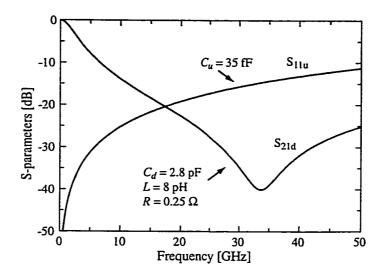

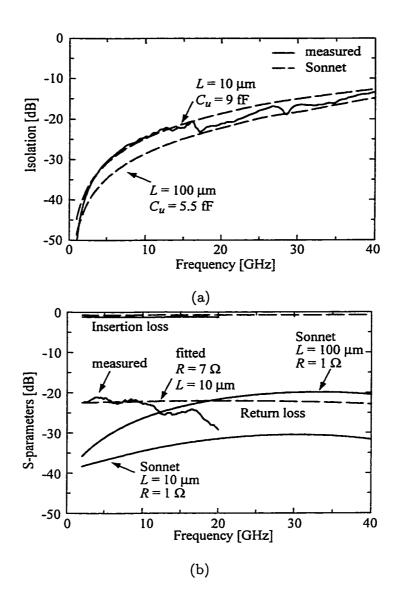

| 3.7   | Simulated S-parameters for a Ka-band CPW MEMS shunt switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

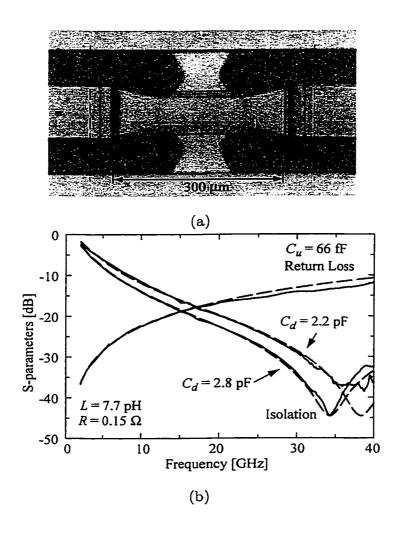

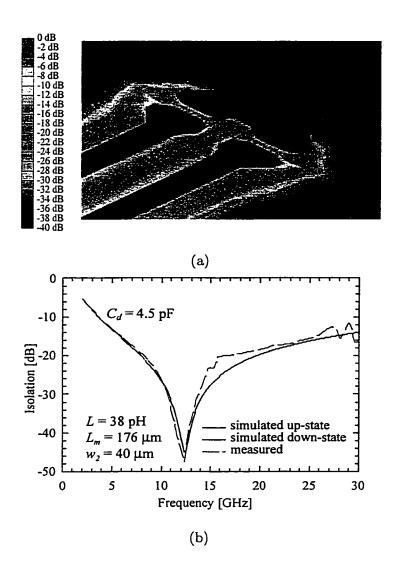

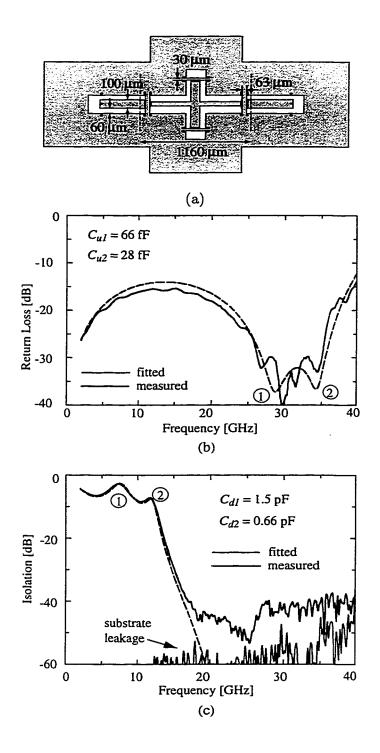

| 3.8   | Photomicrograph of a Ka/V-band inline shunt capacitive switch (a). Mea-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | sured (solid) and fitted (dashed) S-parameters of a Ka/V-band inline shunt capacitive MEMS switch (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

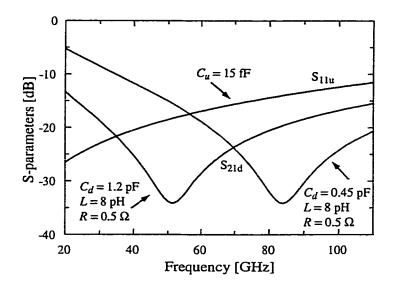

| 3.9   | Simulated S-parameters for a W-band CPW MEMS shunt switch with $C_d =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 1.2 pF and $C_d = 450$ fF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

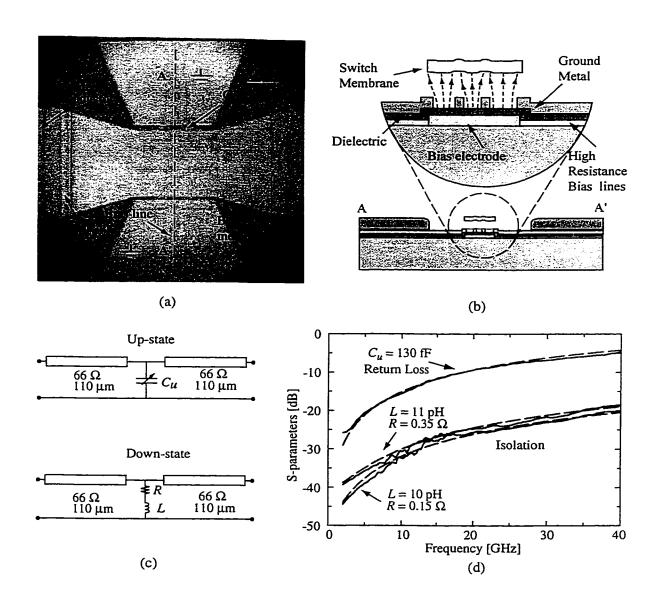

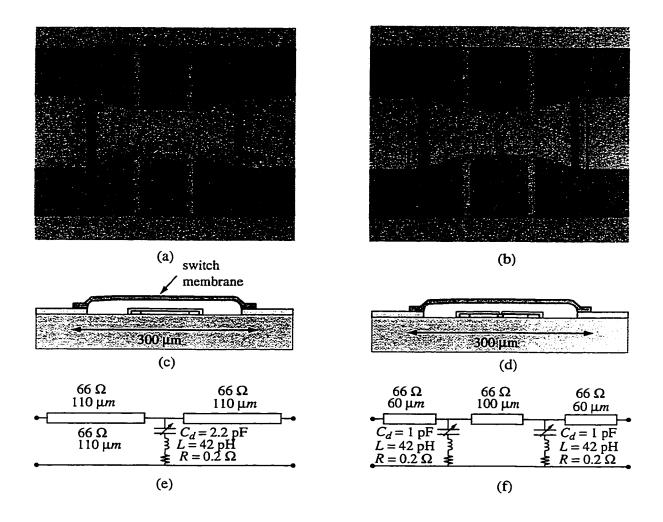

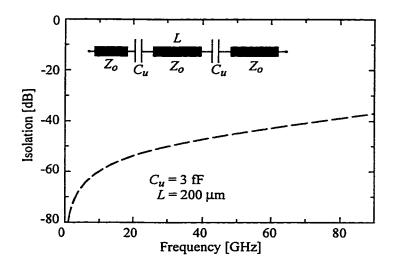

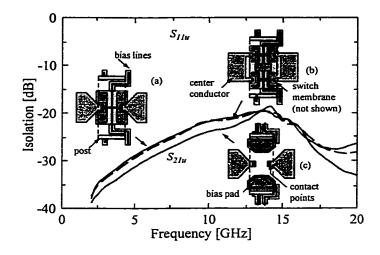

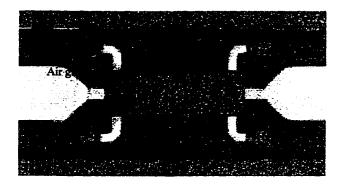

| 3.10  | Photomicrograph of a DC contact inline shunt MEMS switch (a) and an illustration of the DC-contact inline shunt MEMS switch (b). Equivalent circuit in the up-state and down-state (c) and measured (solid) and fitted (dashed) S-parameters of an inline shunt DC MEMS switch (d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

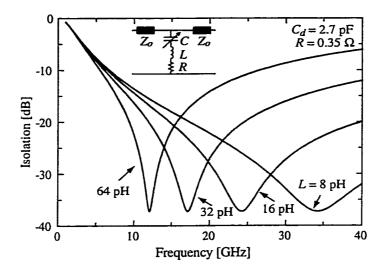

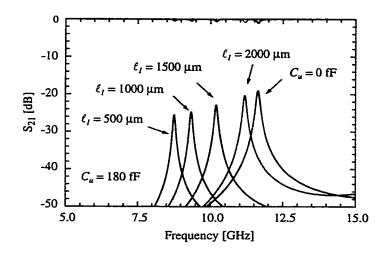

| 3.11  | Simulated isolation of a MEMS shunt switch with a down-state capacitance of 2.7 pF and various values of inductance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

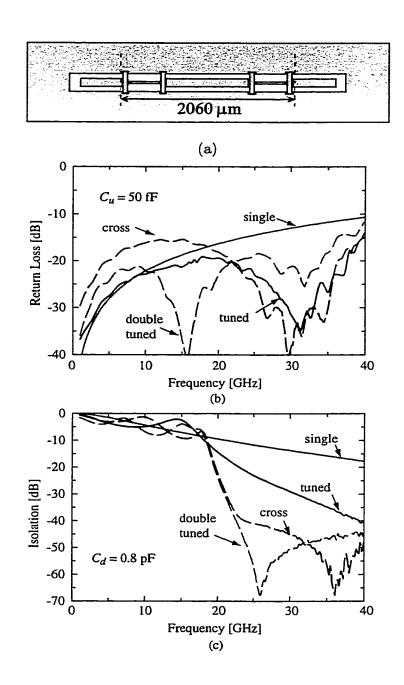

| 2 12  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

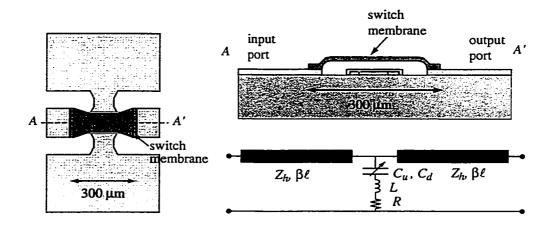

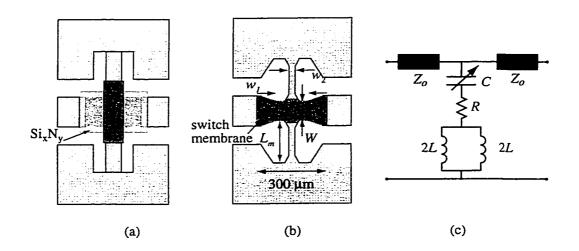

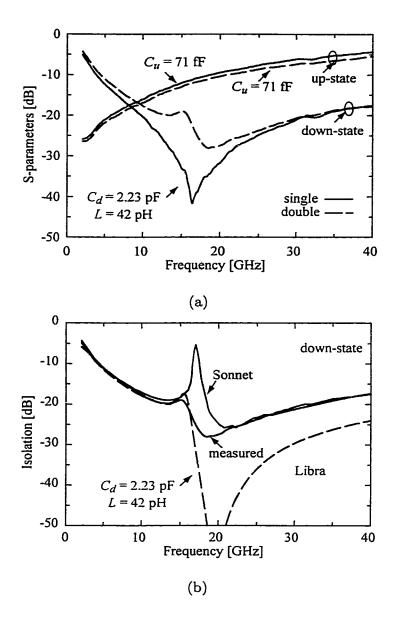

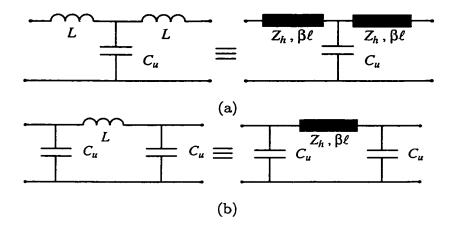

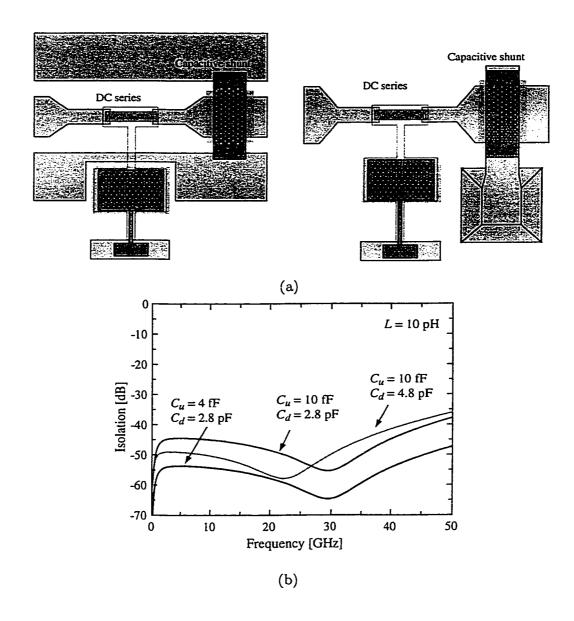

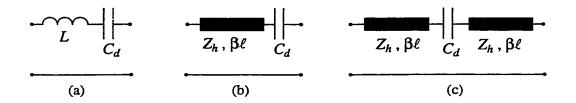

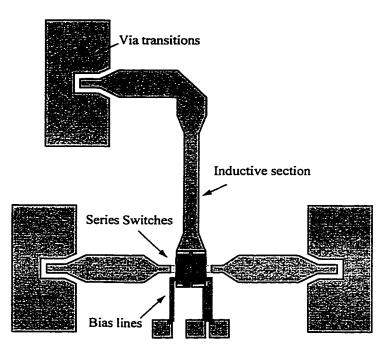

| 3.12  | Inductively resonant MEMS shunt switch implementations (a,b) and an equivalent circuit model (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

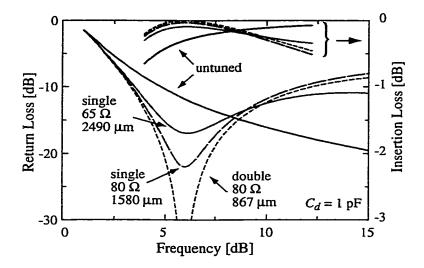

| 2 1 2 | alent circuit model (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

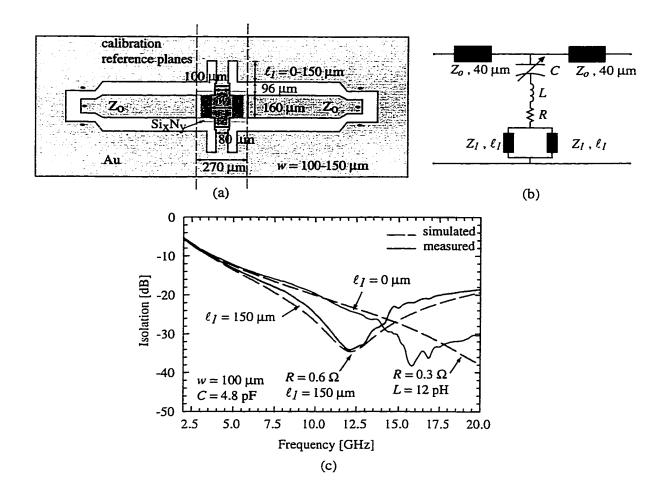

| 3.13  | figuration) and its equivalent circuit model (a,b), and simulated and measured isolation in the down-state position for MEMS shunt switches with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | $w = 100 \ \mu \text{m} \text{ and } \ell_1 = 0 \text{ and } 150 \ \mu \text{m} \text{ (c)} \dots \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

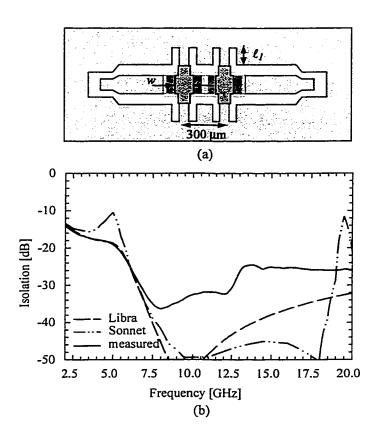

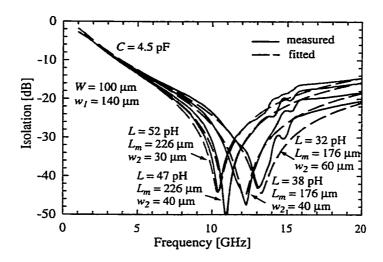

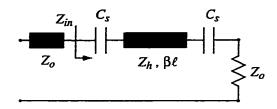

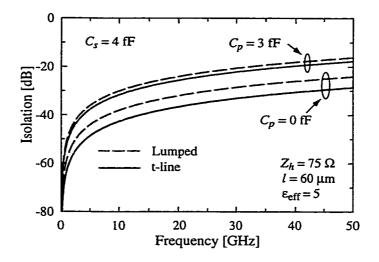

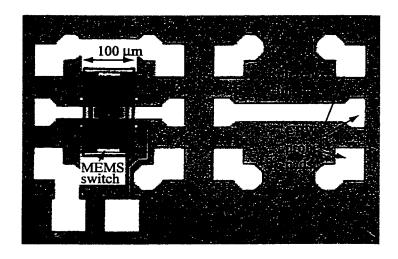

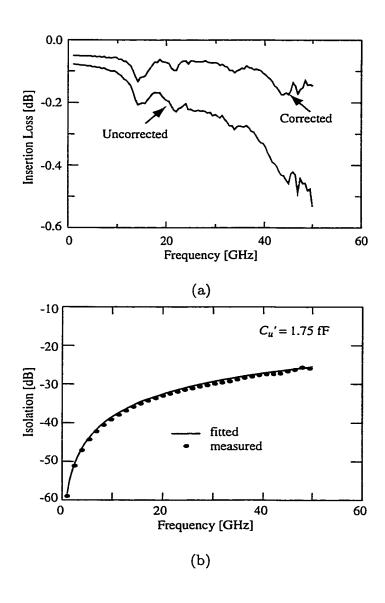

| 3.14  | Simulated and measured S-parameters for a double MEMS shunt switch with $w=150~\mu\mathrm{m},~\ell_1=150~\mu\mathrm{m},~\mathrm{and}~G/W/G=96/160/96~\mu\mathrm{m}$ . The equivalent circuit (Libra) and fullwave moment method (Sonnet) simulations predict higher isolation than the measurements indicate. This is due to the calibration of the contract of |