### Distributed MEMS Transmission Lines

$\mathbf{b}\mathbf{y}$

#### Nicolas Scott Barker

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 1999

#### Doctoral Committee:

Professor Gabriel M. Rebeiz, Chair Professor John W. Halloran Professor Linda P. B. Katehi Assistant Professor Clark T. C. Nguyen Associate Professor Kamal Sarabandi To my family.

### ACKNOWLEDGEMENTS

I would like to thank my advisor, Professor Gabriel Rebeiz, for allowing me to continue with this thesis topic, even after 6 months of nearly no progress. His encouragement and insight were extremely valuable throughout my graduate career. I would also like to thank Professors John Halloran, Linda Katehi, Clark Nguyen, and Kamal Sarabandi for taking the time to serve on my dissertation committee.

I would like to thank Frank Rucky, formerly at the Naval Surface Warfare Center, and Dr. Jim Harvey, at the Army Research Office, for their support of this research and of graduate education which is not always the most efficient means of conducting research.

This research would not have been possible without the support of numerous graduate students. I am indebted to former TICS students Dr. Thomas Budka, Dr. Stephen Robertson, Dr. Chen-Yu Chi and Professor Sanjay Raman for introducing me to microwave circuit fabrication, measurement, and tribal knowledge some of which I hope I have been able to pass on. I am deeply indebted to Dr. Andrew Brown for introducing me to an alternative fabrication process which led to a breakthrough in my research; in addition to his constant support and friendship. I also enjoyed the friendship of former TICS students Dr. Rashaunda Henderson, Professor John Papapolymerou, and Dr. Gildas Gauthier. I would like to thank current TICS students Thomas Ellis, Sergio Pacheco, J. D. Shumpert, Leo DiDomenico, and Katherine Herrick for their invaluable support and friendship. I have also enjoyed getting to know the newer TICS students Jeremy Muldavin, Joe Hayden, Guan-Leng Tan, Lee Harle, Tom Schwartz, and Bill Chappell.

There are many many more people that helped along the way in numerous ways but there are a few who are essential for maintaining the day to day operation of the lab. Thus, I would like to express my sincere thanks to the Radiation Laboratory staff, specifically Carol Truszkowski and Sharon Ryder, as well as the Solid State Electronics Laboratory staff.

Finally, I would like to thank my family. My parents, Bill Barker and Dorothy Barker, encouraged me at every step and never doubted my ability to complete the task I had set for myself. All of my brothers and sisters provided much needed support even though they could not be right here with me. In addition, my church family at First United Methodist Church was a tremendous support week in and week out throughout my entire stay in Ann Arbor. But most importantly, I would like to express my deepest gratitude for my wife Susan who provided understanding and loving support when I needed it most.

# TABLE OF CONTENTS

| DEDICA  | ΓΙΟΝ                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNO   | VLEDGEMENTS iii                                                                                                                                                                                                                                                                                                                                                                      |

| LIST OF | TABLES vii                                                                                                                                                                                                                                                                                                                                                                           |

| LIST OF | FIGURES viii                                                                                                                                                                                                                                                                                                                                                                         |

| LIST OF | APPENDICES xiv                                                                                                                                                                                                                                                                                                                                                                       |

| CHAPT   | ers                                                                                                                                                                                                                                                                                                                                                                                  |

| 1 ]     | ntroduction                                                                                                                                                                                                                                                                                                                                                                          |

|         | Mechanical Properties of Fixed-Fixed Beams       7         2.1 Spring Constant       7         2.2 Electrostatic Actuation       14         2.3 Stabilization of Electrostatically Actuated Bridges       19         2.4 Frequency Response       23         2.5 Brownian Noise Analysis       24                                                                                    |

| 3       | Distributed MEMS Transmission Lines       27         3.1 Fabrication of the DMTL       28         3.2 Analytic Modeling of Distributed Lines       30         3.3 Loss on Distributed Lines       33         3.4 DMTL Circuit Modeling       36         3.5 DMTL Measurements       37         3.6 Comparison of Analytic and Circuit Model       45         3.7 Conclusion       47 |

| 4       | Distributed MEMS Transmission Line Phase Shifters       49         4.1 Design       50         4.2 Optimization       55         4.2.1 Theory       55         4.2.2 Experiment       64         4.3 W-Band DMTL Phase Shifter       69         4.4 Stabilized DMTL Phase Shifter       78                                                                                           |

| 5     | Applie | ations of Distributed MEMS Transmission Lines 81 |

|-------|--------|--------------------------------------------------|

|       | 5.1    | Reflective Switches                              |

|       |        | 5.1.1 Design and Measurements                    |

|       |        | 5.1.2 Switching Speed                            |

|       | 5.2    | Phase Modulators                                 |

|       | 5.3    | Phase Verniers                                   |

|       | 5.4    | Power Handling Measurement                       |

| 6     | Conch  | sions and Future Work                            |

|       | 6.1    | Very Low Loss Phase Shifters                     |

|       | 6.2    | Wideband Switches                                |

|       | 6.3    | Modulators                                       |

|       | 6.4    | Development of High-Q Varactors                  |

| APPE  | NDICE  | es                                               |

| BIBLI | OGRA   | PHY                                              |

# LIST OF TABLES

| <b>Fable</b> |                                                                                  |    |

|--------------|----------------------------------------------------------------------------------|----|

| 2.1          | Difficusions of bridges used in 1 Sare 2                                         | 15 |

| 2.2          | Quality factors for bridges in Figure 2.16                                       | 24 |

| 2.3          | Low-frequency rms Brownian-noise position values for the bridges used in         |    |

|              | Figure 2.16 in Å/ $\sqrt{\text{Hz}}$                                             | 26 |

| 3.1          | Bragg Frequency Calculations from (3.8) and (3.12)                               | 33 |

| 3.2          | Fitted Model Parameters for DMTL with $w/s = 30/306 \ \mu \text{m}$              | 40 |

| 3.3          | Fitted Model Parameters for DMTL with $w/s = 60/640~\mu\mathrm{m}$               | 43 |

| 3.4          | DMTL parameters for Figure 3.14                                                  | 47 |

| 3.5          | DMTL parameters for Figure 3.15                                                  | 47 |

| 4.1          | Modeling parameters for DMTL in Figure 4.1                                       | 51 |

| 4.2          | Specifications for examples in Figures 4.3-4.7                                   | 55 |

| 4.3          | Specifications of the DMTLs used to verify the optimization procedure            | 64 |

| 4.4          | Dimensions of the DMTLs used to verify the optimization. The Bragg fre-          |    |

|              | quency is calculated using $L_b = 20$ pH. $R_b = 0.15 \Omega$ at 30 GHz          | 64 |

| 4.5          | Circuit model parameters for the optimal DMTL (W = 100 $\mu$ m)                  | 60 |

| 4.6          | Calculated design of an optimized W-band DMTL phase shifter on quartz.           | 74 |

| 4.7          | Dimensions for the optimized W-band DMTL phase shifter                           | 74 |

| 4.8          | Circuit model parameters for the W-band DMTL phase shifter                       | 74 |

| 4.9          | Circuit model parameters for the optimal DMTL with integrated capacitors.        | 80 |

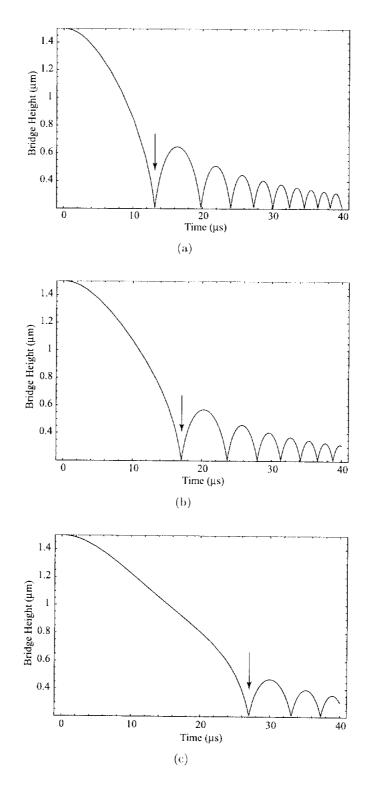

| 5.1          | Parameters of the gold bridge used in the calculation of Figure 5.9              | 91 |

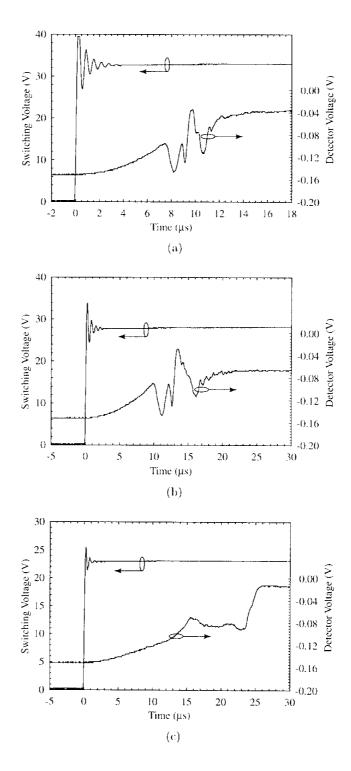

| 5.2          | Measured and modeled switching speed in $\mu$ s ( $Q = 2.3$ )                    | 94 |

| 5.3          | Calculated switching speeds, in $\mu$ s, from the numerical solution for varying |    |

|              | Q values.                                                                        | 94 |

| 5.4          | Measured, theoretical, and modeled RF spectrum of the BPSK signal in dBc.        | 99 |

| 5.5          | Parameters of the gold bridge used in the calculation of Figure 5.15             | 99 |

| 5.6          | I distinction of the Sold bridge that                                            | 10 |

| D.1          | PECVD $Si_xN_y$ recipe [42]                                                      | 12 |

| D.2          | PECVD $Si_xN_y$ reactive ion etching (RIE) recipe                                | 12 |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                |    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

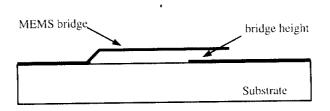

| 1.1    | Cantilever MEMS bridge in a series configuration along a microstrip or CPW                                                                                                     | ~  |

|        | transmission line                                                                                                                                                              | 2  |

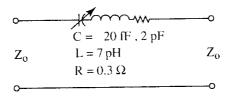

| 1.2    | Circuit model for a series capacitive MEMS switch with the capacitance                                                                                                         | 0  |

|        | switching from 20 fF to 2 pF                                                                                                                                                   | 2  |

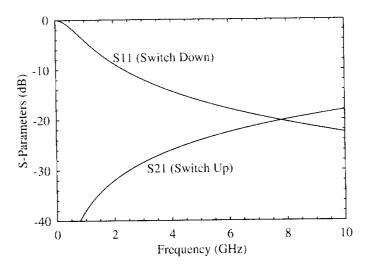

| 1.3    | Circuit simulation of series switch using the model in Figure 1.2                                                                                                              | 2  |

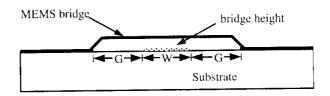

| 1.4    | Fixed-fixed beam MEMS bridge in shunt configuration over a CPW trans-                                                                                                          | 3  |

|        | mission line                                                                                                                                                                   | J  |

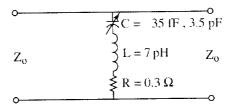

| 1.5    | Circuit model for a shunt capacitive MEMS switch with the capacitance                                                                                                          | 3  |

|        | switching from 35 fF to 3.5 pF                                                                                                                                                 | 3  |

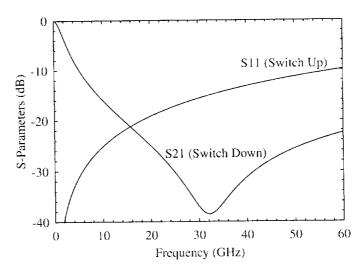

| 1.6    | Circuit simulation of a shunt switch using the model in Figure 1.5                                                                                                             | 5  |

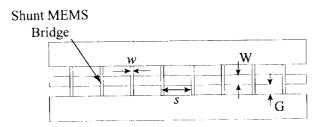

| 1.7    | Top view of a CPW line periodically loaded by shunt MEMS bridges                                                                                                               | 7  |

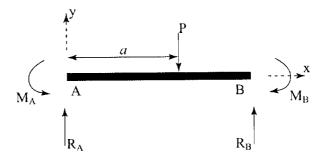

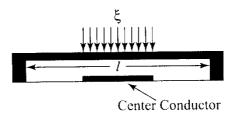

| 2.1    | Fixed-fixed beam with concentrated vertical load P                                                                                                                             | '  |

| 2.2    | Fixed-fixed beam over a CPW line with the force, $P = \xi l/3$ , evenly dis-                                                                                                   | 9  |

|        | tributed above the CPW center conductor                                                                                                                                        | 10 |

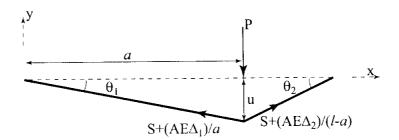

| 2.3    | Deam modeled as a succeeded with with confession                                                                                                                               | 10 |

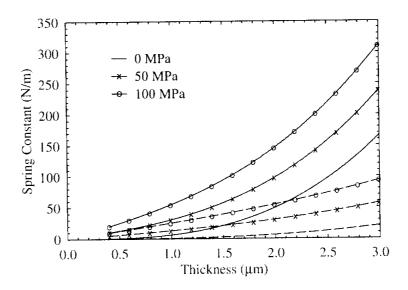

| 2.4    | Spring constant of a gold bridge (E = 80 GPa, $\nu = 0.42$ ) with lengths of                                                                                                   |    |

|        | $200 \ \mu \text{m}$ (-) and $400 \ \mu \text{m}$ (-). For each bridge length the spring constant is evaluated for biaxial residual stresses of 0, 50, and 100 MPa. The spring |    |

|        | constant scales linearly with the bridge width which is held constant at 35 $\mu$ m.                                                                                           | 12 |

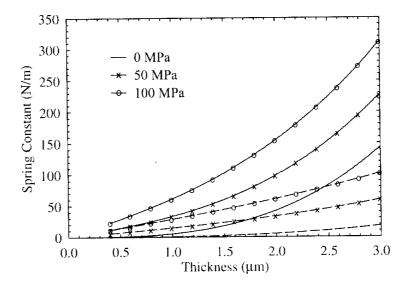

| 2.5    | Spring constant of an aluminum bridge (E = 69 GPa, $\nu$ = 0.33) with lengths                                                                                                  |    |

| 2.0    | of 200 $\mu$ m () and 400 $\mu$ m (). For each bridge length the spring constant                                                                                               |    |

|        | is evaluated for biaxial residual stresses of 0, 50, and 100 MPa. The spring                                                                                                   |    |

|        | constant scales linearly with the bridge width which is held constant at 35 $\mu$ m.                                                                                           | 12 |

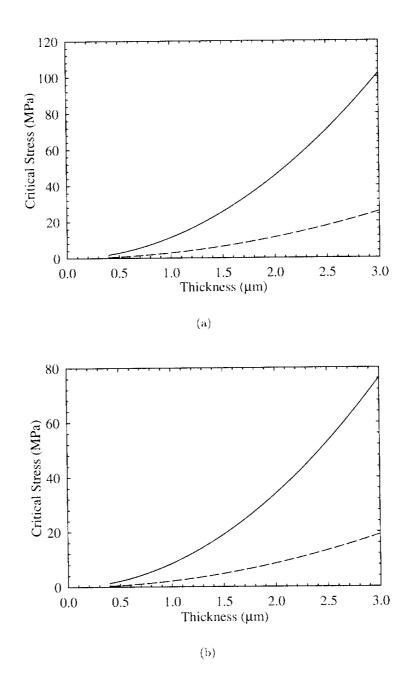

| 2.6    | Critical stress of a (a) gold (E = 80 GPa, $\nu$ = 0.42) and (b) aluminum                                                                                                      |    |

|        | (E = 69 GPa, $\nu = 0.33$ ) bridge vs. thickness for 200 $\mu m$ (—) and 400 $\mu m$ (–                                                                                        |    |

|        | ) long bridges                                                                                                                                                                 | 13 |

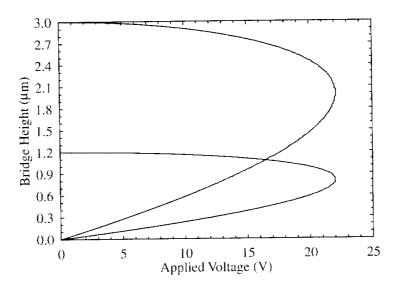

| 2.7    | Bridge height versus applied voltage with a zero-bias bridge height of 1.2 $\mu m$                                                                                             |    |

|        | and 3 $\mu$ m. The bridge parameters, given in Table 2.1, are chosen to result in                                                                                              |    |

|        | a pull-down voltage of 22 V                                                                                                                                                    | 14 |

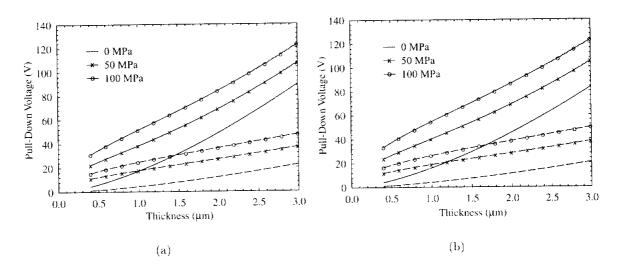

| 2.8  | Pull-down voltage of a (a) gold (E = 80 GPa, $\nu = 0.42$ ) and (b) aluminum (E = 69 MPa, $\nu = 0.33$ ) bridge vs. bridge thickness for 200 $\mu$ m (—) and 400 $\mu$ m (—) long bridges. For each bridge length the pull-down voltage is calculated for biaxial residual stresses of 0, 50, and 100 MPa. The pull-down      |          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | voltage depends on the bridge height as $g_o^{3/2}$ and $g_o$ is 1.5 $\mu$ m                                                                                                                                                                                                                                                  | 17       |

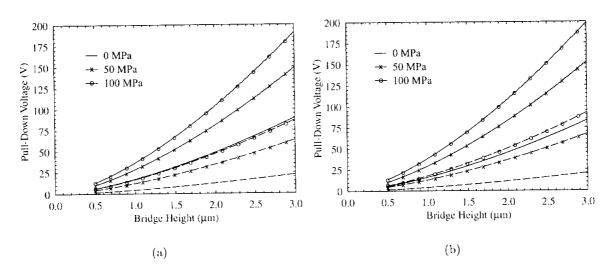

| 2.9  | Pull-down voltage of a (a) gold (E = 80 GPa, $\nu = 0.42$ ) and (b) aluminum (E = 69 MPa, $\nu = 0.33$ ) bridge vs. bridge height for 200 $\mu$ m (—) and 400 $\mu$ m (—) long bridges. For each bridge length the pull-down voltage is calculated for biaxial residual stresses of 0, 50, and 100 MPa. The pull-down voltage |          |

|      | depends on the bridge height as $g_o^{3/2}$ and $g_o$ is 1.5 $\mu$ m                                                                                                                                                                                                                                                          | 17       |

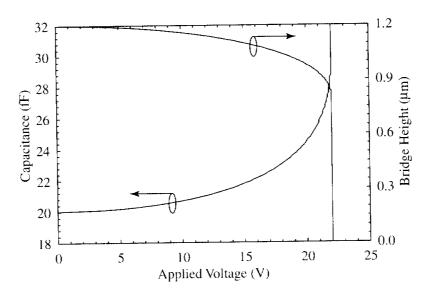

| 2.10 | Variation of bridge capacitance and gap height with applied voltage. The                                                                                                                                                                                                                                                      |          |

|      | bridge parameters have been adjusted to result in a pull-down voltage of 22 V, a zero-bias bridge capacitance of 20 fF, and a zero-bias height of 1.2 $\mu$ m.                                                                                                                                                                | 18       |

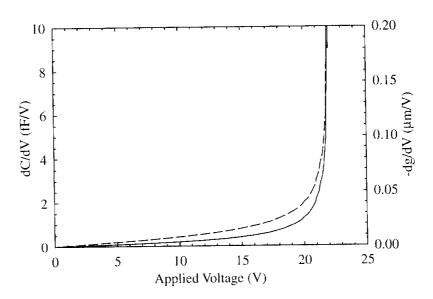

| 2.11 | Derivative of the bridge capacitance ( ) and bridge height (), with respect                                                                                                                                                                                                                                                   |          |

|      | to the applied voltage, vs. the applied voltage. The bridge parameters have been adjusted to result in a pull-down voltage of 22 V                                                                                                                                                                                            | 18       |

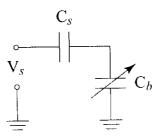

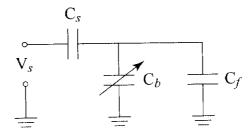

| 9.19 | Stabilization of an electrostatically actuated MEMS bridge through the use                                                                                                                                                                                                                                                    |          |

| 2.12 | of a series feedback capacitor                                                                                                                                                                                                                                                                                                | 19       |

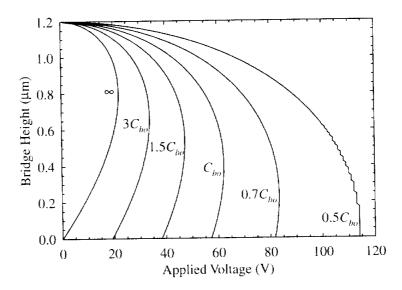

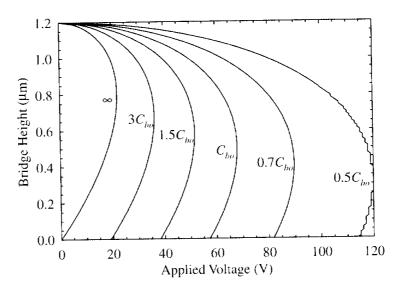

| 2 13 | Plot of change in bridge height versus applied voltage as the series feedback                                                                                                                                                                                                                                                 |          |

|      | capacitor is varied from $0.5C_{bo}$ to $\infty$ . The zero-bias bridge height is 1.2 $\mu$ m.                                                                                                                                                                                                                                | 20       |

| 2.14 | Stabilization of an electrostatically actuated MEMS bridge, in the presence of                                                                                                                                                                                                                                                |          |

|      | significant fringing capacitance, through the use of a series feedback capacitor.                                                                                                                                                                                                                                             | 21       |

| 2.15 | Plot of the change in bridge height versus applied voltage as the series feed-                                                                                                                                                                                                                                                |          |

|      | back capacitor is varied from $0.5C_{bo}$ to $\infty$ with a fringing capacitance of                                                                                                                                                                                                                                          | 22       |

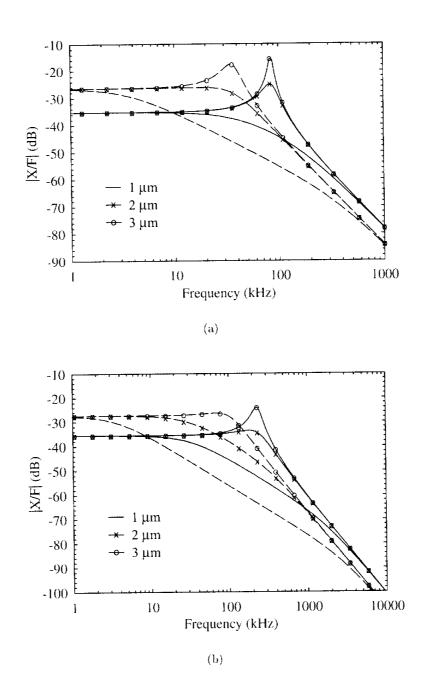

| 0.10 | $C_f = C_{bo}/3$ . The zero-bias bridge height is 1.2 $\mu$ m Frequency response of a (a) gold (E = 80 GPa, $\nu = 0.42$ , $\rho = 19320$ kg/m <sup>3</sup> )                                                                                                                                                                 |          |

| 2.10 | and (b) aluminum (E = 69 MPa, $\nu$ = 0.33, $\rho$ = 2700 kg/m <sup>3</sup> ) bridge for                                                                                                                                                                                                                                      |          |

|      | 200 $\mu$ m () and 400 $\mu$ m () long bridges over a CPW line with W = $l/3$ .                                                                                                                                                                                                                                               |          |

|      | For each bridge length the response is calculated for bridge heights of 1, 2,                                                                                                                                                                                                                                                 |          |

|      | and 3 $\mu$ m. The width is 35 $\mu$ m, the thickness is 1.5 $\mu$ m, and the residual                                                                                                                                                                                                                                        | ۵.       |

|      | stress is 50 MPa                                                                                                                                                                                                                                                                                                              | 25       |

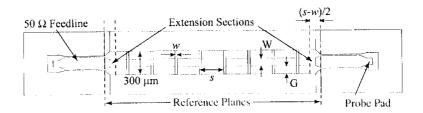

| 3.1  | Layout of a DMTL constructed of a CPW line with center conductor width                                                                                                                                                                                                                                                        |          |

|      | W and total CPW width W+2G, and MEMS bridges with width w and                                                                                                                                                                                                                                                                 |          |

|      | spacing s. The DMTL is connected to 50 $\Omega$ feedlines and probe pads for testing                                                                                                                                                                                                                                          | 28       |

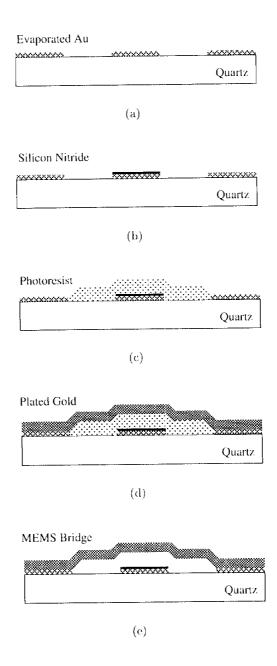

| 3.2  | Details of the fabrication process for the MEMS bridges. The illustrations                                                                                                                                                                                                                                                    |          |

| 0.2  | show a cross-sectional view of a DMTL                                                                                                                                                                                                                                                                                         | 29       |

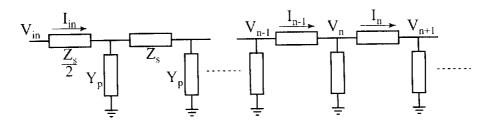

| 3.3  | General model for a periodically loaded transmission line with series impedance                                                                                                                                                                                                                                               |          |

|      | $Z_s$ and shunt admittance $Y_p$                                                                                                                                                                                                                                                                                              | 30       |

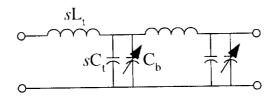

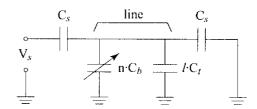

| 3.4  | Lumped element transmission-line model of the DMTL assuming the MEMS                                                                                                                                                                                                                                                          |          |

|      | bridge can be represented by a capacitor $C_b$ . $L_t$ and $C_t$ are the per unit length                                                                                                                                                                                                                                      |          |

|      | inductance and capacitance, respectively, of the unloaded transmission line, and $s$ is the spacing between the MEMS bridges.                                                                                                                                                                                                 | 32       |

|      | and s is the spacing between the MEMIS bridges                                                                                                                                                                                                                                                                                | <b>-</b> |

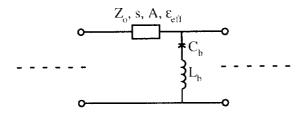

| 3.5  | Circuit model used for a section in the DMTL simulation where $Z_o$ is the unloaded line impedance, $s$ is the periodic spacing of the MEMS bridges, A is the attenuation in dB/cm of the unloaded line, $\epsilon_{eff}$ is the effective dielectric constant of the unloaded line, $C_b$ is the MEMS bridge capacitance, and $L_b$ is | 117 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

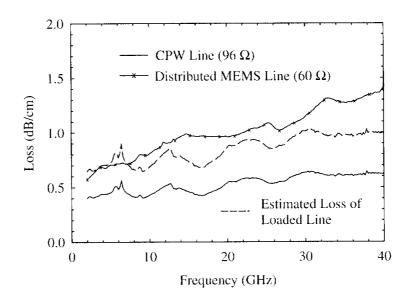

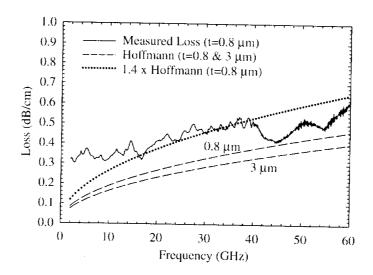

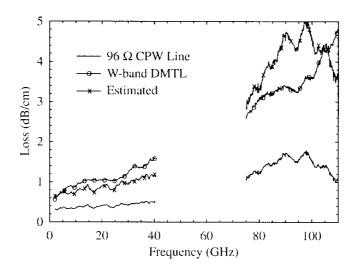

| 3.6  | the bridge inductance                                                                                                                                                                                                                                                                                                                   | 37  |

|      | loss by multiplying it by a factor of $96/60 = 1.6.$                                                                                                                                                                                                                                                                                    | 38  |

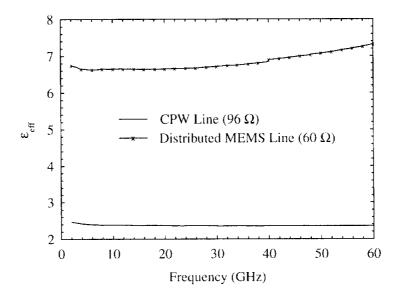

| 3.7  | Measured effective dielectric constant of a 96 $\Omega$ CPW line and a 61 $\Omega$ DMTL.                                                                                                                                                                                                                                                | 38  |

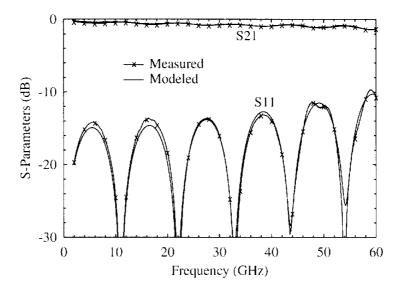

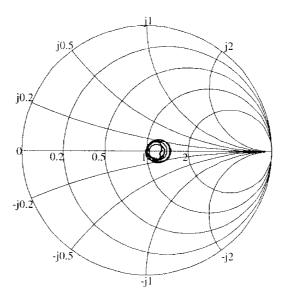

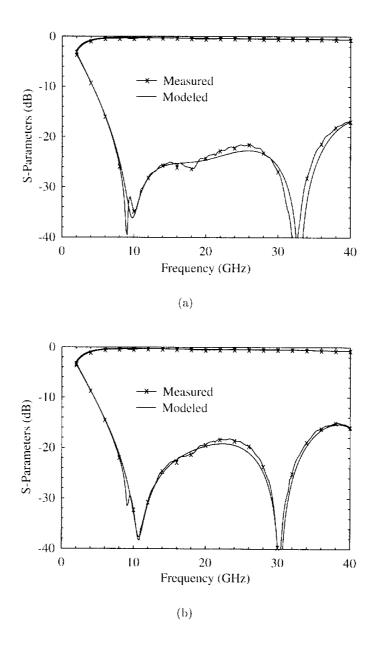

| 3.8  | Measured and simulated S-parameters of a DMTL with 16 30- $\mu$ m wide MEMS                                                                                                                                                                                                                                                             | 40  |

|      | bridges spaced at 306 $\mu m$ (total length = 5.2 mm, $Z=61~\Omega, f_B=129~\mathrm{GHz}$ ).                                                                                                                                                                                                                                            | 40  |

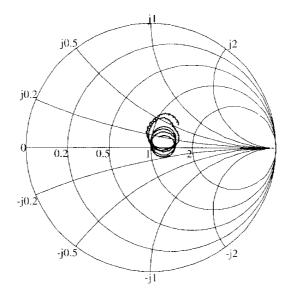

| 3.9  | Measured S11 from 0-60 GHz for a DMTL with 16 30- $\mu$ m wide bridges spaced                                                                                                                                                                                                                                                           | 41  |

|      | at 306 $\mu$ m.                                                                                                                                                                                                                                                                                                                         | 41  |

| 3.10 | Measured S11 from 0-60 GHz for a DMTL with 16 30-μm wide bridges spaced                                                                                                                                                                                                                                                                 | 41  |

|      | at 306 $\mu m$ with the 138 $\mu m$ long high-impedance lines de-embedded Measured and simulated S-parameters of a DMTL with 16 60- $\mu m$ wide MEMS                                                                                                                                                                                   | -11 |

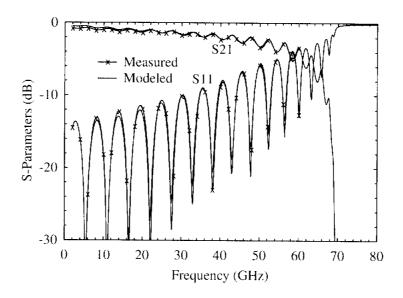

| 3.11 | Measured and simulated 5-parameters of a DW112 with 16 60- $\mu$ m with MEMS bridges spaced at 640 $\mu$ m (total length = 10.8 mm, $Z = 62~\Omega$ , $f_B = 62~\mathrm{GHz}$ ).                                                                                                                                                        | 43  |

| 9.10 | Measured S11 from 0-60 GHz for a DMTL with 16 60- $\mu$ m wide bridges spaced                                                                                                                                                                                                                                                           |     |

| 3.12 | at 640 $\mu$ m                                                                                                                                                                                                                                                                                                                          | 44  |

| 3.13 | Measured S11 from 0-60 GHz for a DMTL with 16-60 $\mu$ m wide bridges spaced                                                                                                                                                                                                                                                            |     |

| 0,10 | at 640 $\mu$ m with the 290 $\mu$ m high impedance lines de-embedded                                                                                                                                                                                                                                                                    | 44  |

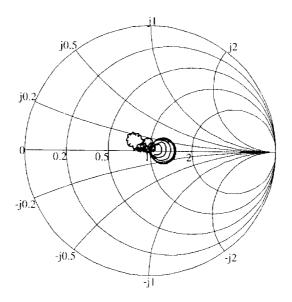

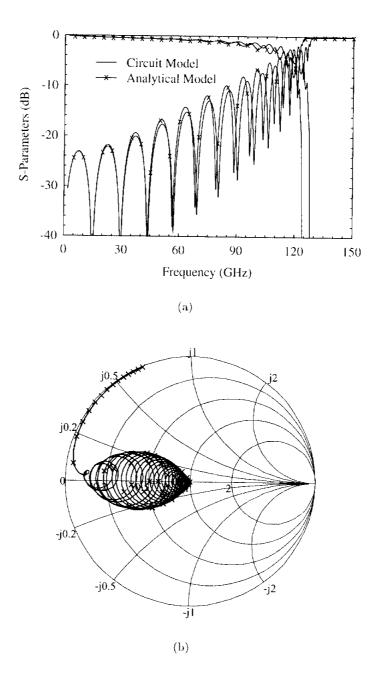

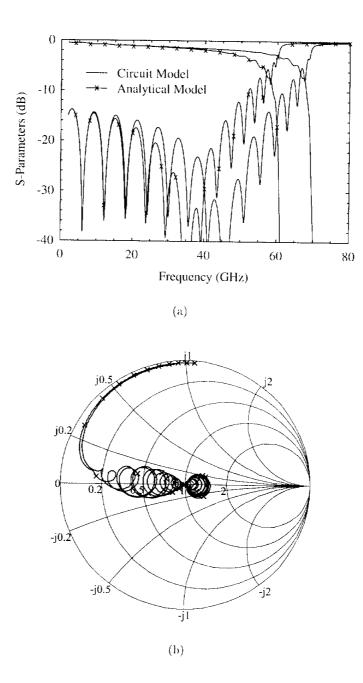

| 3.14 | Comparison between the circuit model and analytical model for the DMTL                                                                                                                                                                                                                                                                  |     |

|      | with parameters listed in Table 3.4                                                                                                                                                                                                                                                                                                     | 46  |

| 3.15 | Comparison between the circuit model and analytical model for the DMTL                                                                                                                                                                                                                                                                  |     |

|      | with parameters listed in Table 3.5                                                                                                                                                                                                                                                                                                     | 48  |

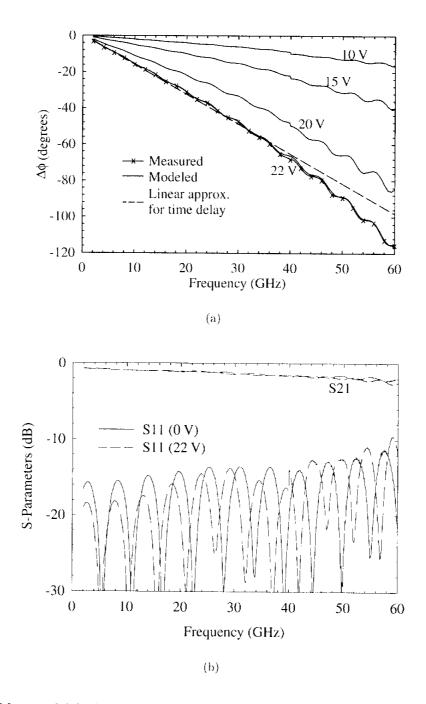

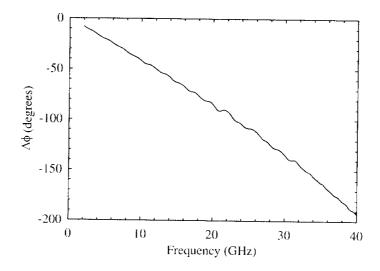

| 4.1  | Measured (a) phase shift and (b) S-parameters for a DMTL with 32 30- $\mu$ m-                                                                                                                                                                                                                                                           |     |

|      | wide bridges spaced at 306 $\mu$ m (total length = 10.1 mm) for varying bias                                                                                                                                                                                                                                                            |     |

|      | voltage. The phase shift at 22 V is modeled with the circuit parameters                                                                                                                                                                                                                                                                 | 52  |

| 4.0  | given in Table 4.1                                                                                                                                                                                                                                                                                                                      | 02  |

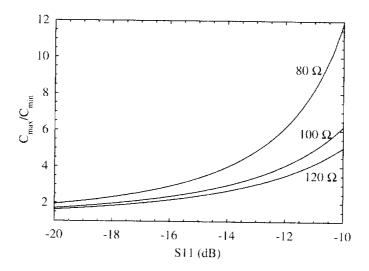

| 4.2  | impedances of 80, 100, and 120 $\Omega$                                                                                                                                                                                                                                                                                                 | 54  |

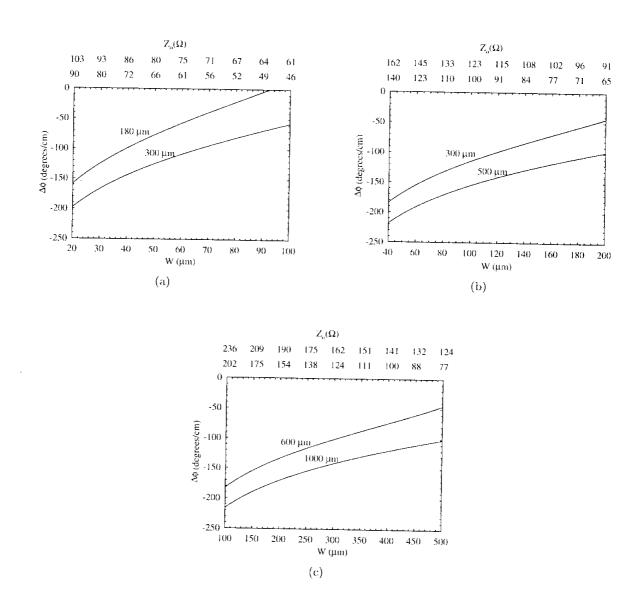

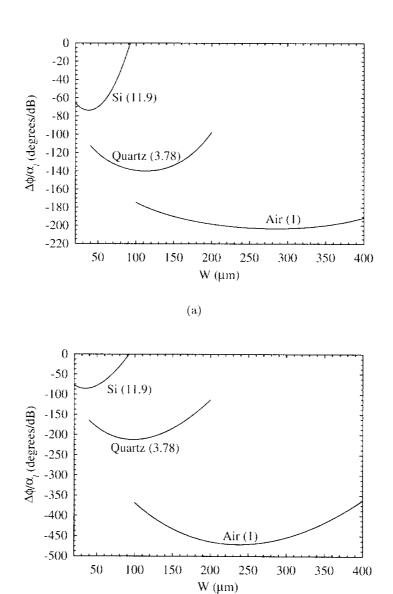

| 4.3  | Calculated phase shift per centimeter vs. the CPW center conductor width                                                                                                                                                                                                                                                                |     |

| 4.0  | at 40 GHz for (a) silicon, (b) quartz, and (c) air with a capacitance ratio                                                                                                                                                                                                                                                             |     |

|      | of $C_r = 1.2$ . The total CPW width is $\lambda_d/8$ and $\lambda_d/5$ , at 60 GHz, for each                                                                                                                                                                                                                                           |     |

|      | substrate, and the Bragg frequency is set to 120 GHz. The impedance for                                                                                                                                                                                                                                                                 |     |

|      | the corresponding center conductor width is given at the top of each plot                                                                                                                                                                                                                                                               | 57  |

| 4.4  | Measured and calculated loss vs. frequency for a 300 $\mu$ m total width unloaded                                                                                                                                                                                                                                                       | ro  |

|      | CPW line on quartz with a 100 $\mu$ m wide center conductor ( $Z_o = 100 \Omega$ )                                                                                                                                                                                                                                                      | 58  |

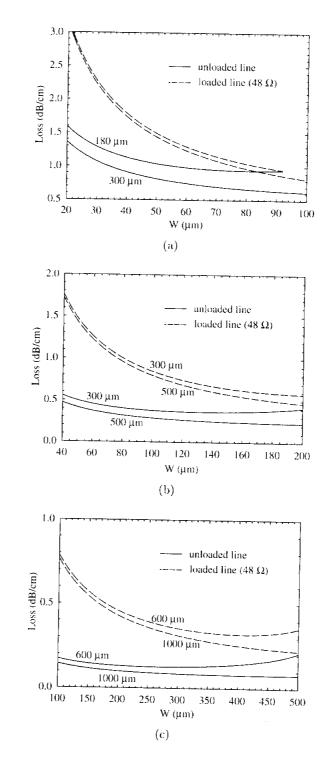

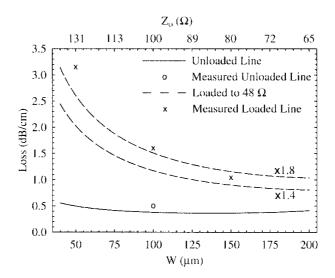

| 4.5  | Calculated loss for the unloaded and loaded transmission lines at 40 GHz                                                                                                                                                                                                                                                                |     |

|      | vs. CPW center conductor width for (a) silicon, (b) quartz, and (c) air substrates. The total CPW width is $\lambda_d/8$ and $\lambda_d/5$ , at 60 GHz, for each                                                                                                                                                                        |     |

|      | substrates. The total Gr w width is $\lambda_{d/3}$ and $\lambda_{d/3}$ , at 60 GHz, for each substrate, and the Bragg frequency is set to 120 GHz                                                                                                                                                                                      | 59  |

|      | attraction, and and prope modules and an analysis and                                                                                                                                                                                                                                                                                   |     |

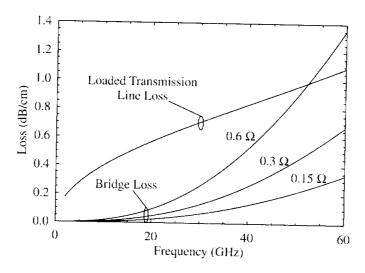

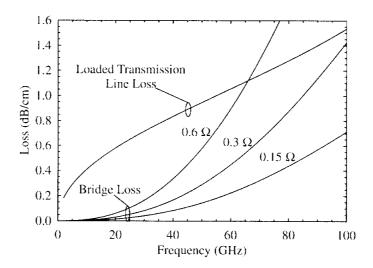

|      | Loaded transmission line loss and loss due to bridge resistance vs. frequency. The line loss is calculated from Hoffmann's equation for a 300 $\mu$ m total width CPW line with a 100 $\mu$ m width center conductor. The Bragg frequency is 120 GHz, the bridge spacing is 197 $\mu$ m and the bridge capacitance is 34.6 fF. | 51 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

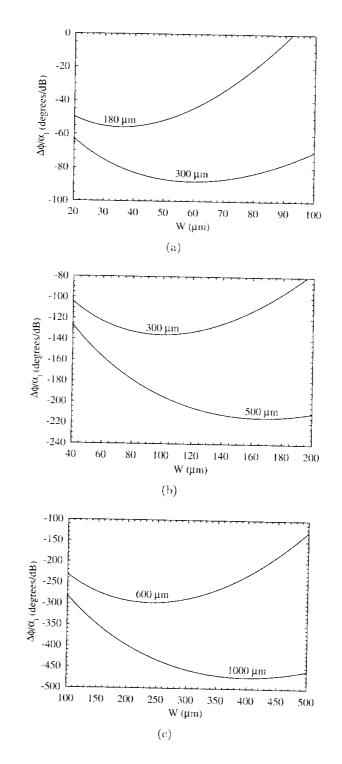

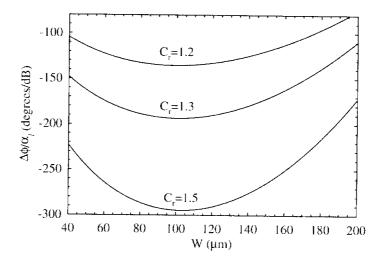

| 4.7  | Calculated phase shift per dB loss at 40 GHz vs. CPW center conductor width for (a) silicon, (b) quartz, and (c) air substrates with a capacitance ratio of $C_r = 1.2$ . The total CPW width is $\lambda_d/8$ and $\lambda_d/5$ for each substrate                                                                            |    |

|      | and the Bragg frequency is set to 120 GHz                                                                                                                                                                                                                                                                                      | 52 |

| 4.8  | Calculated phase shift per dB loss at 40 GHz versus center conductor width for a 300 $\mu m$ total width CPW line on quartz. The capacitance ratio is varied from 1.2 to 1.5 with a loaded impedance of 48 $\Omega$ and a Bragg frequency of                                                                                   | 29 |

| 4.9  | 120 GHz                                                                                                                                                                                                                                                                                                                        | 53 |

|      | widths are included for reference                                                                                                                                                                                                                                                                                              | 65 |

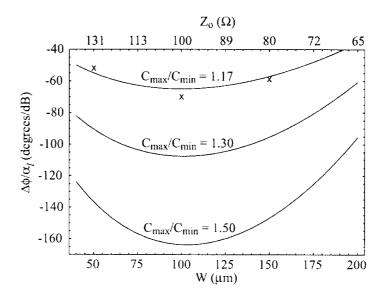

| 4.10 | Calculated phase shift per dB loss at 40 GHz with capacitance ratios of 1.17, 1.3, and 1.5. Measured data points (x) are included for CPW center conductor widths of 50, 100, and 150 $\mu$ m.                                                                                                                                 | 65 |

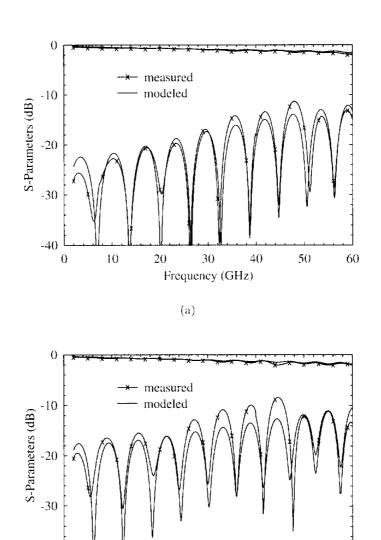

| 4.11 | Measured and modeled S-parameters of the W = 100 $\mu$ m DMTL with 38 bridges (total length= 7.6 mm) at (a) 0 V and (b) a maximum applied bias                                                                                                                                                                                 |    |

|      | of 13 V                                                                                                                                                                                                                                                                                                                        | 67 |

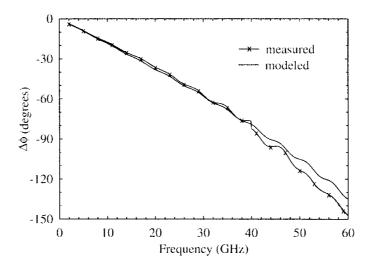

| 4.12 | Measured and modeled phase shift of the W = 100 $\mu$ m DMTL at 13 V                                                                                                                                                                                                                                                           | 68 |

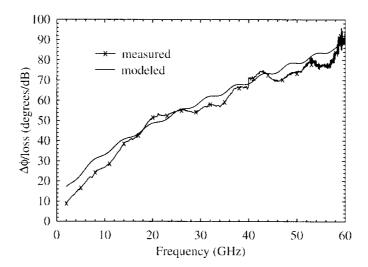

| 4.13 | Measured and modeled phase shift per dB loss for the W = 100 $\mu$ m DMTL showing 90°/dB at 60 GHz or 4 dB loss for 360° phase shift                                                                                                                                                                                           | 68 |

| 4.14 | Loaded transmission line loss and loss due to bridge resistance vs. frequency. The line loss is calculated from Hoffmann's equation for a 300 $\mu$ m total width                                                                                                                                                              |    |

|      | 100 GIIA, the bridge spacing is 110 pm and and strong.                                                                                                                                                                                                                                                                         | 70 |

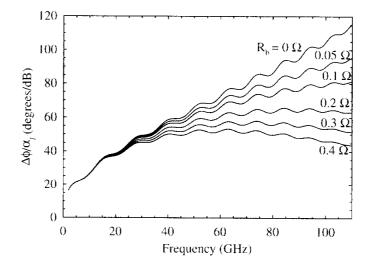

| 4.15 | Phase shift per dB loss calculated from a Libra circuit simulation of a 32 bridge DMTL on quartz with a capacitance ratio of 1.17 and different bridge                                                                                                                                                                         | 70 |

| 4.16 | resistances specified at 30 GHz and varying as $\sqrt{f}$                                                                                                                                                                                                                                                                      | •0 |

|      | for a bridge resistances of (a) 0.15 $\Omega$ at 30 GHz and (b) 0 $\Omega$ . The total CPW width is $\lambda_d/5$ at 100 GHz for each substrate which is 180 $\mu$ m, 300 $\mu$ m, and                                                                                                                                         |    |

|      | $600~\mu\mathrm{m}$ for silicon, quartz, and air, respectively. The loaded impedance is 48 $\Omega$ , the capacitance ratio is 1.2, and the Bragg frequency is 240 GHz                                                                                                                                                         | 72 |

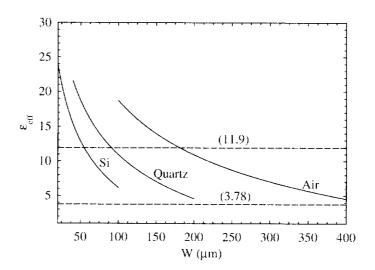

| 4.17 | 7 Calculated effective dielectric constant for W-band DMTL's versus center conductor width. The relative dielectric constant of silicon (11.9) and quartz                                                                                                                                                                      |    |

|      | (3.78) are shown for reference                                                                                                                                                                                                                                                                                                 | 73 |

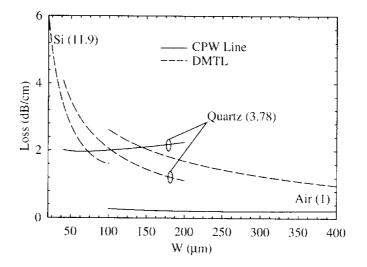

| 4.18 | Calculated loss at 100 GHz versus center conductor width. The CPW line loss (—) includes radiation loss while the DMTL line neglects radiation but                                                                                                                                                                             |    |

|      | includes loss due to a 0.15 $\Omega$ bridge resistance at 30 GHz (0.27 $\Omega$ at 100 GHz).                                                                                                                                                                                                                                   | 73 |

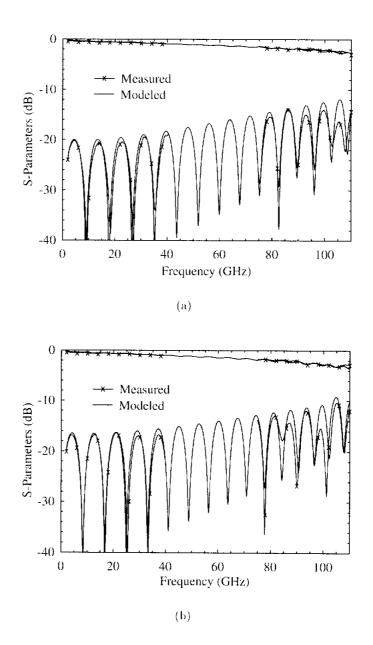

| 4.19       | Measured (2-40 GHz and 75-110 GHz) and modeled S-parameters at (a) 0 V bias and (b) a maximum bias of 26 V for a W-band DMTL phase shifter. The dimensions are listed in Table 4.7 and the circuit parameters are listed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | in Table 4.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75       |

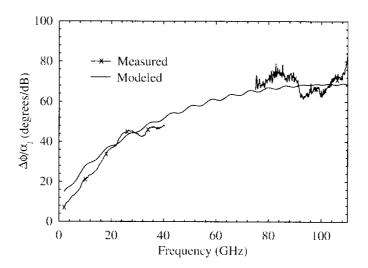

| 4.20       | Measured and modeled phase shift per dB loss at a maximum bias of 26 V for a W-band DMTL phase shifter. The dimensions are listed in Table 4.7 and the circuit parameters are listed in Table 4.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76       |

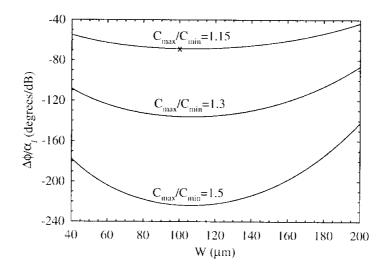

| 4.21       | Calculated phase shift per dB loss at 100 GHz with a capacitance ratio of 1.15, 1.3, and 1.5. The measured data point is shown for a center conductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | • •      |

| 4.22       | width of 100 $\mu$ m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76       |

|            | loss, calculated from (3.20) uses the measured CPW loss to calculate $R_s$ . A bridge resistance of 0.15 $\Omega$ at 30 GHz is also included in the estimate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77       |

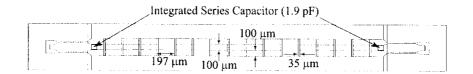

| 4.23       | bridges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79       |

|            | Reduced DC circuit of Figure 4.23 with integrated capacitors, $C_s$ , at both ends of the DMTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79       |

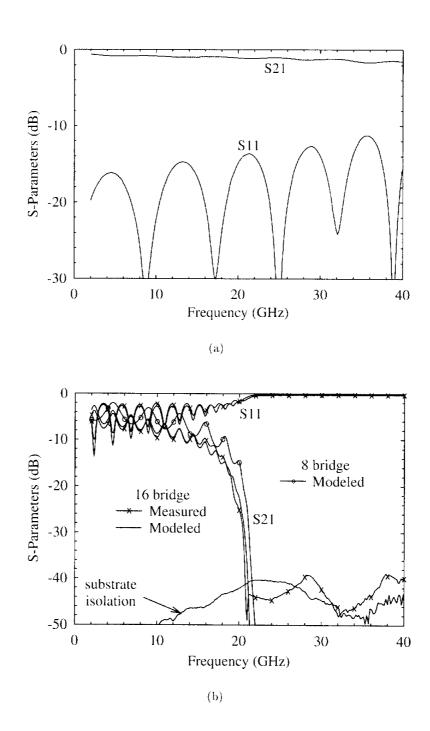

| 4.25       | Optimized 16 bridge DMTL with 1.9 pF integrated series capacitors for stabilization with (a) 0 V and (b) 40 V applied bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80       |

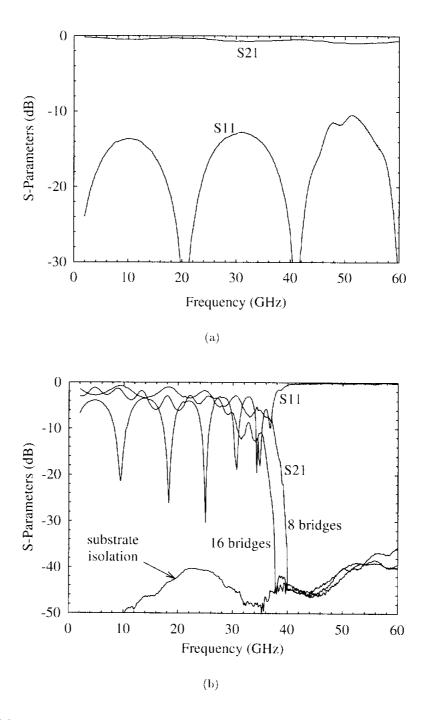

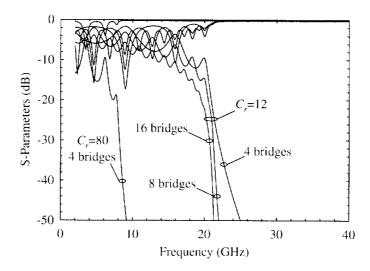

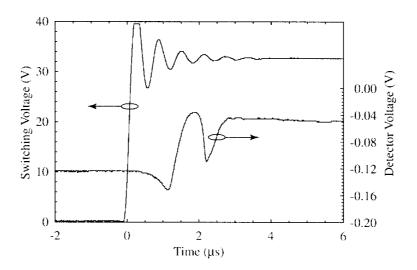

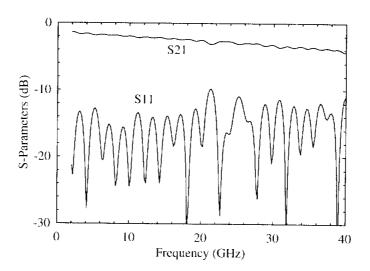

| 5.1        | Measured results of distributed MEMS switches with 8 and 16 30- $\mu$ m wide bridges spaced at 306 $\mu$ m in the (a) open position (bridge up) and (b) closed position. The S-parameters for the open position are only shown for the case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | വ        |

| 5.2        | of the 8 bridge design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82<br>84 |

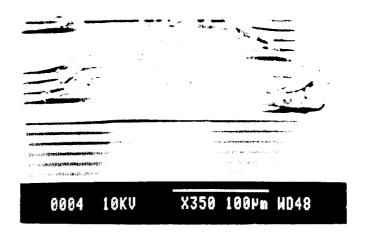

| 5.3        | SEM image of the remains of a DMTL after the breakdown voltage of the $\mathrm{Si}_x\mathrm{N}_y$ was exceeded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85       |

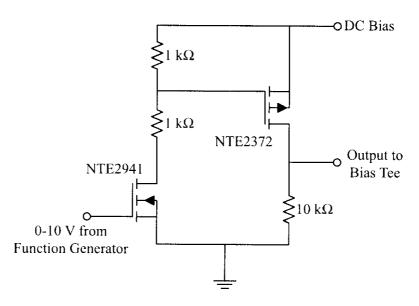

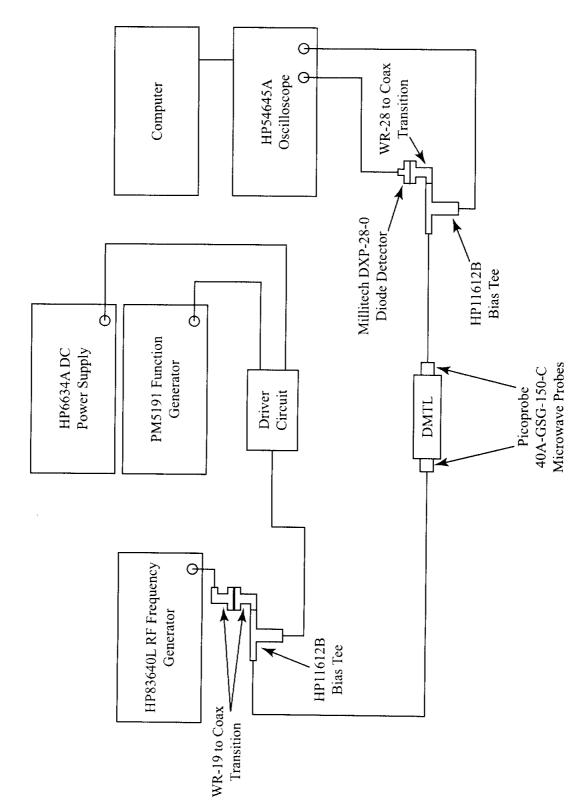

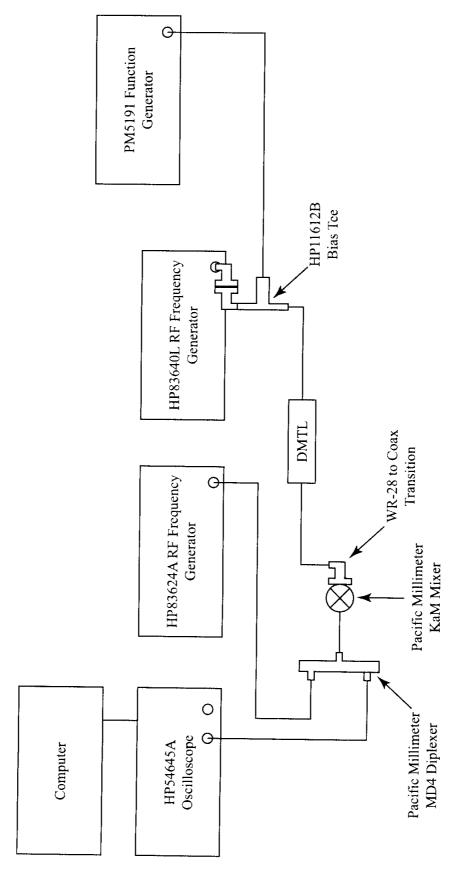

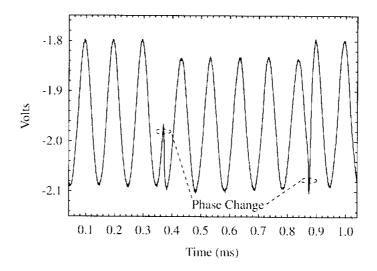

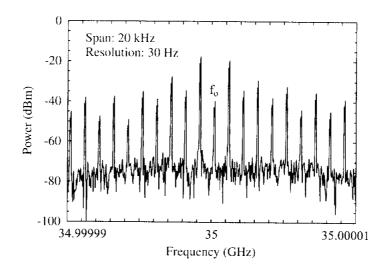

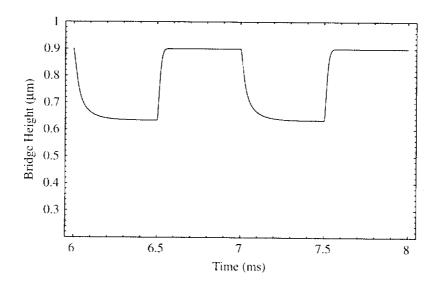

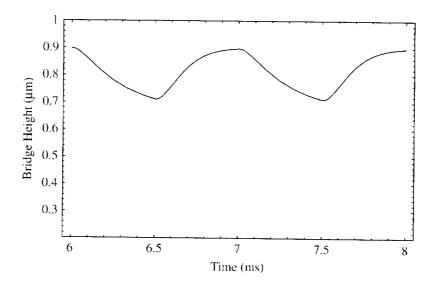

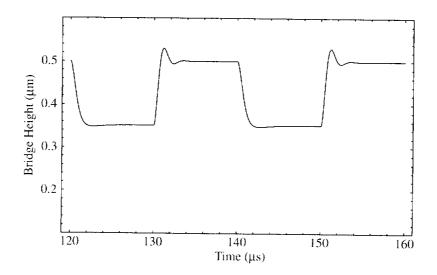

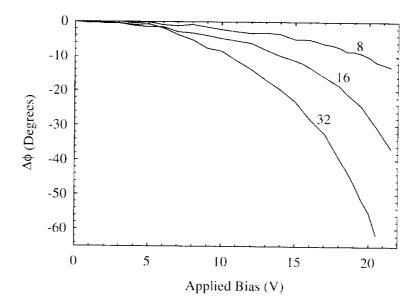

| 5.4        | Variation of lower cutoff frequency with different number of sections used in the distributed switch design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86       |