#### ABSTRACT

Block Enlargement Optimizations for Increasing the Instruction Fetch Rate in Block-Structured Instruction Set Architectures

by Eric Hao

Chair: Yale N. Patt

To exploit larger amounts of instruction level parallelism, processors are being built with wider issue widths and larger numbers of functional units. Instruction fetch rate must also be increased in order to effectively exploit the performance potential of such processors. Blockstructured ISAs are a new class of instruction set architectures that were designed to address the performance obstacles faced by processors attempting to exploit high levels of instruction level parallelism. The major distinguishing feature of a block-structured ISA is that it defines the architectural atomic unit (i.e. the instruction) to be a group of operations which is called an atomic block. This dissertation defines an optimization, block enlargement, that can be applied to a block-structured ISA to increase the instruction fetch rate of a processor that implements that ISA. A compiler that generates block-structured ISA code and a simulator that models the execution of that code on a block-structured ISA processor were constructed to evaluate the performance benefit of block-structured ISAs. This dissertation shows that for the SPECint95 benchmarks, the block-structured ISA processor executing enlarged atomic blocks and using simpler microarchitectural mechanisms to support wideissue and dynamic scheduling outperforms a conventional ISA processor that also supports wide-issue and dynamic scheduling by 28% when assuming perfect branch prediction and by 15% when using real branch prediction.

# Block Enlargement Optimizations for Increasing the Instruction Fetch Rate in Block-Structured Instruction Set Architectures

by

#### Eric Hao

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 1997

#### Doctoral Committee:

Professor Yale N. Patt, Chair Professor John T. Coffey Professor Kevin J. Compton Professor Edward S. Davidson Pohua P. Chang, Senior Researcher, Intel Corporation

#### ACKNOWLEDGEMENTS

I give special thanks to my advisor, Professor Yale Patt, for all that he has taught me in the past four years. In particular, I will continue to value the intellectual and personal lessons I have learned from him long after the technical knowledge I have learned here has grown obsolete.

I also thank the members of my dissertation committee, Professor Edward Davidson, Professor Kevin Compton, Professor John Coffey, and Pohua Chang. I am deeply appreciative for the time and effort they devoted towards guiding the work of my dissertation. In addition, I thank Pohua Chang for serving as my Intel mentor and providing valuable input to the development of the compiler used in this dissertation.

I am grateful for the opportunity to have worked with five generations of the HPS group: Steve Melvin; Mike Butler, Tse-Yu Yeh, and Robert Hou; Bruce Worthington and Greg Ganger; Po-Yung Chang, Carlos Fuentes, Jared Stark, Chris Eberly, Eric Sprangle and Lea-Hwang Lee; and Sanjay Patel, Mark Evers, Dan Friendly, Paul Racunas, Peter Kim, and Rob Chappell. Their help was invaluable and their company will be missed. Special thanks go to Steve Melvin for conceiving the original ideas behind block-structured ISAs, Po-Yung Chang for helping me write the compiler, Mark Evers for developing the simulator, and Jared Stark for answering all my questions about hardware.

I am indebted to our industrial partners: Intel, NCR, Hewlett-Packard, and Motorola, for their technical and financial support. In particular, I thank Intel for the gift of the Proton compiler and the Intel Fellowship.

Finally, I thank the Hwangs for their company and support, without which my years here at Michigan would not have been nearly as enjoyable.

## TABLE OF CONTENTS

| ACKNO  | OWLE   | DGEMENTS                                               |

|--------|--------|--------------------------------------------------------|

| LIST O | F TAE  | <b>BLES</b>                                            |

| LIST O | F FIG  | <b>URES</b>                                            |

| LIST O | F APF  | PENDICES                                               |

| CHAPT  | ΓERS   |                                                        |

| 1      | Introd |                                                        |

|        | 1.1    | The Basic Block Fetch Bottleneck                       |

|        | 1.2    | The Block-Structured ISA Solution                      |

|        | 1.3    | Thesis Statement                                       |

|        | 1.4    | Contributions                                          |

|        | 1.5    | Dissertation Organization                              |

| 2      | Relate | d Work                                                 |

|        | 2.1    | Hardware-based Approaches                              |

|        |        | 2.1.1 Predicting Multiple Branches Per Cycle           |

|        |        | 2.1.2 The Trace Cache                                  |

|        | 2.2    | Software-based Approaches                              |

|        |        | 2.2.1 Trace and Superblock Scheduling                  |

|        |        | 2.2.2 Predicated Execution                             |

|        |        | 2.2.3 Hyperblock Scheduling                            |

|        |        | 2.2.4 VLIW Multi-Way Jumps                             |

|        |        | 2.2.5 Multiscalar Processors                           |

| 3      | Simula | ation Methodology                                      |

|        | 3.1    | The Compiler                                           |

|        | 3.2    | The HPS Processor Model                                |

|        | 3.3    | The Simulators                                         |

|        | 3.4    | The SPEC95 Benchmarks                                  |

| 4      | Block- | Structured ISAs and the Block Enlargement Optimization |

| 7      | 4.1    | The Block Enlargement Optimization                     |

|        | 1.1    | The Proof Phime Content Obumpanon                      |

|   |                   | 4.1.1 Overview                                                             |

|---|-------------------|----------------------------------------------------------------------------|

|   |                   | 4.1.2 Enlarging the Compiler's Scope for Optimization                      |

|   |                   | 4.1.3 Effect on ICache Performance                                         |

|   |                   | 4.1.4 Simulation Concerns                                                  |

|   | 4.2               | Specification of a Block-Structured ISA                                    |

|   |                   | 4.2.1 The Base ISA                                                         |

|   |                   | 4.2.2 Trap Operations                                                      |

|   |                   | 4.2.3 Fault Operations                                                     |

|   |                   | 4.2.4 Subroutine Calls                                                     |

| 5 | Block             | Enlargement — Measurements and Analysis 2'                                 |

| 0 | 5.1               | The Base Block Enlargement Optimization                                    |

|   | $\frac{5.1}{5.2}$ | ICache Performance Issues                                                  |

|   | $\frac{5.2}{5.3}$ | Block Enlargement Obstacles                                                |

|   | $\frac{5.3}{5.4}$ | Function Inlining                                                          |

|   | 5.4 $5.5$         | Handling the Max Successor Constraint                                      |

|   | 5.6               | Summary                                                                    |

|   | 5.0               | Juninary                                                                   |

| 6 | Branch            | Prediction for Block-Structured ISAs                                       |

|   | 6.1               | Effect on Prediction Accuracy                                              |

|   | 6.2               | Two-Level Adaptive Branch Prediction                                       |

|   |                   | 6.2.1 Background                                                           |

|   |                   | 6.2.2 Extensions for Block-Structured ISAs                                 |

|   | 6.3               | Extensions to the Branch Target Buffer                                     |

|   | 6.4               | A Specific Implementation                                                  |

| 7 | Branch            | Prediction — Measurements and Analysis                                     |

| • | 7.1               | Base Comparison                                                            |

|   | 7.2               | Branch Predictor Performance                                               |

|   |                   | 7.2.1 Branch Prediction Accuracy                                           |

|   |                   | 7.2.2 Branch Resolution Time                                               |

|   | 7.3               | BTB Performance                                                            |

|   | 7.4               | Increasing the Predictor Size 6                                            |

|   | 7.5               | Block Enlargement Effects                                                  |

|   | 7.6               | Block-Structured ISA Extensions                                            |

|   |                   | 7.6.1 Target Count                                                         |

|   |                   | 7.6.2 Target Mapping                                                       |

|   | 7.7               | Overall Performance                                                        |

|   | 7.8               | Summary                                                                    |

| 8 | D11.              | Enlangement for Scientific Code Managements and Analysis 79                |

| O | 8.1               | Enlargement for Scientific Code — Measurements and Analysis                |

|   | 8.2               | 0 1                                                                        |

|   | 8.3               | ICache Performance       83         Branch Prediction Performance       83 |

|   | 8.4               | Future Directions 85                                                       |

|   | () 4              | - PRODUCE TO DECIMOUS (A)                                                  |

| 9 (    | Conclu | sion             |   | <br> | <br> | <br> | <br> |      |   |   |   | <br>85  |

|--------|--------|------------------|---|------|------|------|------|------|---|---|---|---------|

|        | 9.1    | Contributions .  |   | <br> | <br> | <br> |      |      |   |   |   | <br>85  |

|        | 9.2    | Future Direction | s | <br> | <br> | <br> |      |      |   |   |   | <br>86  |

| APPENI | DICE   | <b>S</b>         |   | <br> | <br> | <br> |      | <br> |   |   |   | <br>88  |

| BIBLIO | FR.AF  | РНҮ              |   | _    |      |      |      |      | _ | _ | _ | <br>111 |

## LIST OF TABLES

| Table |                                                     |     |

|-------|-----------------------------------------------------|-----|

| 3.1   | Instruction classes and latencies                   | 15  |

| 3.2   | The SPECint95 benchmarks                            | 16  |

| 3.3   | The SPECfp95 benchmarks                             | 17  |

| 5.1   | Call sites that were selected for function inlining | 47  |

| 7.1   | BTB miss counts                                     | 67  |

| D.1   | Inlined call sites for the compress benchmark       | .07 |

| D.2   | Inlined call sites for the go benchmark             | 07  |

| D.3   | Inlined call sites for the ijpeg benchmark          | .08 |

| D.4   | Inlined call sites for the xlisp benchmark          | .08 |

| D.5   | Inlined call sites for the m88ksim benchmark        | .09 |

| D.6   | Inlined call sites for the perl benchmark           | .09 |

| D.7   | Inlined call sites for the vortex benchmark         | 10  |

## LIST OF FIGURES

| Figure     |                                                                                                                                                              |                 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.1        | The performance of a sixteen wide issue processor executing the gcc bench-                                                                                   |                 |

|            | mark as the number of blocks fetched per cycle is increased from one to four.                                                                                | 2               |

| 1.2        | The average number of instructions fetched by a sixteen wide issue processor                                                                                 |                 |

|            | executing the gcc benchmark as the number of blocks fetched per cycle is                                                                                     |                 |

|            | increased from one to four                                                                                                                                   | 2               |

| 2.1        | Using superblock scheduling to combine basic blocks                                                                                                          | 7               |

| 2.2        | Using predicated execution to combine basic blocks                                                                                                           | Ö               |

| 2.3        | Comparing superblock and hyperblock scheduling                                                                                                               | 10              |

| 2.4        | Building a VLIW tree instruction                                                                                                                             | 11              |

| 3.1        | Experimental setup for comparing block-structured ISA performance to con-                                                                                    |                 |

|            | ventional ISA performance.                                                                                                                                   | 14              |

| 4.1        | Combining atomic blocks into an enlarged atomic block.                                                                                                       | 19              |

| 4.2        | Converting traps into faults for the block enlargement optimization                                                                                          | 20              |

| 4.3        | Comparing the block enlargement optimization to superblock scheduling                                                                                        | 21              |

| 4.4        | Using block enlargement to increase the compiler's scope for local optimization.                                                                             | 22              |

| 4.5        | The fall through trap target problem for block-structured ISAs                                                                                               | 25              |

| 4.6        | The fall through return address problem for block-structured ISAs                                                                                            | 26              |

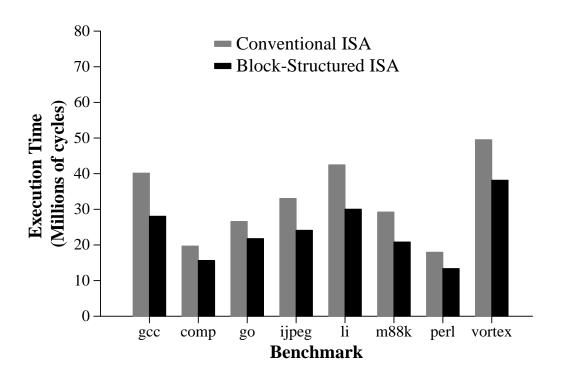

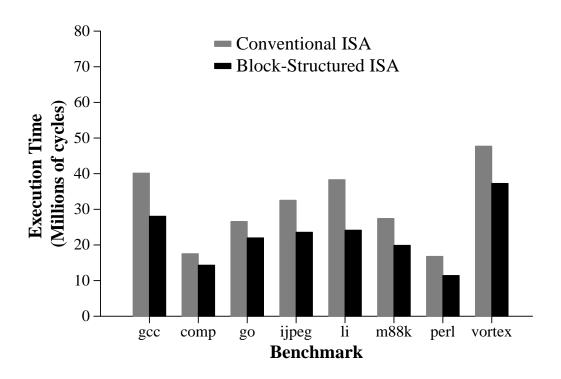

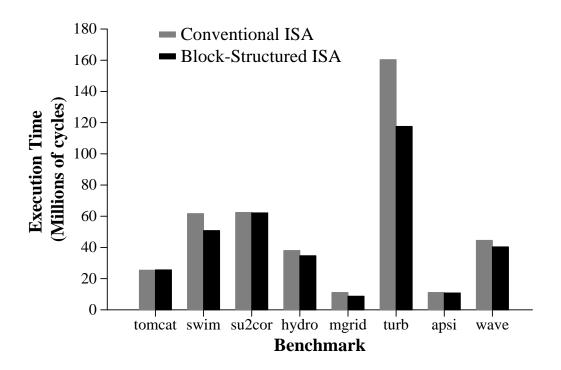

| 5.1        | Performance comparison of block-structured ISA executables to conventional                                                                                   | 0.0             |

| <b>r</b> 0 | ISA executables.                                                                                                                                             | 28              |

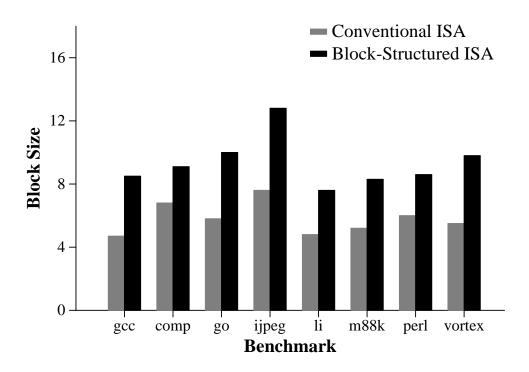

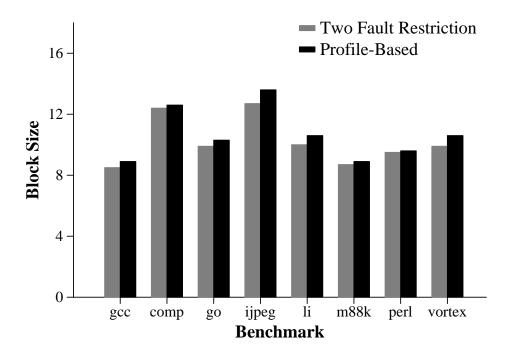

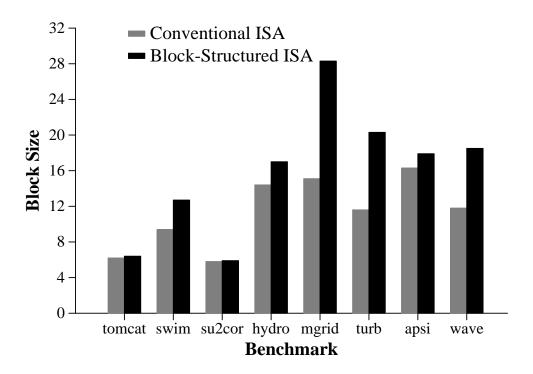

| 5.2        | Average block sizes for block-structured and conventional ISA executables.                                                                                   | 29              |

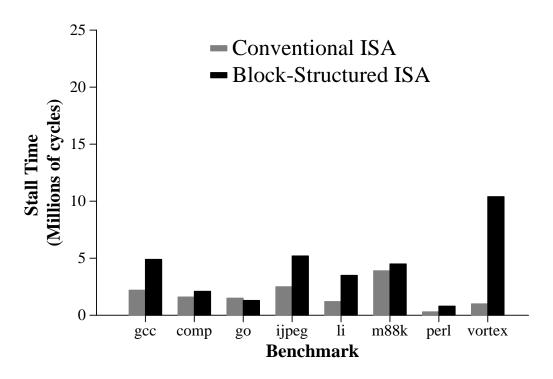

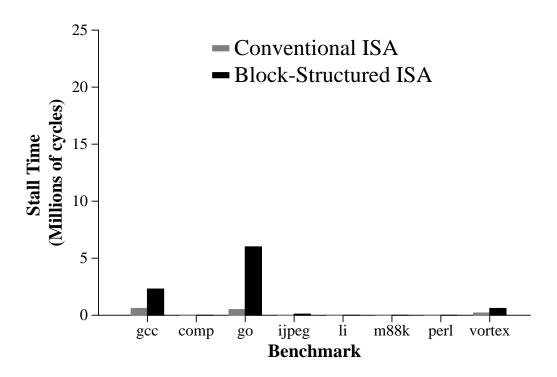

| 5.3        | The number of cycles that instruction fetch was stalled due to a full-window.                                                                                | 30              |

| 5.4        | The number of cycles that instruction fetch was stalled due to an icache miss.                                                                               | 31              |

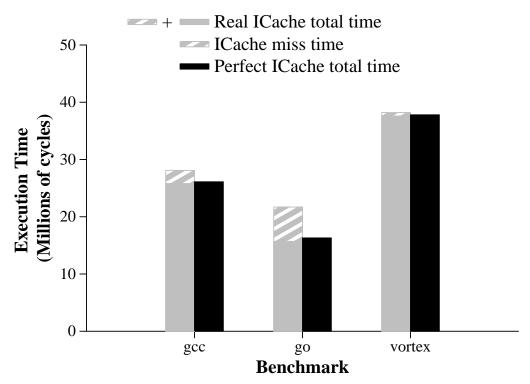

| 5.5        | Execution times for a perfect and a 128KB icache                                                                                                             | 32              |

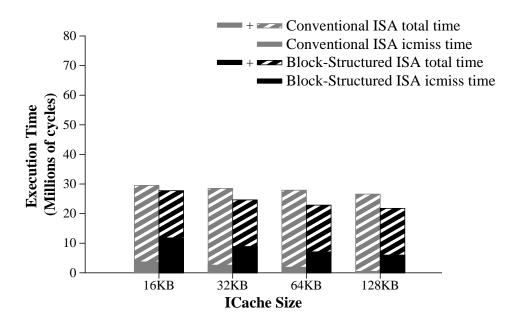

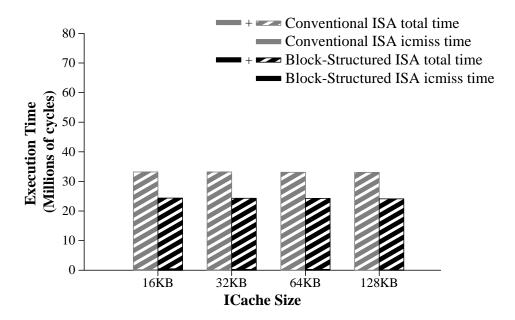

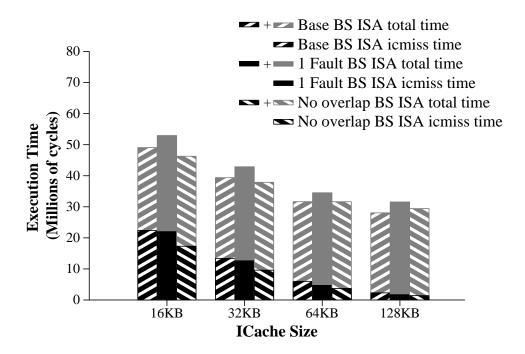

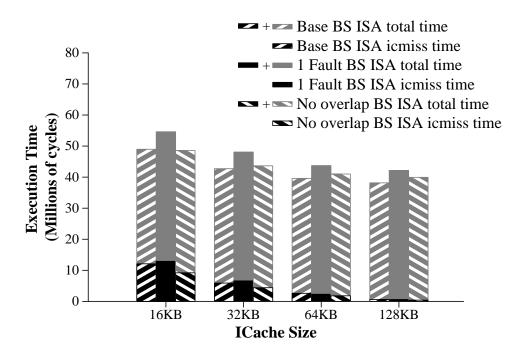

| 5.6        | The number of icache miss and total execution cycles for the gcc benchmark.                                                                                  | 33              |

| 5.7        | The number of icache miss and total execution cycles for the go benchmark.                                                                                   | 33              |

| 5.8        | The number of icache miss and total execution cycles for the perl benchmark.                                                                                 | 34              |

| 5.9        | The number of icache miss and total execution cycles for the vortex benchmark.                                                                               | 34              |

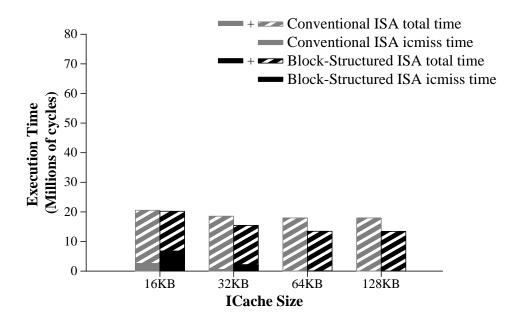

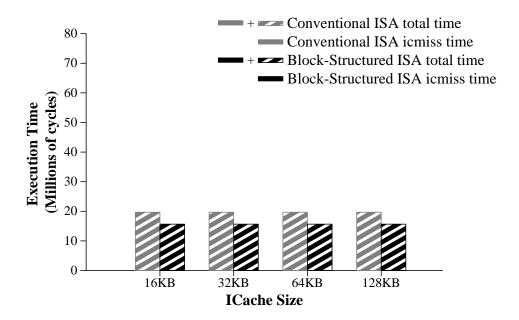

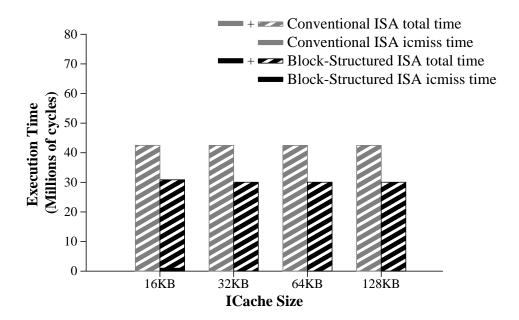

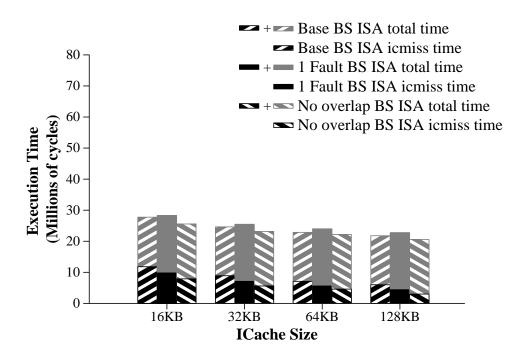

| 5.10       | The number of icache miss and total execution cycles for the compress bench-                                                                                 | 25              |

| K 11       | The number of ignals miss and total execution guales for the iiner bandmark                                                                                  | 35<br>25        |

|            | The number of icache miss and total execution cycles for the ijpeg benchmark.  The number of icache miss and total execution cycles for the xlisp benchmark. | $\frac{35}{36}$ |

| 9.14       | THE HUMBEL OF ICACHE HIBS ARE TOTAL EXECUTION CYCLES FOR THE XIISD DENCINHALK.                                                                               | ા               |

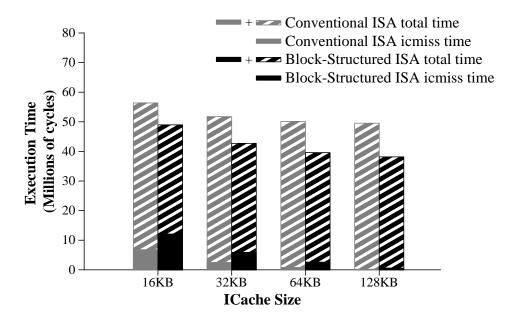

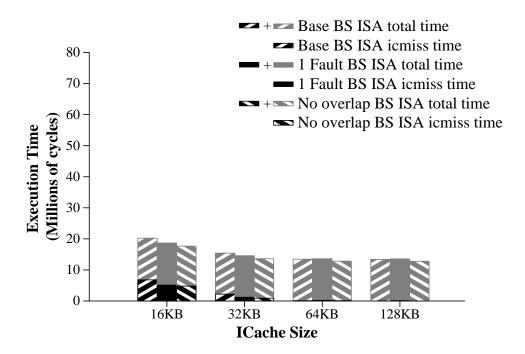

| 5.13 | The number of icache miss and total execution cycles for the m88ksim benchmark.                                          |

|------|--------------------------------------------------------------------------------------------------------------------------|

| 5.14 | Forming overlapped enlarged blocks with the block enlargement optimization.                                              |

|      | Restraining the block enlargement optimization to prevent the formation of overlapped enlarged blocks.                   |

| 5.16 | Comparing the base, one fault, and no overlap variations of the block enlargement optimization for the gcc benchmark.    |

| 5.17 | Comparing the base, one fault, and no overlap variations of the block enlargement optimization for the go benchmark      |

| 5.18 | Comparing the base, one fault, and no overlap variations of the block enlargement optimization for the perl benchmark    |

| 5.19 | Comparing the base, one fault, and no overlap variations of the block enlargement optimization for the vortex benchmark  |

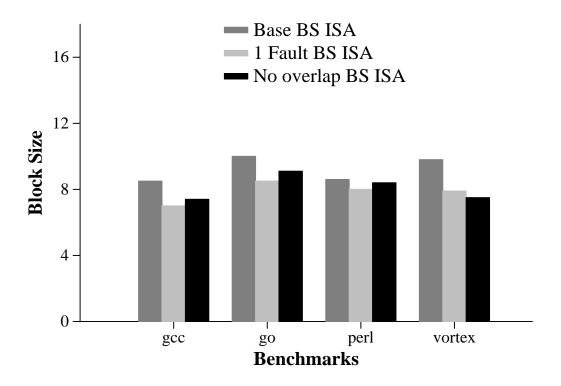

| 5.20 | The average block sizes for the base, one fault, and no overlap variations of the block enlargement optimization         |

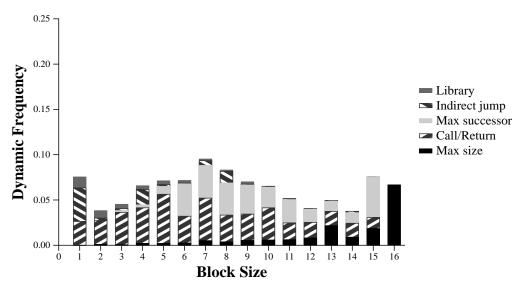

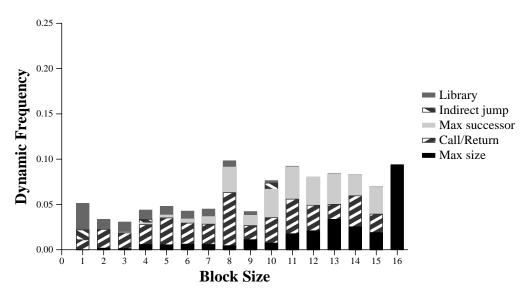

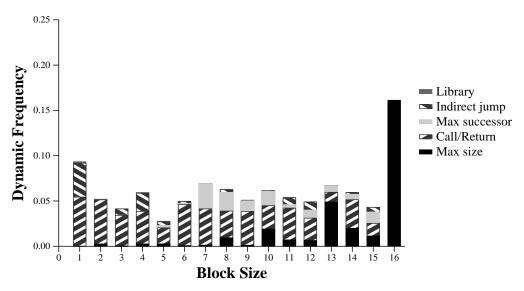

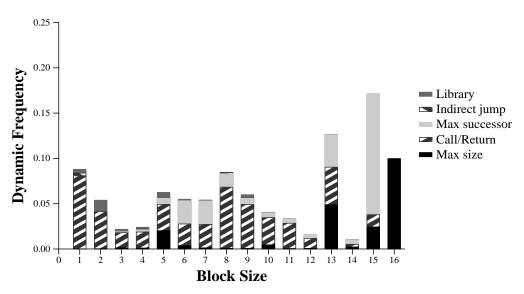

| 5.21 | Block termination reasons for the gcc benchmark                                                                          |

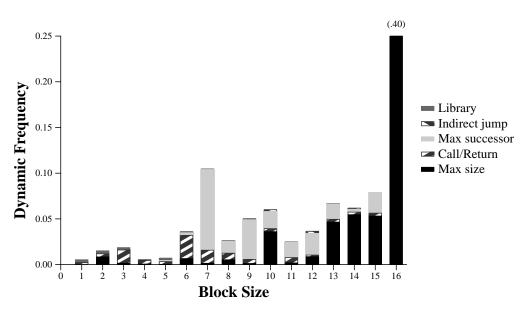

| 5.22 | Block termination reasons for the compress benchmark                                                                     |

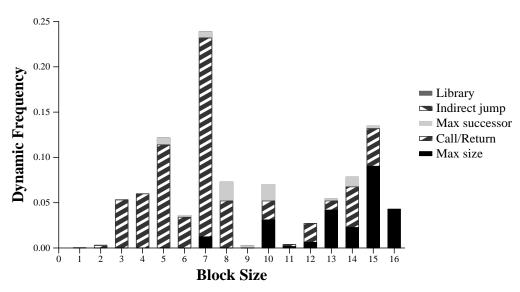

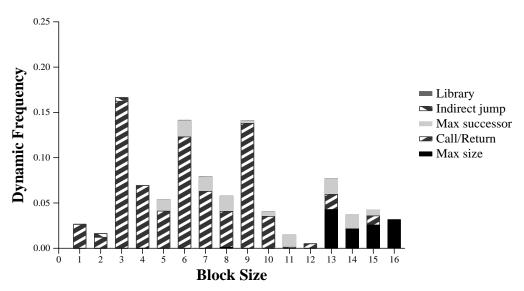

| 5.23 | Block termination reasons for the go benchmark                                                                           |

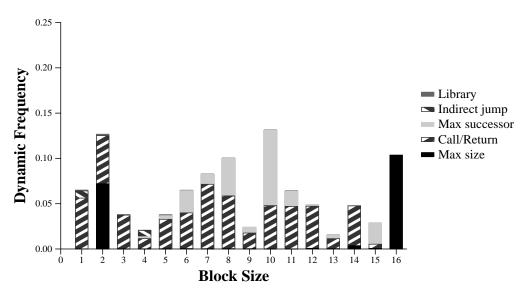

| 5.24 | Block termination reasons for the ijpeg benchmark                                                                        |

| 5.25 | Block termination reasons for the li benchmark                                                                           |

| 5.26 | Block termination reasons for the m88ksim benchmark                                                                      |

| 5.27 | Block termination reasons for the perl benchmark                                                                         |

| 5.28 | Block termination reasons for the vortex benchmark                                                                       |

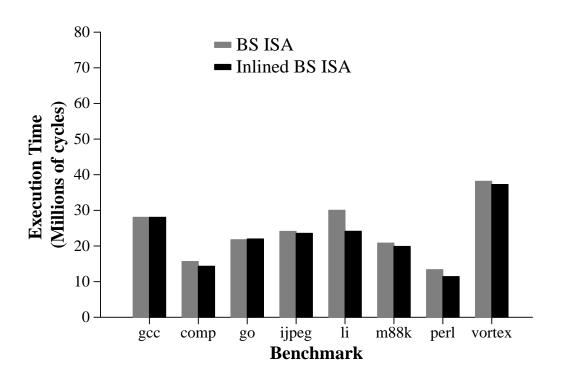

| 5.29 | Execution times of block-structured ISA executables compiled with and without function inlining                          |

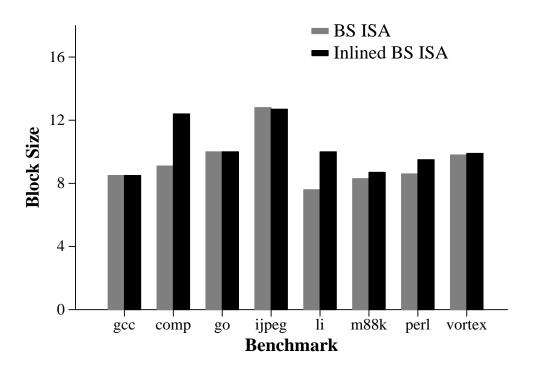

| 5.30 |                                                                                                                          |

| 5.31 |                                                                                                                          |

| 5.32 | Enforcing the max successor constraint                                                                                   |

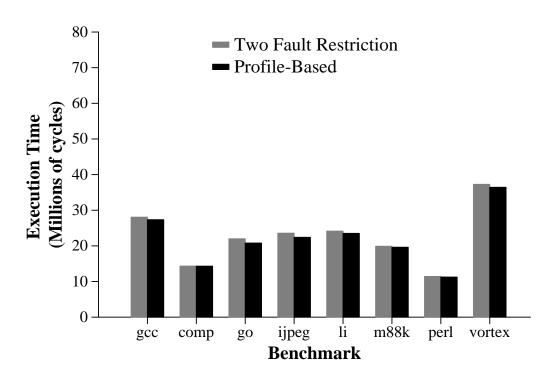

|      | Performance of the profile-based block enlargement                                                                       |

|      | Average block size for profile-based block enlargement                                                                   |

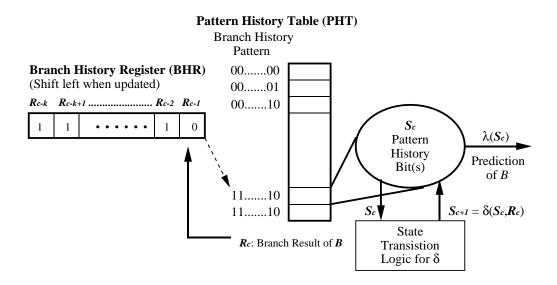

| 6.1  | Structure of the global variation of the Two-Level Adaptive Branch Predictor.                                            |

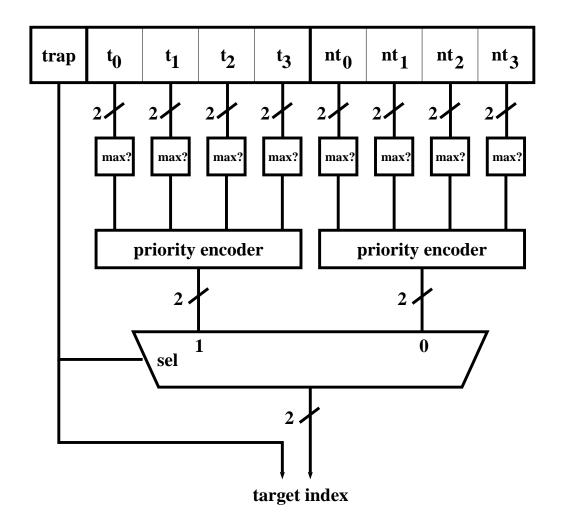

| 6.2  | Generating the predicted target index from a PHT entry in a block-structured                                             |

|      | ISA branch predictor that supports eight targets per block                                                               |

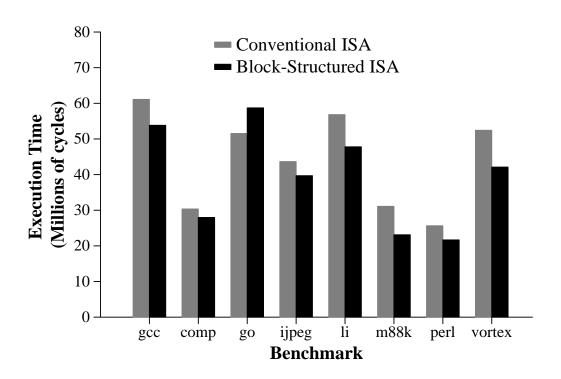

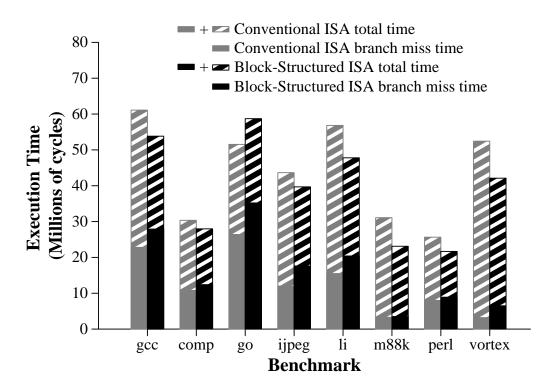

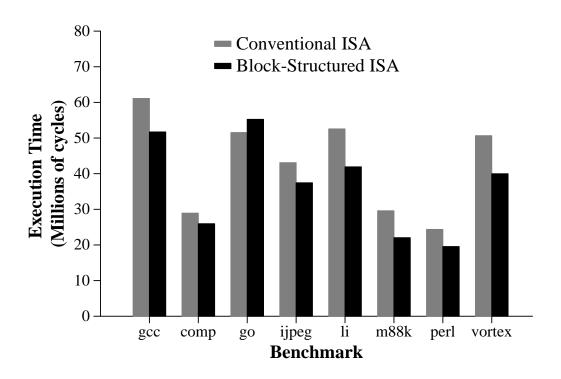

| 7.1  | Execution times for block-structured ISA executables and conventional ISA executables when using a 32KB branch predictor |

| 7 9  |                                                                                                                          |

| 7.2  | Execution times for block-structured ISA executables and conventional ISA                                                |

| 7.3  | executables when using a 32KB branch predictor                                                                           |

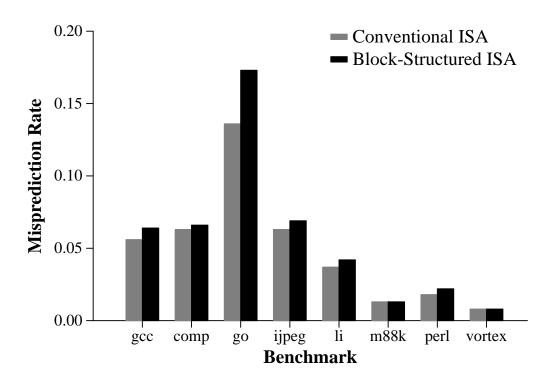

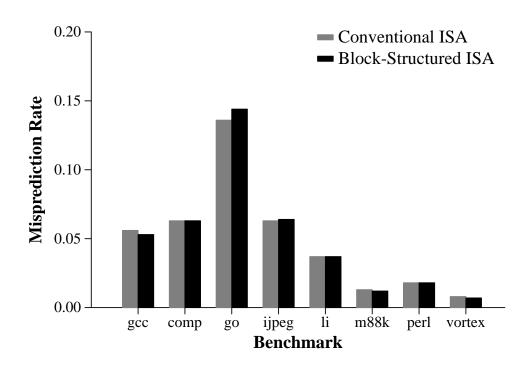

| 1.0  | conventional ISA predictor                                                                                               |

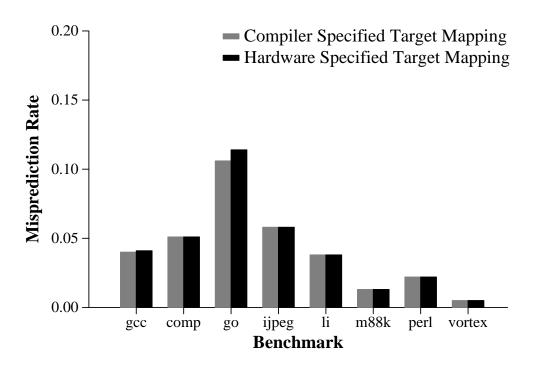

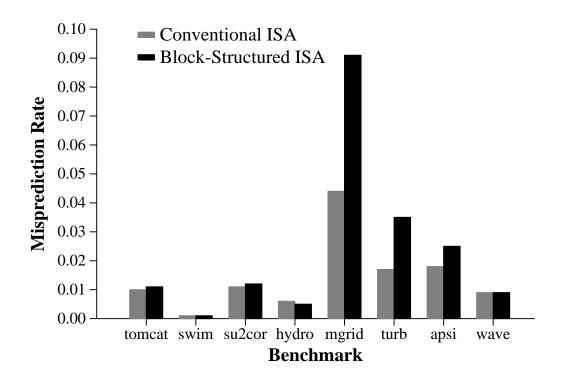

| 7.4  | Misprediction rates for block-structured and conventional ISA predictors with 16 bit history registers                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

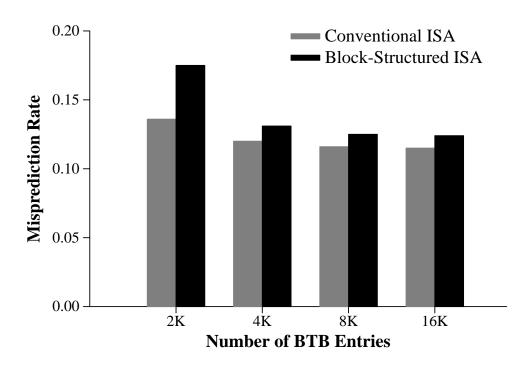

| 7.5  | The effect of BTB size on misprediction rates for the go benchmark                                                                              |

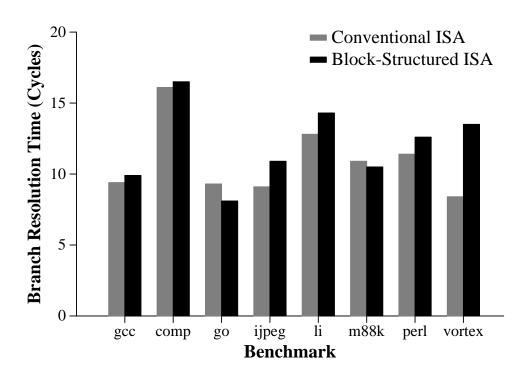

| 7.6  | Mispredicted branch resolution times for the block-structured and conventional ISA predictors                                                   |

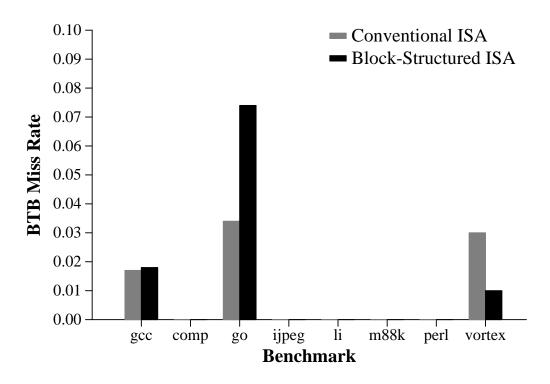

| 7.7  | BTB miss rates for the block-structured ISA and the conventional ISA branch predictors                                                          |

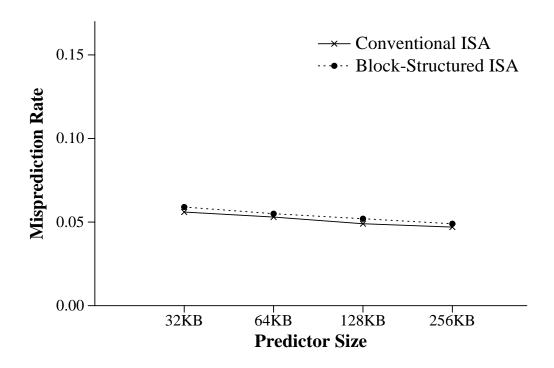

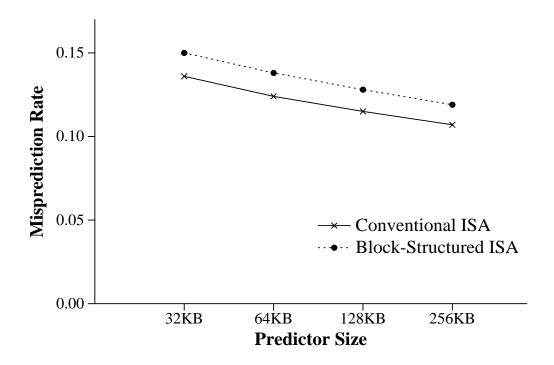

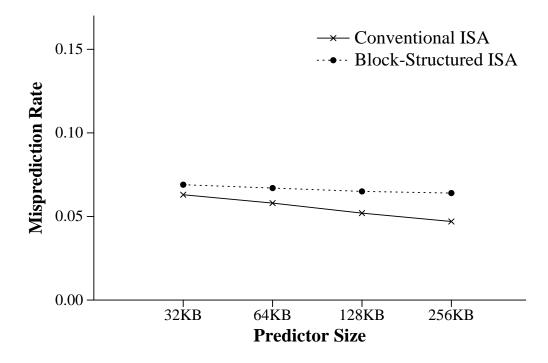

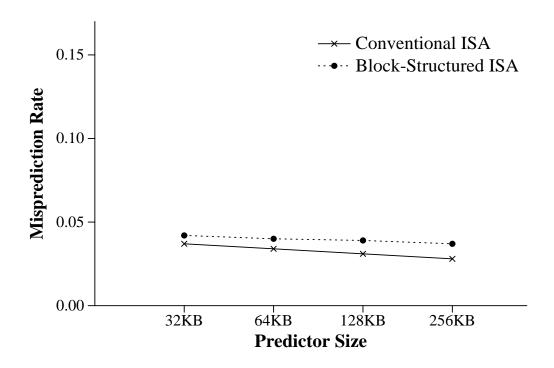

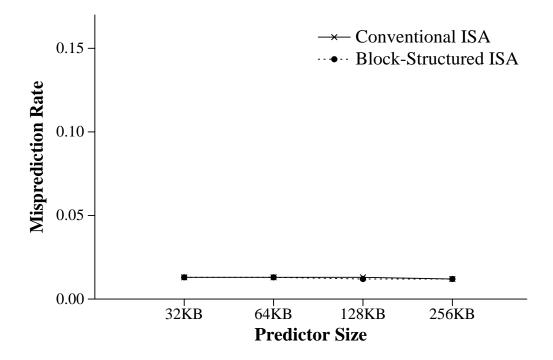

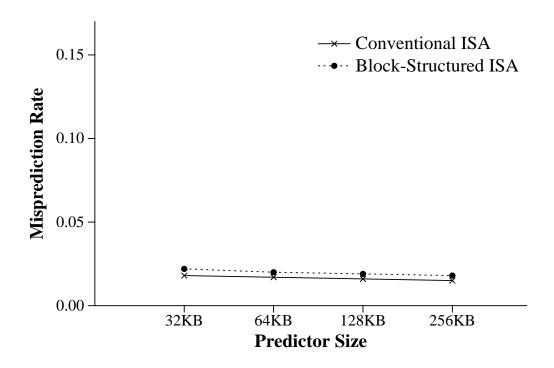

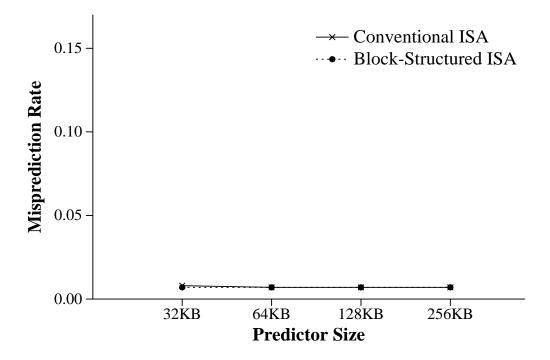

| 7.8  | Misprediction rates for the gcc benchmark for block-structured ISA and conventional ISA branch predictors of size 32KB to 256KB                 |

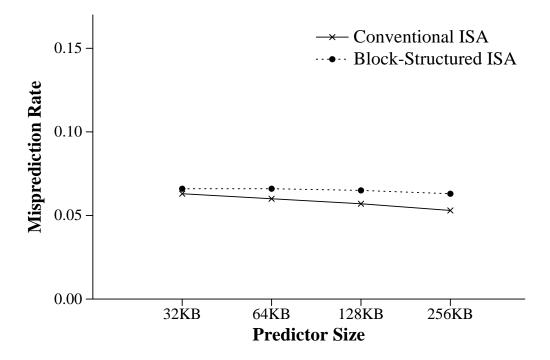

| 7.9  | Misprediction rates for the compress benchmark for block-structured ISA and conventional ISA branch predictors of size 32KB to 256KB            |

| 7.10 | Misprediction rates for the go benchmark for block-structured ISA and conventional ISA branch predictors of size 32KB to 256KB                  |

| 7.11 | Misprediction rates for the ijpeg benchmark for block-structured ISA and conventional ISA branch predictors of size 32KB to 256KB               |

| 7.12 | Misprediction rates for the xlisp benchmark for block-structured ISA and conventional ISA branch predictors of size 32KB to 256KB               |

| 7.13 | Misprediction rates for the m88ksim benchmark for block-structured ISA and conventional ISA branch predictors of size 32KB to 256KB             |

| 7.14 | Misprediction rates for the perl benchmark for block-structured ISA and conventional ISA branch predictors of size 32KB to 256KB                |

| 7.15 | Misprediction rates for the vortex benchmark for block-structured ISA and conventional ISA branch predictors of size 32KB to 256KB              |

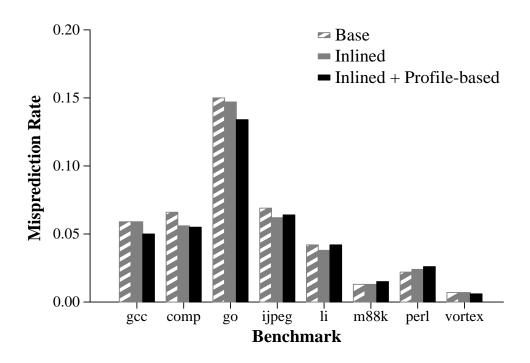

| 7.16 | Branch misprediction rates for the three variations of the block enlargement optimization                                                       |

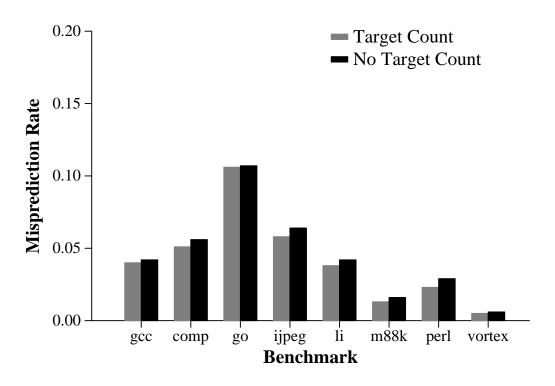

| 7.17 | Misprediction rates for branch predictors with and without the target count extension.                                                          |

| 7.18 | Misprediction rates for branch predictors with and without compiler specified target mappings                                                   |

| 7.19 | Execution times for block-structured and and conventional ISA executables when using a 32KB predictor                                           |

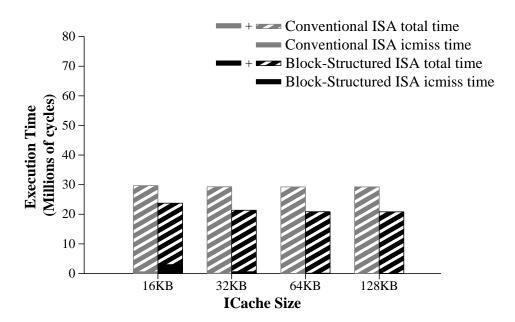

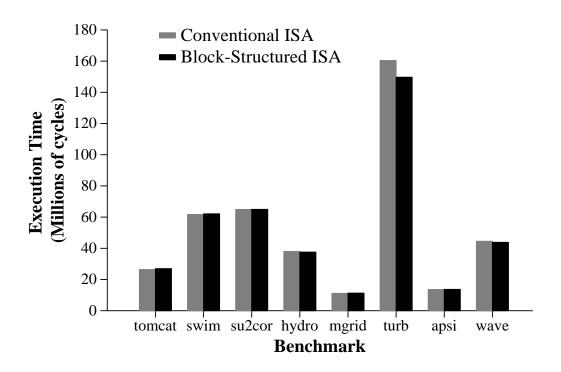

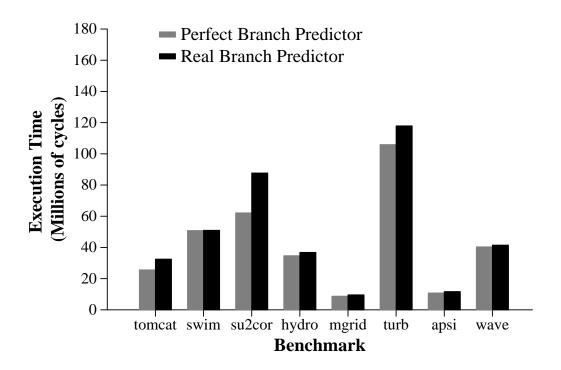

| 8.1  | Performance comparison of block-structured ISA executables to conventional ISA executables for a 16 wide machine with perfect branch prediction |

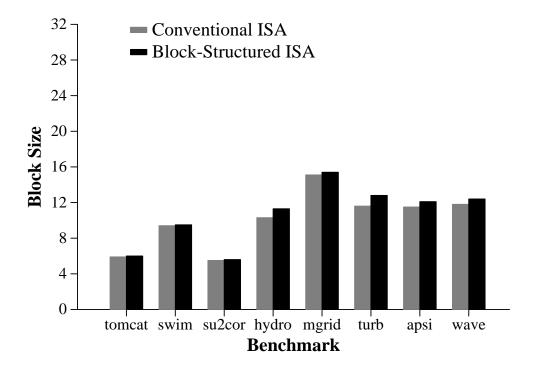

| 8.2  | Average block sizes for block-structured and conventional ISA executables for a 16 wide machine                                                 |

| 8.3  | Performance comparison of block-structured ISA executables to conventional ISA executables for a 32 wide machine with perfect branch prediction |

| 8.4  | A verage block sizes for block-structured and conventional ISA executables for a 32 wide machine                                                |

| 8.5  | Misprediction rates for block-structured and conventional ISA executables                                                                       |

| 8.6  | Execution times for block-structured ISA executables running on a 32 wide machine with and without perfect branch prediction                    |

| A.1  | Execution times for the gcc benchmark                                                                                                           |

| A.2  | Average packet sizes for the gcc benchmark         |

|------|----------------------------------------------------|

| A.3  | Execution times for the compress95 benchmark       |

| A.4  | Average packet sizes for the compress95 benchmark9 |

| A.5  | Execution times for the go benchmark               |

| A.6  | Average packet sizes for the go benchmark          |

| A.7  | Execution times for the ijpeg benchmark            |

| A.8  | Average packet sizes for the ijpeg benchmark       |

| A.9  | Execution times for the xlisp benchmark            |

| A.10 | Average packet sizes for the xlisp benchmark       |

| A.11 | Execution times for the m88ksim benchmark          |

| A.12 | Average packet sizes for the m88ksim benchmark     |

| A.13 | Execution times for the perl benchmark             |

| A.14 | Average packet sizes for the perl benchmark90      |

| A.15 | Execution times for the vortex benchmark           |

| A.16 | Average packet sizes for the vortex benchmark      |

### LIST OF APPENDICES

####

#### CHAPTER 1

#### Introduction

To achieve higher levels of performance, processors are being built with wider issue widths and larger numbers of functional units. In the past ten years, instruction issue width has grown from one (MIPS R2000, Sun MicroSparc, Motorola 68020), to two (Intel Pentium, Alpha 21064) to four (MIPS R10000, Sun UltraSparc, Alpha 21164, PowerPC 604). This increase in issue width will continue as processors attempt to exploit even higher levels of instruction level parallelism. To effectively exploit the performance potential of such processors, instruction fetch rate must also increase. Because the average basic block size for integer programs is approximately five instructions, processors that aim to exploit higher levels of instruction level parallelism must be able to fetch multiple basic blocks each cycle.

### 1.1 The Basic Block Fetch Bottleneck

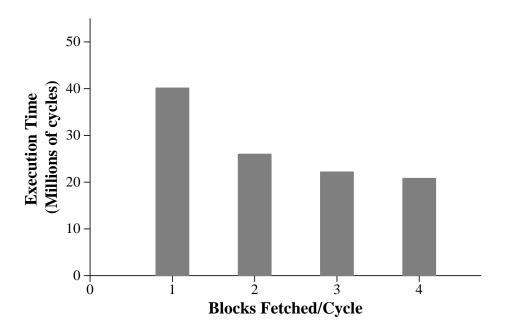

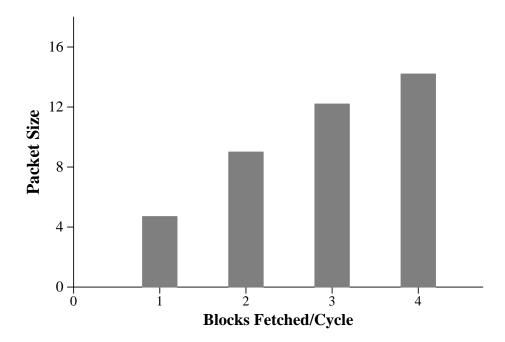

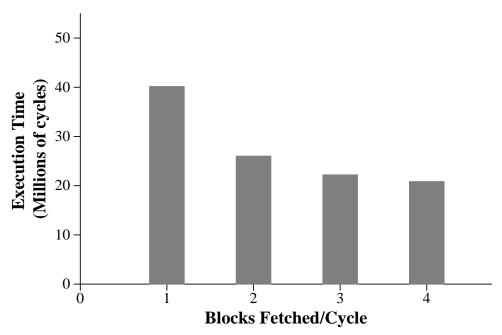

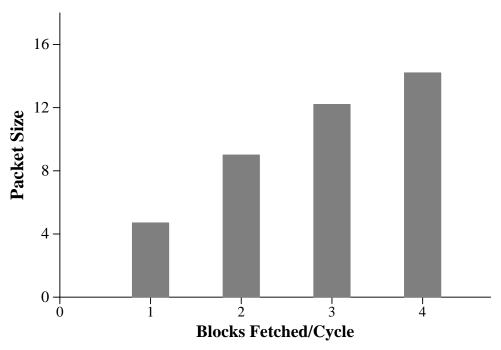

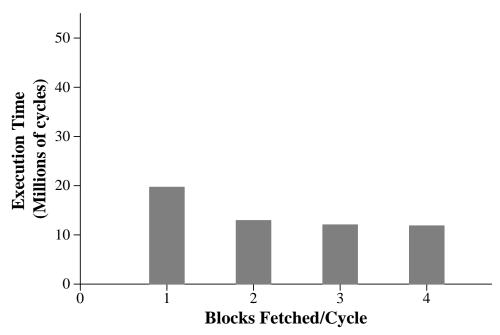

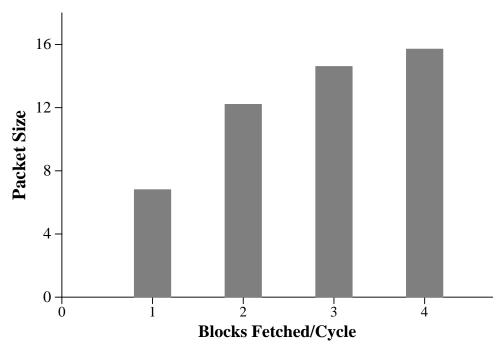

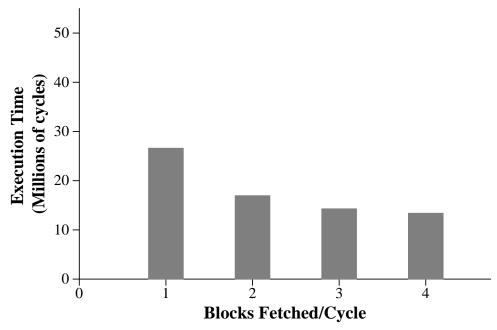

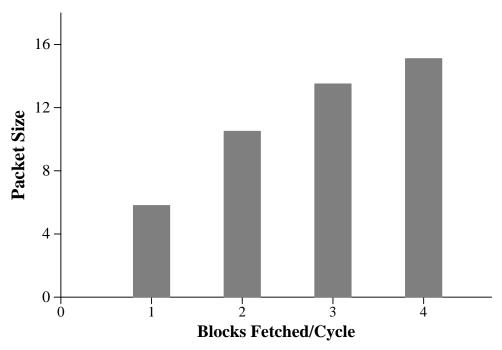

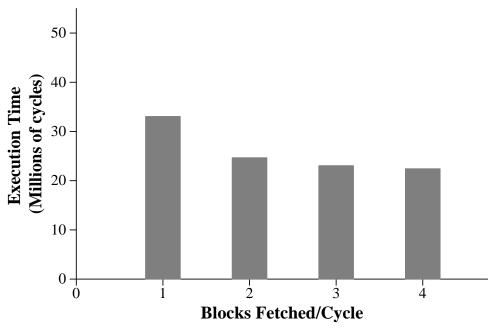

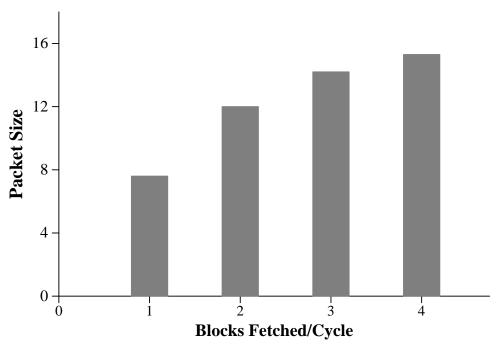

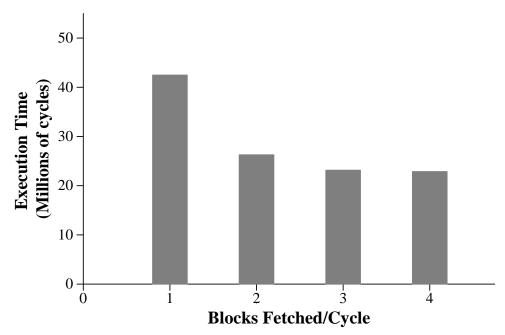

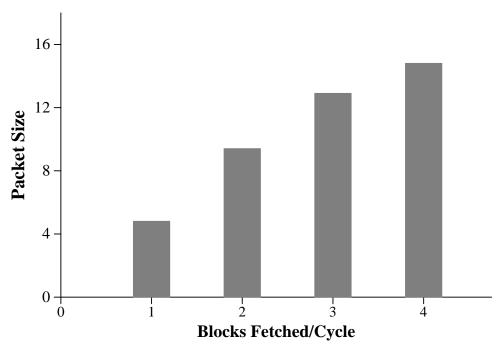

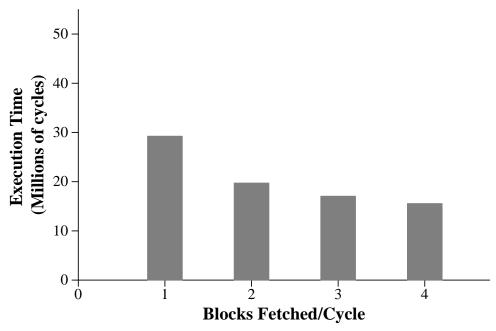

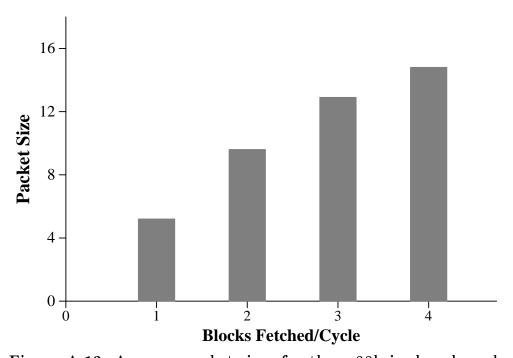

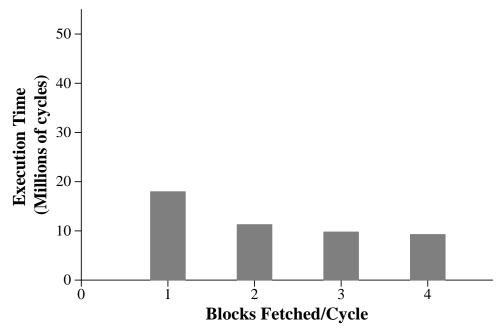

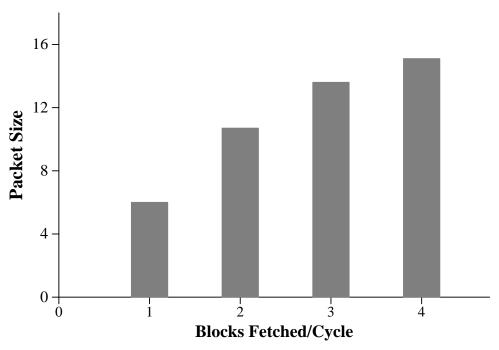

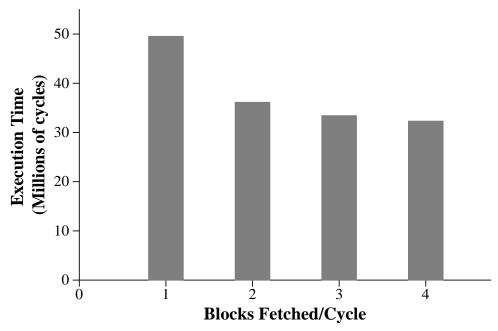

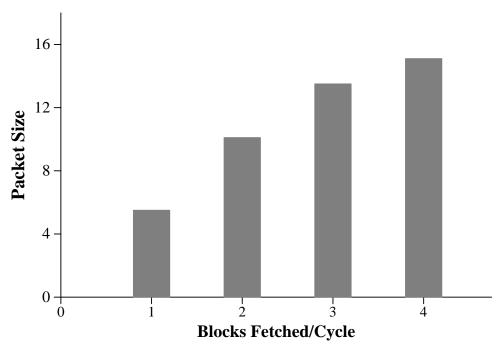

Figure 1.1 illustrates the importance of fetching multiple basic blocks per cycle for a wide issue machine. It plots the performance of the gcc benchmark from the SPECint95 benchmark suite for a sixteen wide issue, dynamically scheduled processor with perfect branch prediction. The number of blocks that the processor could fetch each cycle was varied from one to four. Increasing the number of blocks that could be fetched each cycle from one to two reduced the execution time by 35%. Increasing the number of fetched blocks from one to three reduced execution time by 45%. The reduction in execution time begins to tail off at three blocks per cycle because the processor was constrained to fetch at most sixteen instructions per cycle. Figure 1.2 shows the average number of instructions fetched per cycle (packet size) as the number of blocks that could be fetched was increased from one to four. Appendix A contains the corresponding figures for the seven other SPECint95 benchmarks.

Various approaches have been proposed for increasing instruction fetch rate from that of a single basic block per cycle. Some approaches [54, 10, 11, 45] extend the branch predictor and icache so that multiple branch predictions can be made each cycle and multiple, non-consecutive cache lines can be fetched each cycle. However, this extra hardware requires extra stages in the pipeline which will increase the branch misprediction penalty, decreasing performance. Other approaches [14, 22] statically predict the direction to be taken by a program's branches and then based on those predictions, use the compiler to arrange the blocks so that the multiple blocks to be fetched are always placed in consecutive memory

Figure 1.1: The performance of a sixteen wide issue processor executing the gcc benchmark as the number of blocks fetched per cycle is increased from one to four.

Figure 1.2: The average number of instructions fetched by a sixteen wide issue processor executing the gcc benchmark as the number of blocks fetched per cycle is increased from one to four.

locations. Although they eliminate the need for extra hardware, these approaches must rely on the branch predictions made by a static branch predictor which is usually significantly less accurate than those made by a dynamic branch predictor.

#### 1.2 The Block-Structured ISA Solution

To overcome the basic block fetch bottleneck, this dissertation presents a solution that uses block-structured ISAs. Block-structured ISAs exploit the advantages of both compiler-based and hardware-based solutions by merging basic blocks together at compile-time and providing support for dynamic branch prediction. Block-structured ISAs [31, 33, 32, 48, 19] are a new class of instruction set architectures that were designed to address the performance obstacles faced by processors attempting to exploit high levels of instruction level parallelism. The major distinguishing feature of a block-structured ISA is that it defines the architectural atomic unit (i.e. the instruction) to be a group of operations. These groups of operations are called atomic blocks. Each operation within the atomic block corresponds roughly to an instruction in a conventional ISA. This definition of the atomic block enables the block-structured ISA to simplify many implementation issues for wide-issue processors.

### 1.3 Thesis Statement

Block-structured ISAs increase the instruction fetch rate of a processor (and as a result, its performance) by enabling the compiler to combine separate basic blocks into a single, enlarged atomic block. By increasing the sizes of the blocks, the instruction fetch rate of the processor is increased without having to fetch multiple blocks each cycle. Furthermore, the semantics of the block-structured ISA enable the processor to use a dynamic branch predictor to predict the successor for each atomic block fetched. As a result, block-structured ISAs increase the instruction fetch rate without relying on extra hardware to fetch non-consecutive blocks out of the icache or foregoing the use of dynamic branch prediction.

### 1.4 Contributions

This dissertation makes two key contributions:

- 1. It demonstrates that a processor implementing a block-structured ISA can achieve a significantly higher instruction fetch rate than that achieved by a processor implementing a conventional ISA. This increase in instruction fetch rate translates to a 28% performance improvement when perfect branch prediction is assumed and a 15% performance improvement when real branch prediction is used.

- 2. It presents the design of a dynamic branch predictor for block-structured ISAs. It demonstrates how this predictor is able to achieve a prediction accuracy that is comparable to that of an aggressive dynamic branch predictor for a conventional ISA.

### 1.5 Dissertation Organization

This dissertation is organized into eight chapters. Chapter 2 discusses other approaches to increasing the instruction fetch rate. Chapter 3 describes the simulation methodology used throughout this dissertation. Chapter 4 gives an overview of block-structured ISAs, explaining how the block enlargement optimization works and how it increases the instruction fetch rate. Chapter 4 also defines the specific block-structured ISA studied in this dissertation. Chapter 5 evaluates the performance benefit of the block enlargement optimization, focusing on its ability to increase the average block size. It presents experimental results comparing the performance of the block-structured ISA to that of a conventional ISA. Chapter 6 describes the implementation of a dynamic branch predictor for block-structured ISAs. Chapter 7 evaluates the performance of this branch predictor as compared to an aggressive branch predictor for a conventional ISA. Chapter 7 also examines the block enlargement optimization's impact on branch prediction accuracy. Chapter 8 evaluates the performance benefit of the block enlargement optimization for scientific code. Chapter 9 presents concluding remarks and directions for future work.

#### CHAPTER 2

#### Related Work

The majority of the approaches previously proposed for increasing the instruction fetch rate can be divided into two categories, hardware-based and compiler-based. The hardware-based schemes extend the branch predictor and icache so that multiple branch predictions can be made each cycle and multiple non-consecutive cache lines can be fetched each cycle. They include the branch address cache [54], the collapsing buffer [10], the subgraph-level predictor [11], the multiple-block ahead branch predictor [45], and the trace cache [35, 44, 39]. The compiler-based schemes reorganize the program to increase the amount of work that can be fetched with a single icache access, eliminating the need for extra hardware. These schemes include trace and superblock scheduling [14, 4, 22], predicated execution [20, 42], hyperblock scheduling [29], the VLIW multi-way jump mechanism [13, 26, 12, 36], and multiscalar processors [15, 47].

### 2.1 Hardware-based Approaches

### 2.1.1 Predicting Multiple Branches Per Cycle

The branch address cache [54], the collapsing buffer [10], the subgraph-level predictor [11], and the multiple-block ahead branch predictor [45] are hardware schemes that propose different ways to extend the dynamic branch predictor so that it can make multiple branch predictions each cycle. Because some of the branches may be predicted to be taken, these schemes all require the ability to fetch multiple non-consecutive lines from the icache each cycle. They all propose to meet this requirement by interleaving the icache. This general approach has three disadvantages. First, bank conflicts will arise in the icache when fetching multiple lines from the same bank. To handle this conflict, the fetch for all but one of the conflicting lines must be delayed. This first disadvantage can be minimized if the icache is interleaved with a large enough number of banks. Second, because it is fetching multiple non-consecutive blocks from the icache, the processor must determine which instructions from the fetched cache lines correspond to the desired basic blocks and reorder the instructions so that they correspond to the order of those basic blocks. The processor will require at least one additional stage in the pipeline in order to accomplish these tasks. This additional stage will increase the branch misprediction penalty, decreasing overall performance. Third,

these approaches do not provide solutions to the problem of increased hardware complexity required to support wide issue widths. In particular, the hardware required to perform dependency checking, register file access, and architectural state maintenance increases as the issue width increases. If this problem is not addressed, then this increase in hardware complexity will result in increased cycle times or additional pipeline stages for an aggressive wide-issue machine, which in turn, will decrease performance.

#### 2.1.2 The Trace Cache

The trace cache [35, 44, 39] is a hardware-based scheme that does not require fetching non-consecutive blocks from the icache. Its fetch unit consists of three parts: a core fetch unit, a fill unit, and a trace cache. The core fetch unit fetches one basic block per cycle from the icache. The fill unit records sequences of basic blocks fetched by the core fetch unit, combining each sequence into a trace. These traces are then stored in the trace cache. If the branch predictor indicates that the sequence of basic blocks to be fetched matches a trace stored in the trace cache, then the processor is able to fetch multiple blocks that cycle by fetching the specified trace from the trace cache. Because the blocks have been combined into a contiguous trace, the processor need only fetch a single trace cache line to get all the blocks. In addition, because the blocks' instructions are stored in decoded form with their dependencies specified, the instructions fetched from the trace cache can bypass the pipeline stages that generate this information for instructions fetched from the icache. If no matching trace is found, the processor is able to fetch only one basic block that cycle via the core fetch unit. As long as the processor is fetching its instructions from the trace cache, the trace cache is an effective means for fetching multiple basic blocks each cycle without incurring the costs associated with the other hardware-based approaches.

The trace cache idea was originally proposed by Melvin, Shebanow, and Patt [35]. They proposed using the trace cache (or decoded instruction cache) to ease the instruction decoding bottleneck for HPS implementations of complex instruction sets such as the VAX. The core fetch unit fetched one instruction per cycle. The fill unit recorded the sequences of microoperations that were generated for each instruction. Each decoded instruction cache entry held the microoperations that corresponded to the set of instructions within a given basic block. Thus, a hit in the decoded instruction cache would result in the fetch and issue of an entire basic block's worth of instructions. Later, Melvin and Patt [34] suggested using the fill unit to combine instructions from different basic blocks. Rotenberg et al. [44] and Patel et al. [39] independently proposed implementations of the trace cache that combined basic blocks as suggested by Melvin and Patt. These two trace cache implementations showed significant performance improvements over previously proposed fetch mechanisms including the branch address cache and the collapsing buffer. The implementation proposed by Rotenberg et al. used the trace cache as the secondary fetch mechanism. The majority of the hardware was devoted to the icache. The implementation proposed by Patel et al. [39] used the trace cache as the primary fetch mechanism. By devoting more hardware to the trace cache, they showed that further performance improvements could be achieved. In addition, they showed that the trace cache works well even when compared to a single block fetch mechanism that uses an aggressive branch predictor.

### 2.2 Software-based Approaches

#### 2.2.1 Trace and Superblock Scheduling

Trace scheduling [14] and superblock scheduling [22, 4, 9] are compiler optimizations that enlarge the scope in which the compiler can schedule instructions. They use static branch prediction to determine the frequently executed program paths and place the basic blocks along these paths into consecutive locations, forming a superblock. The instructions within the superblock can then by optimized as if they were in a single basic block. Although the focus of superblock scheduling is to enlarge the scope in which the compiler can schedule instructions, it can also be used to increase the instruction fetch rate. Each superblock can be fetched in a single cycle because the basic blocks which form the superblock are contiguous.

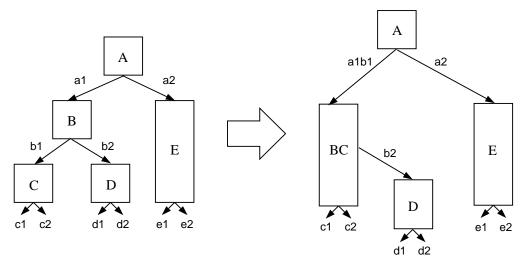

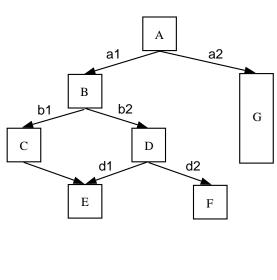

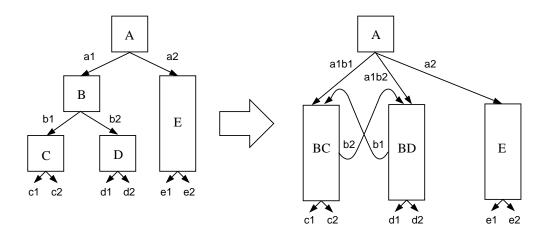

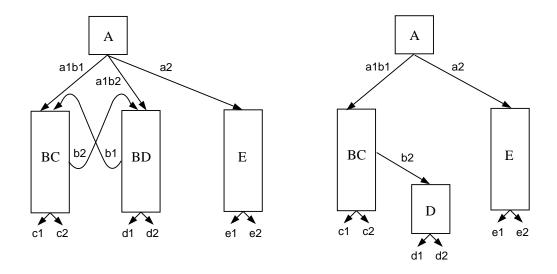

Figure 2.1 shows an application of the superblock optimization. The control flow graph on the left consists of basic blocks A–E. The control flow graph on the right is the result of applying superblock scheduling. The static branch predictor has predicted that block C is

Figure 2.1: Using superblock scheduling to combine basic blocks.

the most likely successor to block B so blocks B and C are combined to form a superblock. As a result, blocks B and C can be fetched in the same cycle. The disadvantage of this approach is that by optimizing blocks B and C as a single unit, block B cannot be fetched with any other block in a single cycle. Even if the processor knew that block D was the correct control flow successor to block B, the processor will still need two cycles to fetch blocks B and D. In effect, to fetch multiple basic blocks in a cycle, the processor must follow the static branch predictions used to form the superblocks. Because dynamic branch prediction is significantly more accurate than static branch prediction [53], using superblock scheduling to increase the instruction fetch rate will not be as effective as an approach that uses dynamic branch prediction to select the set of blocks to be fetched each cycle.

#### 2.2.2 Predicated Execution

A processor that supports predicated execution [2, 20, 43, 42] associates a predicate register with each instruction issued. The execution of an instruction proceeds normally if the predicate register resolves to a true value. The execution is suppressed if that predicate value resolves to a false value. Using predicated instructions, a compiler can eliminate branches in a program by converting the program control dependencies into data dependencies. By eliminating branches, predicated execution can improve performance because the processor will not have to suffer the branch execution penalty associated with those branches. In addition, predicated execution can increase the instruction fetch rate. Once a basic block's branch has been eliminated, it can be combined with its control flow successors to form one larger block. As a result, the processor can now fetch the original basic block along with its control flow successors in a single cycle. Figure 2.2 gives an example of this process. The branch at the end of block A is eliminated via predicated execution, resulting in the combination of blocks A, B, C, and D into a single block.

In contrast to its benefits, predicated execution has two disadvantages. First, it wastes fetch and issue bandwidth fetching and issuing instructions that are suppressed because their predicates evaluate to false. Second, by converting an instruction's control dependency into a data dependency, the program's critical paths may be lengthened. The processor must now wait for the new data dependency to be resolved instead of speculatively resolving the control dependency at fetch time. While predicated execution by itself may not be an effective mechanism for increasing fetch rate, it can provide a significant performance benefit when used in conjunction with speculative execution [28, 7] and other schemes for increasing fetch rate.

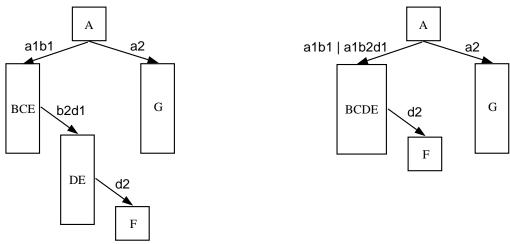

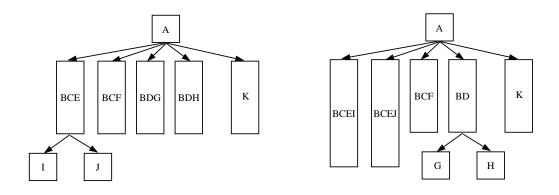

### 2.2.3 Hyperblock Scheduling

Hyperblock scheduling [29, 28] is an extension of superblock scheduling that incorporates predicated execution. As discussed earlier, the processor must always follow the static branch predictions used to form the superblock. If the branches inside a superblock are not highly biased, then using a static branch prediction will result in a low prediction accuracy for that branch. To avoid these mispredictions, hyperblock scheduling will use predicated execution to eliminate such branches. The highly biased branches are not eliminated because they can be accurately predicted by a static branch predictor. Figure 2.3 illustrates the difference between hyperblock and superblock scheduling. The control flow graph at the top shows basic blocks A-G where the branch in block B is slightly biased in the b1 direction and the branch in block D is highly biased in the d1 direction. The control flow graph on the bottom left is the result of applying superblock scheduling to the original control flow graph. Because the branch in block B is not highly biased, it will be frequently mispredicted by the static branch predictor. As a result, the processor will frequently fetch and issue blocks BCE and DE. The control flow graph on the bottom right is the result of applying hyperblock scheduling to the original control flow graph. Because the two frequently executed paths, BCE and BDE, are both included in the hyperblock BCDE, the processor will frequently fetch and issue only block BCDE. Block F will rarely have to be fetched after block BCDE because the branch in block D is highly biased in the d1 direction. By using predicated execution,

Figure 2.2: Using predicated execution to combine basic blocks.

Figure 2.3: Comparing superblock and hyperblock scheduling.

Figure 2.4: Building a VLIW tree instruction.

hyperblock scheduling is able to avoid many of the mispredictions incurred by superblock scheduling. However, because hyperblock scheduling uses predicated execution, it suffers the disadvantages of wasted fetch and issue bandwidth and increased critical path lengths that are associated with predicated execution. Hyperblock scheduling must be carefully controlled to ensure that this tradeoff results in a performance improvement.

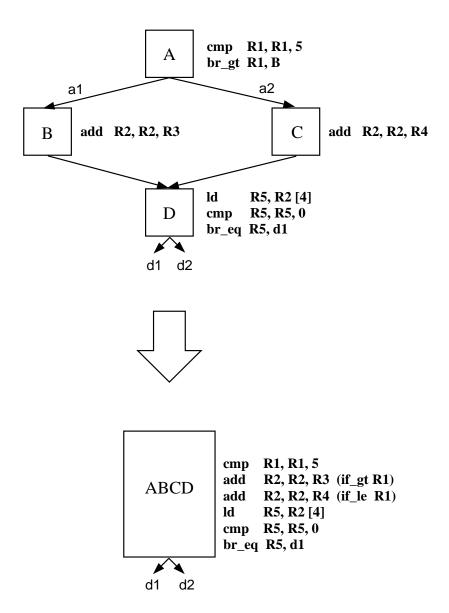

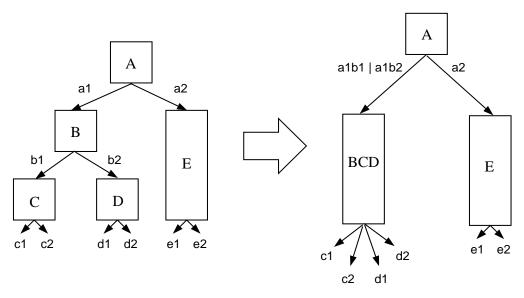

### 2.2.4 VLIW Multi-Way Jumps

The VLIW multi-way jump mechanism [13, 26, 12, 36] combines multiple branches from multiple paths in the control flow graph into a single branch. Using this mechanism along with predicated execution, basic blocks which form a rooted subgraph in the control flow graph can be combined into a single VLIW instruction, which is called a tree instruction. The branches for these basic blocks are combined into a single multi-way branch operation. The processor's condition code registers will specify which path through the rooted subgraph is to be executed (predicated execution is used to suppress the execution of operations from basic blocks not on this path) and which target of the multi-way branch operation is to be the next instruction. Figure 2.4 gives an example of how a tree instruction is formed. Blocks B, C, and D are combined into a single tree instruction. The figure assumes that all the instructions within B, C, and D are independent. When block BCD is issued into the processor, the direction taken by the branches in the original blocks B, C, and D will already be known. If block B's branch has taken the b1 direction and block C's branch has taken the c1 direction, then the execution of block D in BCD will be suppressed and the successor block that corresponds to block C's c1 direction will be the next block fetched. In this example, the direction taken by block D's branch is irrelevant because block D is not on the path of execution.

Because a single tree instruction can include operations from many basic blocks, this approach gives VLIW processors the means to fetch the equivalent work of multiple basic blocks each cycle. However, because the operations within a VLIW instruction must be

independent, it is critical that the compiler be able to find enough independent instructions to fill each VLIW instruction and be able to schedule the operations which evaluate the condition codes for the multi-way jump early enough so that the condition codes are available when the multi-way jump is issued. The compiler may have to delay the scheduling of certain operations in order to meet these requirements, lowering the instruction fetch rate of the processor.

#### 2.2.5 Multiscalar Processors

The multiscalar processing paradigm [15, 47] applies multiprocessor concepts to the design of microprocessors. A multiscalar processor consists of a set of processing elements connected in a ring. The multiscalar processor's compiler is responsible for dividing the program up into units of work, called tasks. These tasks are dynamically assigned to the processing elements for execution. The connecting logic among the processing elements detects and enforces the data dependencies among the tasks. This logic is the multiscalar counterpart for the cache coherency logic for shared memory multiprocessors except that it enforces not only dependencies among memory references from different processing elements, but dependencies among register references from different processing elements as well. Values are communicated among the processing elements via the ring network.

Multiscalar processors eliminate the problem of fetching multiple cache lines from the icache each cycle by associating a separate level one icache with each processing element. Each cycle, each processing element accesses its own level one icache for a single basic block. As long as each icache achieves a sufficient hit rate, the multiscalar processor as a whole is able to fetch the equivalent work of multiple basic blocks each cycle. However, the multiscalar model raises new performance issues not found in traditional wide-issue processors. To achieve high performance, it is important that the multiscalar compiler create tasks so that the workload is evenly balanced among the processing elements and that the communication among the tasks does not exceed the ring bandwidth

### CHAPTER 3

## Simulation Methodology

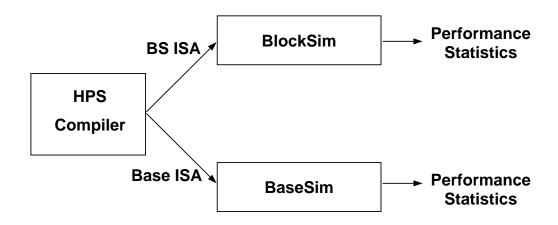

To evaluate the performance advantages of block-structured ISAs, the performance of an HPS implementation of a block-structured ISA is compared to an identically configured HPS implementation of a conventional (or base) ISA. The conventional ISA considered is the same load/store ISA that formed the basis of the block-structured ISA (see chapter 4.2). This ensures that the block-structured ISA has no architectural advantages over the conventional ISA with the exception of those due to block-structuring. Figure 3.1 gives an overview of how this comparison is performed. A compiler generates the block-structured and conventional ISA executables. These executables are passed to the simulators which model the corresponding HPS implementations and generate the performance statistics. This chapter details each component of the experimental setup.

### 3.1 The Compiler

I implemented a compiler that was targeted for both the block-structured and the conventional ISAs. This compiler is based on the Intel Reference C Compiler [24] with the back end appropriately retargeted. The Intel Reference C Compiler generates an intermediate representation of the program being compiled and applies the standard set of optimizations to that representation. The compiler back end takes this representation and applies a set of target-specific optimizations and allocates registers. By using the same core compiler for both ISAs, any unfair compiler advantages one ISA may have had over the other was eliminated.

### 3.2 The HPS Processor Model

The HPS paradigm [40, 41] is used to model the processor implementation in this study because it encompasses a set of microarchitectural techniques that are designed to achieve high performance for single instruction stream execution. These techniques include aggressive branch prediction, wide instruction issue, out-of-order execution, and precise exception handling and have been adopted by all currently introduced microprocessors [16, 17, 18].

The HPS implementations modeled issue sixteen instructions per cycle. This issue width was chosen for two reasons. First, because the current generation of microprocessors are

Figure 3.1: Experimental setup for comparing block-structured ISA performance to conventional ISA performance.

already issuing four instructions per cycle, sixteen wide issue is the minimum issue width that is aggressive enough to represent a design point far enough in the future to be considered research. Second, the block enlargement optimizations are designed to improve performance for wide-issue machines. They have little benefit for narrow issue widths. Using a generalized version of the Tomasulo algorithm [51], the instructions' registers are dynamically renamed in parallel and sent to an appropriate node table entry to await execution. An instruction is executed as soon as its source operands are ready and a functional unit is free. The HPS implementations modeled have 16 functional units with each functional unit capable of executing instructions from any instruction class. Table 3.1 lists the simulated latencies for each instruction class. After execution, an instruction's result is forwarded to the register file and to the other instructions awaiting execution in the node tables. An instruction is retired when its associated checkpoint [23] is retired. This occurs after all the instructions in the checkpoint have successfully executed and all previously issued checkpoints have been retired. The HPS implementations modeled can hold up to 32 checkpoints for a total of 256 instructions. The processor will stop fetching and issuing instructions if all 32 checkpoints are in use. This break in instruction fetch and issue is called a full-window stall. A full-window stall will continue until a checkpoint is retired (i.e. freed up for use). Unless otherwise noted, the level one icache size modeled was 128KB<sup>1</sup>. For the SPECint95 experiments, the level one dcache modeled was 16KB. The data requirements for the SPECint95 benchmarks are low enough so that using a small dcache has little effect on performance. For the SPECfp95 experiments, the level one dcache modeled was 128KB to handle the larger data requirements for the SPECfp benchmarks. The level two caches had six cycle access times and were modeled as perfect caches.

The same, aggressive HPS configuration was used for both the block-structured and conventional ISA processors. While, this guaranteed that neither ISA had a microarchitectural

<sup>&</sup>lt;sup>1</sup>A 128KB icache with a single cycle access time may appear aggressive compared to currently available microprocessor designs. However, advances in process technology will make such icaches possible in the future. Digital has already announced the 21264 Alpha processor which has a 64KB, two-way set associative icache with a single cycle access time [18].

| Class      | Latency | Description                                 |

|------------|---------|---------------------------------------------|

| Integer    | 1       | INT add, sub and logic OPs                  |

| FP Add     | 3       | FP add, sub, and convert                    |

| FP/INT Mul | 3       | FP mul and INT mul                          |

| FP/INT Div | 8       | FP div and INT div                          |

| Load       | 2       | Memory loads                                |

| Store      | -       | Memory stores                               |

| Bit Field  | 1       | Shift and bit testing                       |

| Branch     | 1       | Trap, fault, and other control instructions |

Table 3.1: Instruction classes and latencies.

advantage over the other, this constraint ignored the hardware advantages of block-structured ISAs. As mentioned in chapter 4, block-structured ISAs simplify the hardware required to implement wide-issue processors. If this advantage were to be exploited, then for a fixed hardware cost, the block-structured ISA processor would have either a faster cycle time or a wider issue width than that of the conventional ISA processor.

### 3.3 The Simulators

Two trace-driven simulators were implemented to measure the performance of the conventional and block-structured ISAs, BaseSim and BlockSim. Both simulators were divided into two parts, a front end and a back end. The front ends were responsible for actually executing the specified executable and generating an instruction trace that corresponded to the correct execution of that executable. The back ends were responsible for modeling the microarchitectural components of the processor in order to determine the performance achieved by the specified HPS implementation while executing the instruction trace. The microarchitectural components modeled included the branch predictor, the node tables, the functional units, the distribution buses, the register files and renaming logic, and the caches.

The instruction trace generated by BaseSim's front end included only instructions that were on the correct path of execution. By excluding instructions from incorrect speculative (or wrong) paths, BaseSim was unable to model the effects of issuing such instructions into the machine [3, 25]. However, the execution penalty associated with the mispredicted branch that created the incorrect speculative path is still correctly modeled. When a branch misprediction occurs in a real machine, the processor continues to fetch instructions from the wrong path until the mispredicted branch is resolved. At that time, the architectural state of the processor is restored to its state at the point of the mispredicted branch, the instructions issued from the wrong path are removed from the node tables, and the processor begins fetching instructions from the correct path. When a branch misprediction occurs in the simulator, the simulator simply stalls the instruction fetch mechanism until the branch is resolved. By stalling, the simulator mimics the effect of not fetching and issuing useful work during this time without having to actually fetch and issue instructions from the incorrect path. After the mispredicted branch is resolved, the simulator restarts instruction fetch from

the correct path, which is the next instruction in the instruction trace.

To accurately model branch misprediction penalties for a processor implementing a block-structured ISA, the simulator must take into account the effect of wrong path instructions for certain branch mispredictions (see chapter 4.1.4 for more details). As a result, the instruction trace generated by BlockSim's front end must include the wrong path instructions that occur after these specific branch mispredictions. To accomplish this, BlockSim's back end communicates its branch predictions to the front end so that the front end knows when a branch misprediction will occur and includes the appropriate instructions in the instruction trace.

#### 3.4 The SPEC95 Benchmarks

The SPEC benchmarks [49] were used to evaluate the performance of the block-structured and conventional ISAs. Tables 3.2 lists the eight SPECint95 used along with their test and training data sets. The test data sets were used to generate the performance numbers reported. The training sets were used to generate the benchmark profiles for the experiments that required profiling. The test and training data sets were all either the reference data sets provided with the SPEC benchmarks or modified versions of those data sets. Table 3.3 lists the ten SPECfp95 benchmarks used along with their test data sets. The table does not include a listing of training data sets because profiling was not used for the SPECfp benchmarks. Modified data sets were used for both the SPECint95 and SPECfp95 benchmarks whenever the running time for the reference data set was too long. Appendices B and C give descriptions of the modified data sets used.

| Benchmark | Description                   | Test Set                | Training Set                  |

|-----------|-------------------------------|-------------------------|-------------------------------|

| gcc       | GNU C compiler                | jump.i                  | ${ m stmt.i}$                 |

| compress  | Data compression program      | $30 \mathrm{KB.in^*}$   | $300 \mathrm{B.in^*}$         |

| go        | Go-playing program            | 2stone $9.$ in          | null.in                       |

| ijpeg     | Image compression program     | specmun.ppm             | vigo.ppm                      |

| li        | Xlisp interpreter             | boyer.lsp               | queens.lsp                    |

| m88ksim   | Simulator for 88100 processor | $\operatorname{dcrand}$ | dhry                          |

| perl      | Perl interpreter              | $_{ m scrabbl.pl}$      | primes.pl                     |

| vortex    | Object-oriented database      | ${\rm test.in^*}$       | $\operatorname{profile.in}^*$ |

Table 3.2: The SPECint95 benchmarks and their test and training data sets. \* indicates the input set is an abbreviated version of the SPECint95 reference input set.

| Benchmark     | Description                          | Test Set                      |

|---------------|--------------------------------------|-------------------------------|

| tomcatv       | Mesh generation                      | tomcatv.in                    |

| swim          | Shallow water equation solver        | swim.in                       |

| su2cor        | Monte Carlo method for particle      | $\mathrm{su}2\mathrm{cor.in}$ |

|               | mass computation                     |                               |

| hydro2d       | Navier Stokes equation solver        | hydro2d.in                    |

| mgrid         | 3D multigrid solver                  | $\operatorname{mgrid.in}$     |

| applu         | Partial differential equation solver | applu.in                      |

| ${ m turb3d}$ | Turbulence modeling                  | ${ m turb 3d.in}$             |

| apsi          | Weather modeling                     | $\operatorname{apsi.in}$      |

| fpppp         | Quantum chemistry problem            | fpppp.in                      |

| wave5         | Maxwell's equations solver           | wave 5. in                    |

Table 3.3: The SPECfp95 benchmarks and their test data sets. All the test data sets used were abbreviated versions of the SPECfp95 reference input sets.

### CHAPTER 4

## Block-Structured ISAs and the Block Enlargement Optimization

Block-structured ISAs [31, 33, 32, 48] were designed to help solve performance obstacles faced by wide issue processors. Their major distinguishing feature is that the architectural atomic unit is defined to be a group of operations, where an operation typically corresponds to an instruction in a load/store architecture. These groups, known as atomic blocks, are specified by the compiler. When an atomic block is issued into the machine, either every operation in the block is executed or none of the operations in the block are executed. The semantics of the atomic block enable the block-structured ISA to explicitly represent the dependencies among the operations within a block and to list the operations within the block in any order without affecting the semantics of the block. These features simplify the implementation of a wide issue processor by simplifying the logic required for recording architectural state, checking dependencies, accessing the register file, and routing operations to the appropriate reservation stations. By reducing hardware complexity, wide issue implementations of a block-structured ISA will require fewer hardware resources than that of a wide issue implementation of a conventional ISA, resulting in a faster cycle time or a shallower pipeline. While these benefits are critical to building wide issue processors, this dissertation focuses on the ability of block-structured ISAs to increase the instruction fetch rate. This chapter will describe the block enlargement optimization, a compiler optimization used by block-structured ISAs to increase the instruction fetch rate and the details of the specific block-structured ISA that will be studied throughout this dissertation.

### 4.1 The Block Enlargement Optimization

#### 4.1.1 Overview

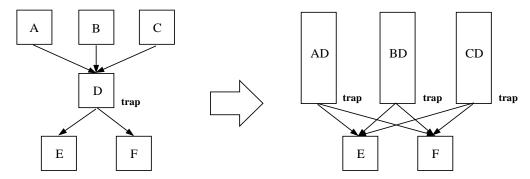

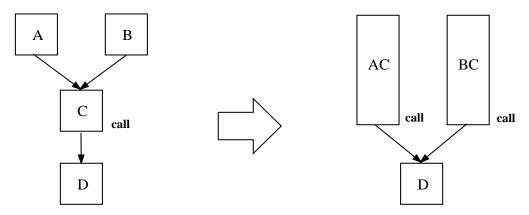

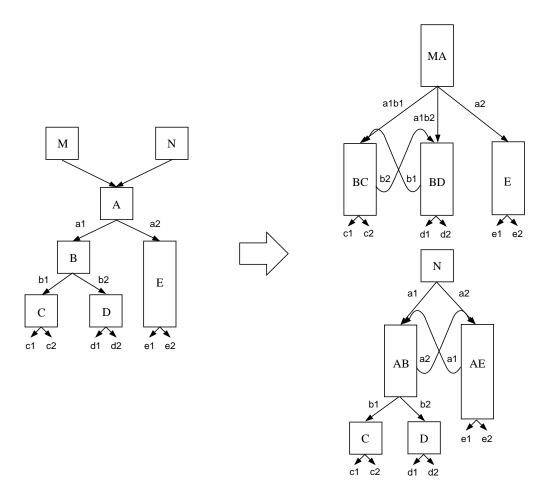

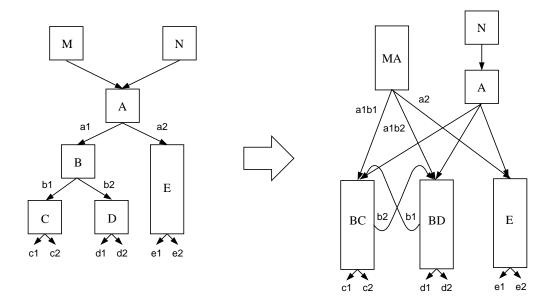

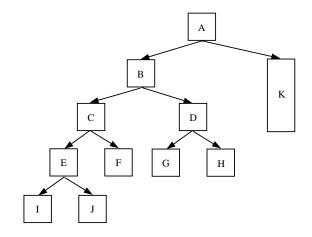

The block enlargement optimization increases the size of an atomic block by combining the block with its control flow successors. Figure 4.1 illustrates how block enlargement works. The control flow graph on the left consists of the atomic blocks A–E, each one ending with a branch that specifies its two successor blocks. These branches are called trap operations to differentiate them from fault operations which will be described below. These blocks are analogous to the basic blocks in a control flow graph for a conventional ISA. The control

Figure 4.1: Combining atomic blocks into an enlarged atomic block.

flow graph on the right shows the result of combining atomic block B with its control flow successors C and D to form the enlarged atomic blocks BC and BD. Both blocks BC and BD are now control flow successors to block A.

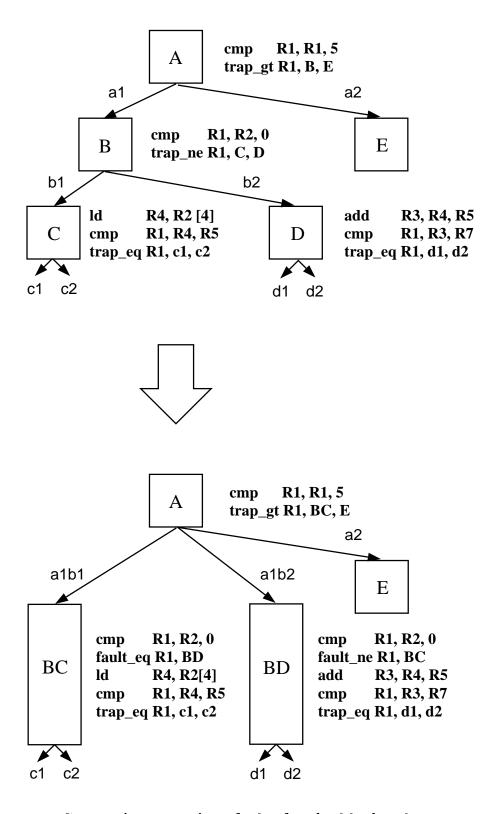

To support the block enlargement optimization, a new class of branch operations, the fault operation, is included in block-structured ISAs. The fault operation takes a condition and a target. If the condition evaluates to false, the fault operation has no effect. If the condition evaluates to true, the instructions from the atomic block to which it belongs are discarded and the instruction stream is redirected to its target. When two blocks are combined, the trap operation at the end of the first block is converted into a fault operation. If a block is combined with its fall-through successor, then the condition of the resulting fault operation is the same as the original trap operation's condition. If a block is combined with the target of its trap operation, then the condition of the resulting fault operation is the complement of the original trap operation's condition. The target of the fault operation is the enlarged block that results from combining the first block with its other control flow successor. In figure 4.1, when blocks B and C are combined, the trap at the end of B is converted into a fault in block BC. The fault's condition is true whenever block D is suppose to follow block B in the dynamic instruction stream and the fault's target is BD. Block BD contains a corresponding fault operation with a complementary condition and a target that points back to BC. Figure 4.2 shows this transformation using sample code sequences for blocks A—D.

Enlarging atomic blocks changes the way a processor sequences through a control flow graph because the control flow edges traversed are no longer solely determined by the operations that precede it. Enlarging an atomic block causes multiple branches to be placed in a single block. Referring back to figure 4.2, enlarged blocks BC and BD both contain two branches, the fault operation which corresponds to the original trap at the end of B and the trap operation at the end of C or D. This results in block A having three control flow successors, blocks BC, BD, and E. Block A's correct control flow successor is specified by not only the direction taken by block A's trap operation, but by the direction taken by block B's branch (i.e. the fault operations in BC and BD). Because the operations that evaluate block B's condition may be in B itself, the correct successor to A cannot be determined until

Figure 4.2: Converting traps into faults for the block enlargement optimization.

Figure 4.3: Comparing the block enlargement optimization to superblock scheduling.

after BC or BD has been issued. To arrive at the correct successor, a successor candidate must be chosen that is a possible successor given the current trap condition. If block A's trap indicates that control flow edge a1 is to be taken, blocks BC or BD can be chosen as the successor candidate. In effect, block A's trap serves only to partition the control flow successors into two subsets, the taken subset and the not taken subset. It does not specify exactly which control flow successor is the correct one. The processor must then depend on the faults within the chosen successor block to redirect control to the correct successor block as previously described.

Figure 4.3 contrasts the difference between the block enlargement optimization and superblock scheduling. Starting with the original control flow graph found on the left sides of figures 2.1 and 4.1, the control flow graph on the left side of figure 4.3 is the result of applying the block enlargement optimization. The control flow graph on the right is the result of applying superblock scheduling. There are two key differences. First, the block enlargement optimization gives the processor the opportunity to fetch either blocks B and C together in a single cycle or blocks B and D together in a single cycle. Superblock scheduling allows only blocks B and C to be fetched together. For the block enlargement case, the dynamic branch predictor can be used to predict every branch in the program. For the superblock case, the dynamic branch predictor can be used to predict only the branches that end superblocks. Predictions for branches that reside inside a superblock are constrained to be the static branch predictions used to form the superblocks. Because dynamic branch predictors usually achieve significantly higher prediction accuracies than static branch predictors, this extra degree of freedom provides a performance advantage for the block enlargement optimization over superblock scheduling. Second, mispredicting a branch inside an enlarged block (i.e. a fault operation) incurs an extra penalty not associated with ordinary branch mispredictions, because it causes all the work in that block to be discarded. Some of this

Figure 4.4: Using block enlargement to increase the compiler's scope for local optimization.

work may have to be issued and executed again after the correct block is fetched. For example, in figure 4.3, if block BC is fetched and issued and its fault operation fires, then the entire block will be discarded and block B will have to be fetched and issued again in the form of block BD. For a misprediction of a branch inside a superblock, the entire superblock is not discarded, just the work that follows the mispredicted branch. Referring again to figure 4.3, if block BC is fetched and issued and the branch inside the block redirects the control flow to block D, block C is suppressed but block B remains in the machine.

Using the block enlargement optimization, block-structured ISAs are able to increase the instruction fetch rate without suffering the disadvantages associated with traditional approaches — the need to fetch multiple non-consecutive cache lines each cycle and the constraint of having to use static branch prediction instead of dynamic branch prediction for certain select branches in the program.

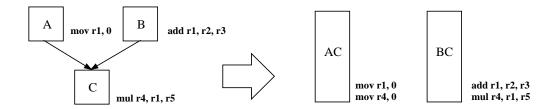

### 4.1.2 Enlarging the Compiler's Scope for Optimization

In addition to increasing the instruction rate, the block enlargement optimization also increases the compiler's scope for local optimization in the same manner as is done in trace scheduling [14] and superblock scheduling [22]. Compiler optimizations can be divided into two classes: local and global [1]. Local optimizations are optimizations that are performed upon instructions that reside within a single block. They are narrow in focus. Global optimizations are optimizations that are performed across multiple basic blocks. By considering a wider scope, global optimizations can find opportunities for improving the code beyond what is done by local optimizations. However, when applying a global optimization across a set of basic blocks, the compiler must ensure that the optimization does not cause incorrect results or increase the execution time for any path the program may take through those basic blocks. Consider the control flow graph on the left side of figure 4.4. If the program's path of execution is assumed to proceed from block A to block C, then the instruction mul r4, r1, r5 in block C can be optimized to mov r4, 0. However, if the program's path of execution was to proceed from block B to block C, this optimization would cause incorrect results.

When a set of basic blocks are combined together into a single enlarged block via the block enlargement optimization, that set of basic blocks becomes an atomic unit and can be treated as a single basic block. Thus the compiler can apply optimizations to that set of blocks as if the optimizations were local optimizations. The compiler no longer has to

worry about the optimizations' effects on the different program paths through the set of basic blocks. Consider the control flow graph on the right side of figure 4.4, the result of applying the block enlargement optimization to the control flow graph on the left. The mul r4, r1, r5 from block C has been optimized to mov r4, 0 for block AC while remaining in its original form in block BC. If the program's path of execution were to proceed from block A to block C, enlarged block AC would be issued into the machine. If the path of execution were to proceed from block B to block C, enlarged block BC would be issued into the machine. In either case, the best possible version of block C is issued into the machine.

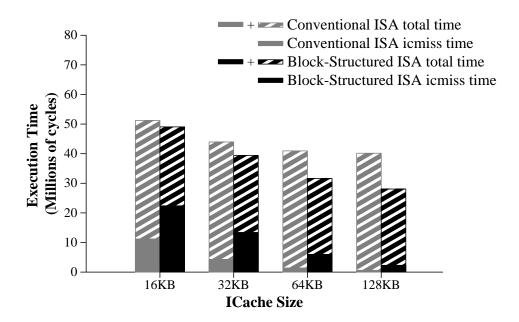

#### 4.1.3 Effect on ICache Performance

In addition to the average block size, the icache hit rate is another important factor that determines the instruction fetch rate. For the block enlargement optimization to be effective, it must increase the average block size without significantly reducing icache performance. Because it increases the size of the executable, the block enlargement optimization may have a negative effect on icache hit rate. Each time a block is combined with its successors, a separate copy of that block is created for each successor. In figure 4.1, combining block B with it's successors C and D resulted in the creation of an extra copy of B. This duplication may increase the number of icache capacity misses during program execution and lower performance. This will be the case if all the enlarged blocks formed from combining the block with its successors are accessed with sufficient frequency. On the other hand, if an enlarged block is never accessed, then it is never brought into the icache. The duplication incurred by such a block has no effect on the icache miss rate or the memory bandwidth used by the icache. The block enlargement optimization must be controlled so that the degree of block enlargement is balanced against the increase in the program's icache space requirements.

#### 4.1.4 Simulation Concerns

As mentioned in chapter 3.3, for a simulator to accurately model branch misprediction penalties for a processor implementing a block-structured ISA, the simulator must take into account the effect of wrong path instructions. The instructions that compute a fault operation's condition may be in the same block as the fault itself. If such a fault is mispredicted, the only way to determine the amount of time required to resolve the fault is to issue the atomic block within which it resides and this block, by definition, is on the wrong path. Consider the enlarged block control flow graph in figure 4.2 on page 4.2. Suppose the correct successor to block A is block BD, but the simulated branch predictor has mispredicted the successor block to be block BC, that is, the fault operation in block BC has been mispredicted. This misprediction will be resolved when block BC's fault operation is executed and thus block BC must be issued into the simulated machine. To correctly model the machine's behavior in this situation, the instruction trace generated by BlockSim's front end will include the instructions in block BC that originally came from block B. The simulator will then stall instruction fetch until the mispredicted fault operation is resolved. Because BlockSim's front end does not proceed any further down the wrong path than the first block, the effect of executing instructions from the wrong path is only partially modeled by BlockSim.

### 4.2 Specification of a Block-Structured ISA

#### 4.2.1 The Base ISA

To explore the performance advantages of block-structured ISAs, I have defined a specific block-structured ISA that incorporates a subset of the features described above. This ISA's architectural unit is the atomic block. The operations that can be found in an atomic block were taken from a subset of the MC88000 ISA [37]. All the non-control flow operations and indirect branches were taken directly from the MC88000 ISA. Added to this core set of operations were the trap, fault, and subroutine call operations. Each atomic block can contain up to sixteen operations, the issue width of the machine <sup>1</sup>. In addition, each atomic block must contain exactly one trap, subroutine call, or indirect branch operation to specify the control flow successor for that block.

#### 4.2.2 Trap Operations