# Power Driven Microarchitecture Workshop

in Conjunction with ISCA 98 Barcelona, Spain

Sunday, June 28, 1998

Organizers: Dirk Grunwald, University of Colorado Srilatha (Bobbie) Manne, University of Colorado Trevor Mudge, University of Michigan

# **Table of Contents**

| Introduction1                                                                 |

|-------------------------------------------------------------------------------|

| Bus Transition Activity Session                                               |

| Reducing the Energy of Address and Data Buses with the Working-Zone           |

| Encoding Technique and its Effect on Multimedia Applications                  |

| Enric Musoll, Tomas Lang, and Jordi Cortadella                                |

| Reduced Address Bus Switching with Gray PC9                                   |

| Forrest Jensen and Akhilesh Tyagi                                             |

| Instruction Scheduling for Low Power Dissipation in High Performance          |

| Microprocessors14                                                             |

| Mark C. Toburen, Thomas M. Conte, and Matt Reilly                             |

| Code Transformations for Embedded Multimedia Applications: Impact on          |

| Power and Performance                                                         |

| N. Zervas, K. Masselos and C.E. Goutis                                        |

| Modeling Inter-Instruction Energy Effects in a Digital Signal Processor       |

| Ben Klass, Don Thomas, Herman Schmit, and David Nagle                         |

| Power Issues in the Memory Subsystem                                          |

|                                                                               |

| Split Register File Architectures for Inherently Low Power Microprocessors    |

| V. Zyuban and P. Kogge                                                        |

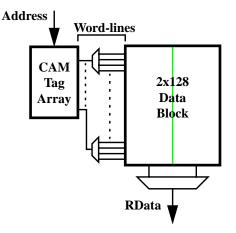

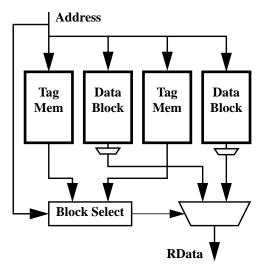

| Energy Efficient Cache Organizations for Superscalar Processors               |

| Kanad Ghose and Milind Kamble                                                 |

| Power and Performance Tradeoffs Using Various Cache Configurations            |

| A New Scheme for I-cache Energy Reduction in High-Performance Processors      |

| Nikos Bellas, Ibrahim Hajj and Constantine Polychronopoulos                   |

| Low-Power Design of Page-Based Intelligent Memory                             |

| Mark Oskin, Frederic T. Chong, Aamir Farooqui, Timothy Sherwood,              |

| and Justin Hensley                                                            |

| Power Reduction by Low-Activity Data Path Design and SRAM Energy Models       |

| Mir Azam, Robert Evans, and Paul Franzon                                      |

| Cache-in-Memory: A Low Power Alternative?67                                   |

| Jason Zawodny, Eric W. Johnson, Jay Brockman, and Peter Kogge                 |

| Innovative VLSI Techniques for Power Reduction                                |

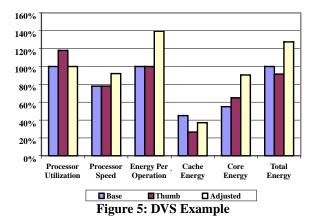

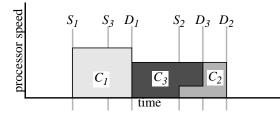

| Dynamic Voltage Scaling and the Design of a Low-Power Microprocessor System74 |

| Trevor Pering, Tom Burd, and Robert Broderson                                 |

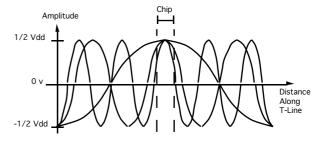

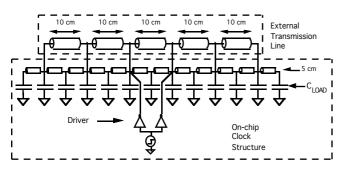

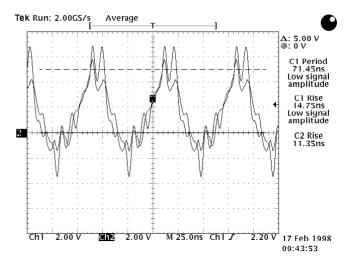

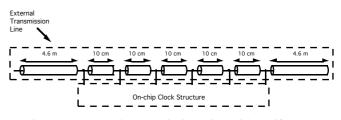

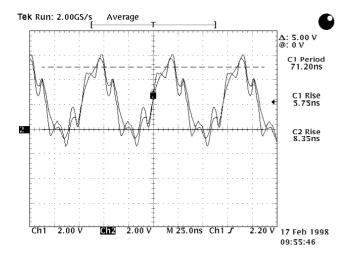

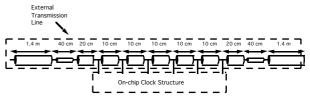

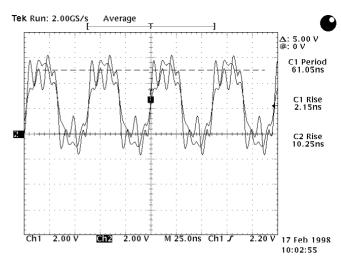

| Transmission Line Clock Driver                                                |

| Matthew Becker and Thomas Knight, Jr.                                         |

| Architectural Power Reduction and Power Analysis                                   | 86  |

|------------------------------------------------------------------------------------|-----|

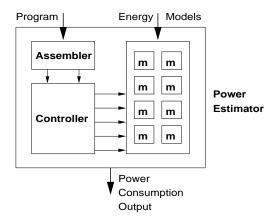

| An Architectural Level Power Estimator                                             | 87  |

| Rita Yu Chen, Mary Jane Irwin, and Raminder S. Bajwa                               |     |

| Multivariate Power/Performance Analysis For High Performance Mobile                |     |

| Microprocessor Design                                                              | 92  |

| George Z.N. Cai, Kingsum Chow, Tosaku Nakanishi, Jonathan Hall<br>and Micah Barany |     |

| Power-Aware Architecture Studies: Ongoing Work at Princeton                        | 98  |

| Christina Leung, David Brooks, Margaret Martonosi, and Douglas Clark               |     |

| Architectural Tradeoffs for Low Power                                              | 102 |

| Vojin G. Oklobdzija                                                                |     |

| The Inherent Energy Efficiency of Complexity-Adaptive Processors<br>David Albonesi | 107 |

| Function Unit Power Reduction                                                      | 113 |

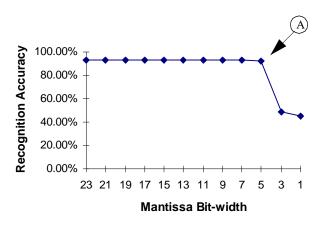

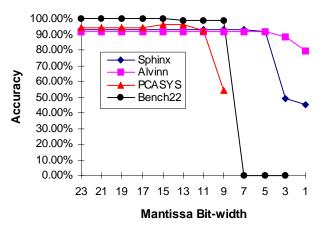

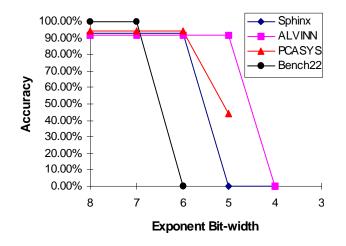

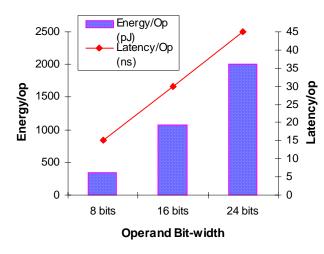

| Minimizing Floating-Point Power Dissipation via Bit-Width Reduction                | 114 |

| Ying-Fai Tong, Rob Rutenbar, and David Nagle                                       |     |

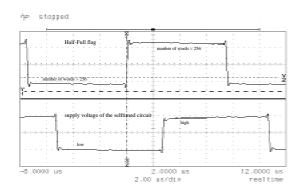

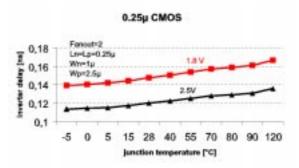

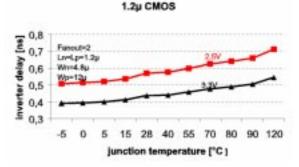

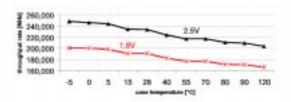

| A Power Management for Self-Timed CMOS Circuits (FLAGMAN) and                      |     |

| Investigations on the Impact of Technology Scaling                                 | 119 |

| Thomas Schumann , Ulrich Jagdhold, and Heinrich Klar                               |     |

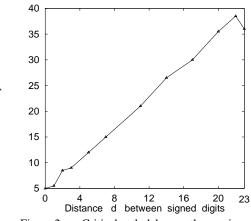

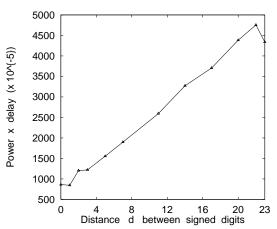

| Hybrid Signed Digit Representation for Low Power Arithmetic Circuits               | 124 |

| D. Phatak, Steffen Kahle, Hansoo Kim, and Jason Lue                                |     |

| Alternative Architectures                                                          | 130 |

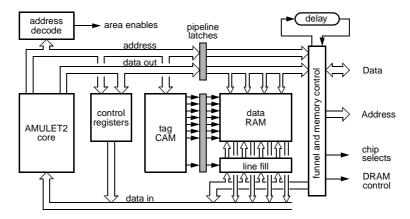

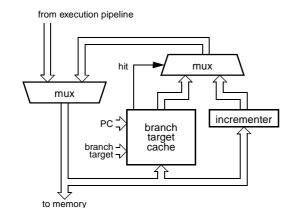

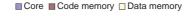

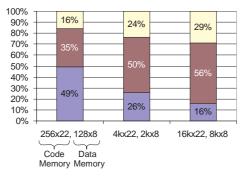

| Power-Saving Features in AMULET2e                                                  | 131 |

| S.B. Furber, J.D. Garside, and S. Temple                                           |     |

| A Fully Reversible Asymptotically Zero Energy Microprocessor                       | 135 |

| Carlin Vieri, M. Josephine Ammer, Michael Frank,                                   |     |

| Norman Margolus and Tom Knight                                                     |     |

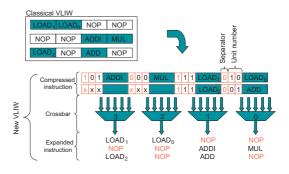

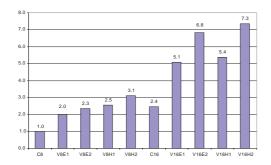

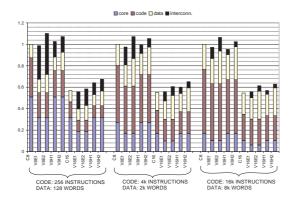

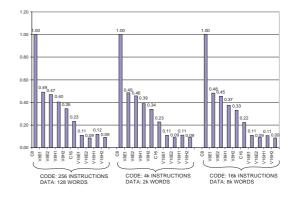

| Low-Power VLIW Processors: A High-Level Evaluation                                 | 140 |

| Jean-Michel Puiatti, Christian Piguet, Josep Llosa,                                |     |

| and Eduardo Sanchez                                                                |     |

| Designing the Low-Power M*CORE <sup>TM</sup> Architecture                          | 145 |

| Jeff Scott, Lea Hwang Lee, John Arends, and Bill Moyer                             |     |

|                                                                                    |     |

| Author Index                                                                       | 151 |

|                                                                                    |     |

# **Power-Driven Microarchitecture Workshop**

# Introduction

In recent years, reducing power dissipation has become a critical design goal for many microprocessors due to portability and reliability requirements. Most of the power reduction was achieved through supply voltage reduction and process shrinks. However, there is a limit to how far supply voltages may be reduced, and the power dissipated on-chip is increasing even as process technology improves. Further advances will require not only circuit and technology improvements but new ideas in microarchitecture. This will be true not only for the obvious situation of portable computers but also for high-performance systems. It was the goal of the Power-Driven Microarchitecture Workshop to provide a forum for examining innovative architectural solutions to the power problem for processors at all levels of performance.

The Power-Driven Microarchitecture Workshop was held in conjunction with the ISCA98 conference. The response to the call for papers was outstanding, enabling us to assemble an strong program of over two dozen papers. Three invited speakers, Mark Horowitz of Stanford, and Vivek Tiwari and Doug Carmean from Intel provided a brief tutorial introduction to power issues in VLSI design, and covered existing problems and solutions in the microprocessor market. The purpose of these tutorials was to establish common ground for discussing power issues in processor design.

It is our hope that, as a result of this workshop, the level of awareness will have been raised in the architecture community about issues related to power dissipation and energy consumption. We further hope that this heightened awareness will lead to exciting new research in the area.

Dirk Grunwald Bobbie Manne Trevor Mudge

# **Bus Transition Activity**

# Reducing the Energy of Address and Data Buses with the Working-Zone Encoding Technique and its Effect on Multimedia Applications \*

**Enric Musoll**

Cyrix

(National Semiconductor Corp.) Santa Clara, CA 95052 enric@cyrix.com

Tomás Lang Dept. of Electrical and Computer Eng. University of California at Irvine Irvine, CA 92697 tomas@ece.uci.edu

Jordi Cortadella Dept. of Software

Universitat Politècnica de Catalunya

08071 Barcelona, Spain

jordic@lsi.upc.es

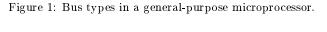

(or multiplexed data bus) Address I Data bus generator Memory Load/Store D Data bus unit unit ROM  $2^n$ I Address bus Execution D Address bus core D Cache I Cache (or ultiplex address bus)

# Abstract

The energy consumption due to I/O pins is a substantial part of the overall chip consumption. This paper gives an overview of the Working Zone Encoding (WZE) method for encoding for low power the external address and data buses, based on the conjecture that programs favor a few working zones of their address space at each instant. In such cases, the method identifies these zones and sends through the address (data) bus only the offset of this reference (data value) with respect to the previous reference (data value) to that zone, along with an identifier of the current working zone. This is combined with a one-hot encoding for the offset.

The paper then focuses on preliminary work on the following two topics:

- reduction of the effect of the WZE delay on the bus access time by overlapping this delay with the virtual to physical address translation. Although the modification to allow this overlapping might increase the bus energy, simulations of the SPEC benchmarks indicate that for a page size of 1 KB or larger the effect is negligible.

- extension of the technique for the data bus to some multimedia applications which are characterized by having packed bytes in a word. For two typical applications, the data-only data bus and data-only address bus I/O activity is reduced by 74% and 51% with respect to the unencoded case, and by 68% and 33% with respect the best of the rest of the encoding techniques.

#### 1 Introduction

The I/O energy is a substantial fraction of the total energy consumption of a microprocessor [4], because the capacitance associated with an external pin is between one hundred and one thousand times larger than that corresponding to an internal node. Consequently, the total energy consumption decreases by reducing the number of transitions on the high-capacitance, off-chip side, although this may

come at the expense of some additional transitions on the low-capacitance, on-chip side.

For a microprocessor chip, the main I/O pins correspond to the address and data buses. In this work, we consider an encoding to reduce the activity in both of these buses. If the value carried by n bits has to be transmitted over a bus, a reduction in the switching activity of this bus may be obtained at the cost of extra hardware in the form of an encoder on the sender device, a decoder on the receiver device, and potentially a larger number of wires m.

In [10] and [11] we have presented the Working-Zone Encoding (WZE) method, which is based on the conjecture that applications favor a few working zones of their address space. Moreover, consecutive addresses to each of these working zones frequently differ by a small amount. In such cases, an offset with respect to the previous address for that zone is sent, together with a zone identifier. The offset is encoded so as to reduce the activity of the address bus. This scheme is extended to the data bus [8] by noticing that the data for successive accesses to a working zone frequently differ also by a small amount, so that it is effective also to send the offset.

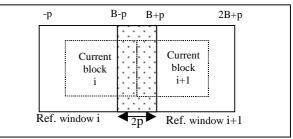

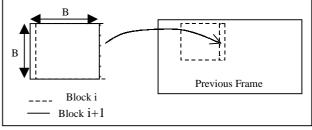

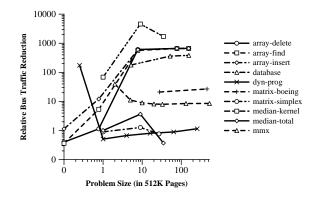

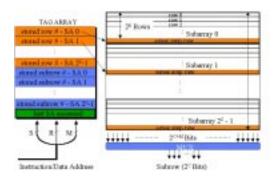

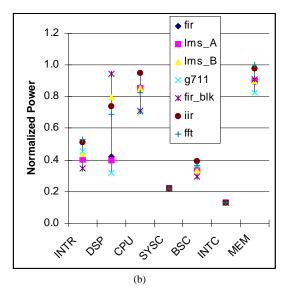

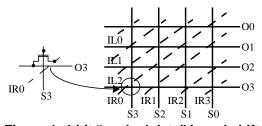

To evaluate the effectiveness of the technique in general applications, several SPEC95 streams of references to memory along with the corresponding data values were used. Among the possible bus organizations (see Figure 1), we have considered a multiplexed address bus (for instruction and data addresses) and a multiplexed instruction/data bus, with and without a unified 8K-byte direct-mapped cache. We also have compared with previously proposed encodings: Gray, bus-invert, T0, combined T0/bus-invert, inc-xor and dbm-vbm. Table 1 summarizes the results obtained. The table shows the energy reduction ratios of the WZE tech-

<sup>\*</sup>This work has been partially funded by CICYT TIC 95-0419.

|                          | Address Bus Ratio |             | Ins/Data Bus Ratio |                 | Both Buses Ratio |                 |

|--------------------------|-------------------|-------------|--------------------|-----------------|------------------|-----------------|

|                          | vs. non           | vs. best    | vs. non            | vs. best        | vs. non          | vs. best        |

|                          | encoded           | of rest     | encoded            | of rest         | encoded          | of rest         |

| Avg. (no cache)          | (0.39) $0.47$     | (0.54) 0.66 | (0.67) $0.73$      | $(0.77) \ 0.84$ | $(0.56) \ 0.63$  | $(0.69) \ 0.78$ |

| Avg. (with cache) $Avg.$ | (0.71) $0.87$     | (0.87) 1.06 | (0.53) $0.63$      | $(0.61) \ 0.72$ | $(0.60) \ 0.72$  | $(0.70) \ 0.85$ |

Table 1: Results summary for some SPEC95 streams. Ratios are calculated as *Energy WZE/Energy other*, being *other* the unencoded case and the best of the rest of the techniques evaluated. Energy overhead of the encoder/decoder logic is only included for the WZE technique. In parenthesis, without overhead.

nique with respect to the unencoded case and to the best of the rest of the techniques, for each of the buses and for both together. We conclude that the WZE encoding significantly reduces the activity in both buses. Moreover, for the case without cache, the technique presented here outperforms the other previous bus encoding proposals for low power. On the other hand, for the case with cache the best scheme for the address bus is either the WZE presented here or bus-invert with four groups, depending on the overhead of these two techniques. In any case, the WZE method outperforms the rest of the techniques when both buses are encoded, and requires fewer additional wires than the bus-invert with four groups.

In this paper we give an overview of the WZE technique and summarize previous work on the topic; this material is similar to that of [8] and should give the reader a reasonable understanding of the method. For more details consult [10, 11]. We then focus on preliminary work on the following two topics:

- Reduction of the effect of the WZE delay on the bus access time by overlapping this delay with the virtual to physical address translation.

- Use of the WZE technique in multimedia applications, which are characterized by having packed bytes in a word. Because of the particular features of these applications, we explore the possibility of special modifications to the encoding technique for the data bus.

#### 1.1 Previous work

Several encoding techniques for reduced bus activity have been reported, such as one-hot [6], Gray [7], bus-invert [13], T0 and combined bus-invert/T0 [5], and inc-xor and dbmvbm [12].

One-hot encoding results in a reduced activity because only two bits toggle when the value changes. However, it requires a number of wires equal to the number of values encoded, so that it is not practical for typical buses.

Gray and T0 encoding are targeted to situations in which consecutive accesses differ by one (or by a fixed stride). The Gray encoding is useful because the encoding of these values differs by one bit. In the T0 encoding an additional wire is used to indicate the consecutive access mode, and no activity is required in the bus.

The bus-invert method [13] consists on sending either the value itself or its bit-wise complement, depending on which would result in fewer transitions. An extra wire is used to carry this polarity information. For uniform and independent distributions, this encoding technique works better when the bit-width of the value to be sent is divided into smaller groups and each one encoded independently. The bus-invert technique has been combined with T0 in [5], thus obtaining more activity reduction than each of the techniques by itself.

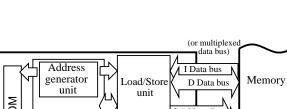

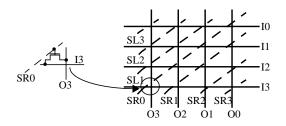

Figure 2: Address space with three vectors.

A source-coding framework is proposed in [12] as well as some specific codes. The scheme is based on obtaining a prediction function and a prediction error. This prediction error is XORed with the previous value sent to the bus so that the number of transitions is reduced in the likely case when the prediction error has a small number of ones. For addresses, the only new code proposed is the inc-xor code, in which the prediction is the previous address plus one (or any fixed stride) and the prediction error is obtained by the bitwise XOR operation. This code is most beneficial for instruction address buses, where sequential addressing is prevalent. Also presented are codes which relate to the 1-hot encoding used in this paper, such as the dbm-vbm, that are applied to the data bus. In the dbm-vbm technique, the prediction is the previous address and the prediction error is obtained by a function that increases as the absolute difference between the current input and the prediction increases. Afterwards, code-words with fewer 1's are assigned to smaller error values. Finally, the result is XORed with the previous value sent to the bus.

#### 2 Overview of the WZE technique

In this Section an overview of the WZE technique for the address bus is given along with the implementation decisions made and the rationale behind them. Afterwards, an extension of the WZE technique [8] is reviewed which allows the data bus to be encoded by reusing a large portion of the hardware already used to encode the address bus.

The basis of the WZE technique is as follows:

1. It takes into account the locality of the memory references: applications favor a few working zones of their address space at each instant. In such cases, a reference can be described by an identifier of the working zone and by an offset. This encoding is sent through the bus. 2. The offset can be specified with respect to the base address of the zone or to the previous reference to that zone. Since we want small offsets encoded in a one-hot code, the latter approach is the most convenient.

As a simple example consider an application that works with three vectors (A, B and C) as shown in Figure 2. Memory references are often interleaved among the three vectors and frequently close to the previous reference to the vector. Thus, if both the sender and the receiver had three registers (henceforth named Prefs) holding a pointer to each active working zone, the sender would only need to send:

- the offset of the current memory reference with respect to the Pref associated to the current working zone

- an identifier of the current Pref.

- 3. To reduce the number of transitions, the offset is encoded in a one-hot code. Since the one-hot code produces two transitions if the previous reference was also in the one-hot code and an average of n/2 transitions when the previous reference is arbitrary, the number of transitions is reduced by using a transition-signaling code [14]. In this case, before sending the reference through the bus an XOR operation is performed with the previous value sent, always resulting in one transition.

- 4. One value can be sent using a 0-hot code, which with transition signaling produces zero transitions. This code should be used for the most-frequent event, which we have determined to be a repetition of the same offset for the current working zone.

- 5. When there is a reference that does not correspond to a working zone pointed by any Pref, it is not possible to send an offset; in such a case, the entire current memory reference is sent over the bus. Moreover, it is necessary to signal this situation.

- 6. In general, the total number of working zones of a program can be larger than the number supported by the hardware. Consequently, these have to be replaced dynamically. The most direct possibility is to replace an active working zone as soon as there is a miss. However, in this case any arbitrary reference would disturb an active working zone. To reduce this effect, we incorporate additional registers (henceforth named *potential working zones*) that store the references that cause a miss. Various heuristics are possible to determine when a potential working zone becomes an active one.

#### 2.1 Implementation decisions

In the general scheme presented above, there are many aspects that have to be decided to obtain a suitable implementation. These decisions affect both the complexity of the implementation and the energy reduction achieved. Since there are many interdependent parameters, it is not practical to explore the whole space. Below we indicate the decisions made and the rationale for them.

• The number of active and potential working zones affects the number of registers and associated logic (and therefore the encoder/decoder energy consumption) and

the number of values of the identifier. In the evaluation of the scheme, we have explored a range of values and determined the one that produces the largest reduction. It was determined that a small number of working zones is sufficient.

- When there is a hit to a working zone, an offset and an identifier are sent. There are choices for the set of values of the offset and the code of the identifier. Since the offset is sent in a one-hot code (with transition signaling) the set of values is directly related to the number of bits required. We have decided to use all bits of the original bus to send the offset. Moreover, we have seen that the number of hits is maximized if positive and negative offsets are used. Since all bits of the original bus are used for the offset, it is necessary to have additional wires for the identifier and, to minimize these additional wires, we use a binary code. We have considered using bits of the original bus for the identifier (thus reducing the offset bits) and have observed a significant increase in I/O activity with respect to the use of separate bits.

- When there is a miss, this situation has to be signaled to the receiver. Since in that case, all bits of the original bus are used to send the address, this hit/miss condition has to use some additional wire. As we already have decided to use additional wires for the identifier, one value on these wires might be used to signal the miss. However, this would produce a few transitions when changing from a hit to a miss. To assure only one transition, we have assigned an additional bit to signal a miss.

- The search for a hit in a working zone requires subtracting the previous address with the current one and detecting whether the offset is in the acceptable range. For the selection of which zones to check it is possible to use any of the schemes used for caches. Because of the small number of working zones, we have chosen a fully-associative search.

- There are two replacement procedures required: for the active working zones and for the potential working zones. As indicated before, when there is a miss the address is placed in a potential working zone. Since there are few of these, we use the LRU algorithm for this placement. Moreover, it is necessary to determine when a new active working zone appears and, in this case, which active working zone to replace. Among the possible alternatives, we have chosen to initiate a new active working zone when there is a hit in a potential working zone. Again, here we use the LRU replacement algorithm.

#### 2.2 Extension to the data bus

The technique for the address bus can be extended to include also the data bus. This extension is based on the fact that in many instances the data values of consecutive accesses to a working zone differ by a small amount. If that is the case, the data can also be sent as an offset, coded in the one-hot encoding. In this case, the zero-hot encoding is used when the offset is zero.

To implement this extension, as illustrated in Figure 2, we include an additional register, called Pdat, per working zone. On the other hand, if the access is not to an active working zone or if the offset is larger than possible for the

| ſ | Value sent<br>over the bus<br>(either address | Transition signaling<br>and one-hot retrieval<br>1. XORing 2. One-hot |           | Receiver<br>action<br>(address bus) | Receiver<br>action<br>(data bus) |

|---|-----------------------------------------------|-----------------------------------------------------------------------|-----------|-------------------------------------|----------------------------------|

|   | or data)                                      | 11 11 0 1000g                                                         | retrieval | (uuu 000 000)                       | (1111 212)                       |

|   | (-) 010011                                    | -                                                                     | -         | -                                   | -                                |

|   | (2) 011011                                    | 001000                                                                | 3         | offset 3 (Pref $\#2$ )              | offset 3 (Pdat $\#2$ )           |

|   | (1) 011011                                    | 000000                                                                | †         | same offset (Pref #1)               | same data value (Pdat $\#1$ )    |

|   | (1) 011001                                    | 000010                                                                | 1         | offset 1 (Pref $\#1$ )              | offset 1 (Pdat $\#1$ )           |

Table 2: Example of the decoding process. Assuming always hit; () in the first column indicates working zone number.

one-hot encoding, the whole value is sent through the bus. An additional wire is required to distinguish these cases.

In addition, to further reduce the bus transitions, when the value in the data bus is not encoded by the WZE method, we use the bus-invert technique; for the address bus we saw that the benefits of using the bus-invert in this case were very small.

In summary, for the address bus, to send the offset it is necessary to compare it with the previous offset to the same working zone. The following two situations occur:

- the offsets are the same: send again the previous value sent over the bus (zero transitions)

- they are different: send the one-hot encoded value of the offset using transition signaling (one transition).

For the data bus, to send the offset it is necessary to compare the current data value with the Pdat associated to the current working zone, and the following situations occur:

- the values are the same: send again the previous value sent over the bus (zero transitions)

- they are different: send the one-hot encoded value of the offset (one transition).

The decoding of an offset in the receiver is done also in two steps: XORing the value that it receives with the previous one, and retrieving the one-hot of the result. When the XORing produces a 0 vector, the two values were the same and this is interpreted (see Table 2):

- for the address bus, as a repetition of the previous offset to that same working zone,

- for the data bus, as a repetition of the previous data value when that same working zone was last accessed

#### 2.3 Address and data bus fields

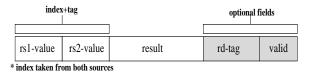

As shown in Table 3 (next page) the encoded address and data bus consists of five fields:

- the  $n_a$  wires of the original address bus (word\_address)

- the n<sub>d</sub> wires of the original data bus (word\_data)

- $\lceil \log_2(H+M) \rceil$  wires to specify one of H working zones or M potential zones (ident)

- one wire to indicate whether there has been a hit or a miss in any of the zones (WZ\_miss)

- one wire to indicate if the data bus has been able to be encoded using the offset (dbus\_WZ\_encoded)

- one wire to indicate, in the case of a miss in the working zones, whether the data bus is coded with the businvert technique (dbus\_BI\_encoded).

Therefore,  $m = n_a + n_d + \lceil \log_2(H + M) \rceil + 3$  wires are required.

#### 3 Reducing the delay

The decoder introduces some delay in the bus access. Since this might be unacceptable, we now describe a method to overlap this delay with the virtual to physical address translation.

When an address translation is required, the most direct approach would be to perform the translation and then apply the encoding to the resulting physical address. However, this would produce an increased delay for the bus access. To reduce this delay we propose the following modification of the WZE technique:

• Use the virtual address to determine whether there is a hit in a working zone. To do this, each Pref contains the virtual address of the previous access to the corresponding zone.

Since, as it is well known, the translation modifies only the most-significant bits of the address (the page number) but keeps unaltered the least-significant bits (the page offset), this procedure is correct as long as the offset does not cross page boundaries. Consequently, it is necessary to detect when a change of page occurs and, in that case, the access is not treated as an offset.

Since the data value is not translated, this is encoded as in the original method.

Because of this modification in the WZE technique, the reduction in energy might be affected. This is because now we do not use offsets which cross a page boundary. On the other hand, the internal energy overhead might be reduced because now the detection of offset uses only the page-offset bits. The simulation of the SPEC benchmarks indicate that for a page size of 1 KB or larger the effect is negligible. We observe this in Table 4, where the I/O transitions per reference on the multiplexed address bus for the gcc benchmark (with unified cache) and for different page sizes is shown.

|              | I/O transitions/reference |

|--------------|---------------------------|

| Page size    | (address bus)             |

| (no pages)   | 3.26                      |

| $4K \ bytes$ | 3.26                      |

| 1K bytes     | 3.29                      |

| 256 bytes    | 3.36                      |

| 64 bytes     | 3.72                      |

| 1 byte       | 5.32                      |

Table 4: Effect of the pages on the activity reduction if the WZE delay is overlapped with the virtual to physical address translation. For pages larger than 1K bytes the effect is negligible. Some unrealistic page sizes are also shown for comparison purposes. The data is for the gcc benchmark with unified cache.

|        |           | m-wire encoded address and data bus        |                          |                 |                 |                                |  |  |  |

|--------|-----------|--------------------------------------------|--------------------------|-----------------|-----------------|--------------------------------|--|--|--|

|        | WZ_miss   | ident                                      | word_address             | dbus_WZ_encoded | dbus_BI_encoded | word_data                      |  |  |  |

|        | (1  wire) | $(\lceil log_2(H+M) \rceil \text{ wires})$ | $(n_a \text{ wires})$    | (1  wire)       | (1  wire)       | $(n_d \text{ wires})$          |  |  |  |

| WZ     | 0         | WZ index                                   | offset or                | 1               | don't care      | offset or                      |  |  |  |

| format |           |                                            | last address value       |                 |                 | last data value                |  |  |  |

|        |           |                                            |                          | 0               | 1               | BI <sub>G=1</sub> (data value) |  |  |  |

|        |           |                                            |                          |                 | 0               | complete data                  |  |  |  |

| Non WZ | 1         | don't care                                 | complete                 | don't care      | 1               | $BI_{G=1}(data value)$         |  |  |  |

| format |           |                                            | $\operatorname{address}$ |                 | 0               | complete data                  |  |  |  |

Table 3: Information assigned to each of the several fields of the encoded address and data bus when there is a hit (WZ format) and a miss (Non WZ format) in the H working zones and in the M potential working zones. The number of wires for each field is also shown.

#### 4 Use in Multimedia Applications

In this Section we modify the WZE technique for the data bus for those multimedia applications that use data workloads composed of packets of data that may be brought from memory several in the same word. Examples of these are the image processing applications and we will evaluate the WZE technique for two particular examples. We show the results for the data-only data bus and the data-only address bus (see Figure 1). The code of the applications is assumed to be stored in an internal ROM (therefore no references to instructions are sent through the address bus and no instructions are fetched through the data bus).

In multimedia applications images are composed of pixels. These pixels consist of one or a few components, each with a relatively small number of values (for instance, in the examples we illustrate each pixel consists of three colors and each color can have 256 values). In such case, these pixels can be stored in one word which is subdivided into subwords for each component. In many applications, these components are accessed and processed simultaneously. We now describe how we modify the WZE technique for this situation.

The address bus encoding part of the technique is not modified, since the locality of reference is even more apparent in these applications with images. For the data part we do the following:

- Instead of using an offset for the whole word, we encode each of the bytes using the byte offset. In this way, the one-hot encoding allows eight possible offsets. We have determined that this number of offsets (which would correspond to offsets from -4 to +4) is insufficient to capture a significant portion of the data. Consequently, it is convenient to extend the encoding to include also k-hot encodings for k > 1.

- Moreover, if we allow two possibilities for each byte, namely that the data satisfies the offset range (a hit) or not (a miss), we would need individual wires per byte to indicate this hit/miss. Since this would be a significant wire overhead, we decided to code every data byte as an offset, no matter how large this offset is. Moreover, since a k-hot encoding with transition signaling generates k transitions in the bus, to reduce the average number of transitions we encode the offsets into a k-hot code, with smaller value of k for the more frequent offsets (that is, the value of k increases as the absolute value of the offset increases).

- When there is an address miss (that is, the address does not correspond to an active WZ), the most direct solution is to send the unencoded data value. However, we have found that the variation in the values of

images is small enough so that it is better to send the offsets with respect to the last data value.

Note that in this modification of the WZE technique, the two extra wires (dbus\_WZ\_encoded and dbus\_BI\_encoded in Table 3) are not needed, since the data bus is always encoded and no bus-invert is done.

We have done some preliminary evaluations for two applications: *image alpha blending* and *motion estimation*. Both use color images where a pixel is composed of three bytes that specify the three main colors; a pixel is read or written per memory reference.

#### 4.1 Image Alpha Blending

Alpha Blending [1] is used for imaging effects to merge two images together, weighting one image more than the other. Thus, alpha blending may be used for fading from one image to another and this is the case shown here: given two images of two different human faces, six images are generated so that the first image is transformed into the second one. This is done for three different sets of human faces [2].

The results are reported in Table 5, where the WZE technique is compared to the unencoded case and to the best of the rest of the techniques (bus-invert with three groups, one per byte). The WZE technique uses four active and two potential working zones.

#### 4.2 Motion Estimation

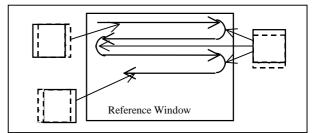

The Motion-estimation algorithm [9] is used in video transmission to lower the bandwidth of the network where the video is being transmitted. The frame to be transmitted is divided into blocks which are compared to several blocks in the previous frame and the best match is selected.

The basic motion-estimation algorithm is applied to two different sets of images in motion [3, 2] (weather satellite, human face and football images). Results are shown in Table 6; the best of the rest of the techniques is the dbm-vbm with three groups. The WZE technique uses three active working zones and no potential working zones.

|                                     | Data-only Data Bus |      |                     |  |  |

|-------------------------------------|--------------------|------|---------------------|--|--|

| Images                              | non                |      |                     |  |  |

|                                     | encoded            | WZE  | $\mathbf{BI}_{G=3}$ |  |  |

| t claire 	o missa                   | 10.07              | 3.00 | 8.68                |  |  |

| t claire 	o susie                   | 10.68              | 3.23 | 8.58                |  |  |

| $\texttt{missa} \to \texttt{susie}$ | 10.43              | 3.83 | 8.97                |  |  |

Table 5: Data-only data bus I/O transitions per reference for the alpha-blending application. The best of the rest of the techniques is the bus-invert with three groups.

|                   | Data-only Data Bus Ratio |          | Data-only | Address Bus Ratio           | Both Buses Ratio |          |

|-------------------|--------------------------|----------|-----------|-----------------------------|------------------|----------|

|                   | vs. non                  | vs. best | vs. non   | vs. best                    | vs. non          | vs. best |

| Application       | encoded                  | of rest  | encoded   | $\mathbf{of} \mathbf{rest}$ | encoded          | of rest  |

| Image Blending    | 0.32                     | 0.38     | 0.17      | 0.23                        | 0.26             | 0.32     |

| Motion Estimation | 0.58                     | 0.81     | 0.36      | 0.41                        | 0.49             | 0.67     |

Table 8: Results summary for the two multimedia applications. Smaller ratio means fewer I/O transitions.

|                   | Data-only Data Bus |      |                                          |  |

|-------------------|--------------------|------|------------------------------------------|--|

| Image Sequences   | non                |      |                                          |  |

|                   | encoded            | WZE  | $\mathbf{dbm}\text{-}\mathbf{vbm}_{G=3}$ |  |

| weather satellite | 10.05              | 5.93 | 7.58                                     |  |

| human face        | 9.13               | 5.14 | 5.89                                     |  |

| football          | 10.79              | 6.22 | 7.79                                     |  |

Table 6: Data-only data bus I/O transitions per reference for the motion-estimation application. The best of the rest of the techniques is the dbm-vbm with three groups.

|                   | Data-only Address Bus |      |                 |  |  |

|-------------------|-----------------------|------|-----------------|--|--|

| Application       | non                   |      | best of         |  |  |

|                   | encoded               | WZE  | $\mathbf{rest}$ |  |  |

| Image Blending    | 7.78                  | 1.33 | 5.78            |  |  |

| Motion Estimation | 6.71                  | 2.40 | 7.21            |  |  |

Table 7: Data-only address bus I/O transitions per reference for the two example multimedia applications.

Table 7 shows the data-only address bus results for both applications. For the image blending the best of the rest of the techniques is the dbm-vbm whereas for the motion estimation is the bus-invert. In any case, the WZE technique clearly outperforms any previously proposed technique.

The averaged results for both applications are shown in Table 8. We show the ratio of the I/O transitions with respect the unencoded case and to the best of the rest of the techniques for the data-only data bus, data-only address bus and both buses. The I/O activity when coding both buses is reduced by 74% and 51% with respect the unencoded case, and by 68% and 33% with respect the best of the rest of the encoding techniques.

#### 5 Conclusions

This paper gives an overview the Working Zone Encoding (WZE) method for encoding an external address and data bus, based on the conjecture that programs favor a few working zones of their address space at each instant.

For the general-purpose microprocessor multiplexed address bus and multiplexed instruction/data bus (with unified cache), the WZE significantly reduces the I/O activity, around 30% with respect to the unencoded case and 15% with respect the best of the rest of the encoding techniques. When no caches are present, the reductions are even larger.

For two multimedia applications using images as the workload, the activity in the data-only data bus and the dataonly address bus is reduced by 74% and 51% with respect the unencoded case, and by 68% and 33% with respect the best of the rest of the encoding techniques. These results are promising and make it worthwhile to pursue the development of this approach.

#### References

- [1] http://developer.intel.com/drg/mmx/appnotes/ ap554.htm.

- [2] http://ipl.rpi.edu/sequences/sequences.html.

- [3] http://meteosat.e-technik.uni-ulm.de/meteosat.

- [4] H. Bakoglu. Circuits, Interconnections and Packaging for VLSI. Menlo Park, CA, 1990.

- [5] L. Benini, G. De Micheli, E. Macii, D. Sciuto, and C. Silvano. Address bus encoding techniques for system-level power optimization. In *Design*, *Automation and Test in Europe*, pages 861–866, February 1998.

- [6] A.P. Chandrakasan and R.W. Brodersen. Low Power Digital CMOS Design. Kluwer Academic Publishers, 1995.

- [7] R.M. Owens H. Mehta and M.J. Irwin. Some issues in gray code addressing. In *Great Lakes Symposium on* VLSI, pages 178–180, March 1996.

- [8] T. Lang, J. Cortadella, and E. Musoll. Extension of the Working-Zone Encoding method to reduce the energy on the microprocessor data bus. Technical Report http://www.eng.uci.edu/numlab/archive/pub/nl98b/ 02.ps.Z, University of California, Irvine, May 1998. To be published in the next Int. Conference on Computer Design (ICCD'98).

- [9] C. Lin and S. Kwatra. An adaptive algorithm for motion compensated colour image coding. *IEEE Globe*com, 1984.

- [10] E. Musoll, T. Lang, and J. Cortadella. Exploiting the locality of memory references to reduce the address bus energy. In Int. Symp. on Low Power Design and Electronics, pages 202-207, August 1997.

- [11] E. Musoll, T. Lang, and J. Cortadella. Working-Zone Encoding for reducing the energy in microprocessor address buses. Technical Report http://www.eng.uci.edu/numlab/archive/pub/nl98b/ 01.ps.Z, University of California, Irvine, March 1998. To be published in the next special issue of Transactions on VLSI on low-power electronics and design.

- [12] S. Ramprasad, N.R. Shanbhag, and I.N. Hajj. Coding for low-power address and data busses: a source-coding framework and applications. In Proc. of the Int. Conf. on VLSI Design, pages 18-23, January 1998.

- [13] M.R. Stan and W.P. Burleson. Bus-invert coding for low power I/O. *IEEE Trans. on VLSI Syst.*, pages 49– 58, 1995.

- [14] M.R. Stan and W.P. Burleson. Low-power encodings for global communications in CMOS VLSI. *IEEE Trans.* on VLSI Syst., pages 444-455, 1997.

# **Reduced Address Bus Switching with Gray PC**

Forrest Jensen Akhilesh Tyagi\*

Iowa State University Ames, IA 50011

#### Abstract

Reduced switching on the address bus saves on the energy incurred in PC increment, the propagation of PC value across the pipeline, instruction cache access, and memory access. We estimate the savings in bit switchings in PC by adopting the Gray sequence for program sequencing. There is a 40% reduction in address bit switchings with a Gray PC over the traditional lexicographic PC over a collection of SPEC '95 integer and FP benchmarks. We also assess the adverse impact of Gray PC on the other processor units, particularly I-cache locality. The cache miss rates are indistinguishable between the Gray and lexicographic sequencing. These experiments were conducted with the SimpleScalar tool set. We also propose a design for a Gray counter for the PC. We have developed optimization algorithms for the loader so that the expected address bus switching is minimized.

#### 1 Introduction

The need for reduced energy in processors has been emphasized elsewhere [Sin94]. Portable computing platforms (general purpose computing engines such as laptops or special purpose embedded processors) strive to reduce the energy of computation in order to prolong the battery life. The packaging and heat dissipation limitations are another driving force behind the low energy processor architecture and implementation trend.

In this paper, we assess the effectiveness of nonlexicographic instruction ordering, in particular Gray ordering, in reducing address bus switching and system energy. There are several architecture level side-effects of Gray address ordering that need to be evaluated. Specifically, an adverse impact on cache locality can negate any energy gains derived from the lower address bus switching.

This change in the implementation is transparent to the software. The only system component that needs to be modified is the loader. A simplistic loader can load an instruction originally at address A at the address gray(A). However, this poses a new optimization problem for the loader, to minimize the expected switching over the program graph. We provide some algorithms for this optimization problem as well, which have not been implemented yet (Section 4).

Note that we will use terms *energy* and *power* interchangeably since for a processor power is just the en-

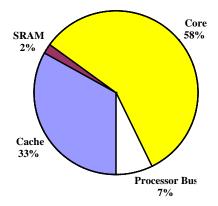

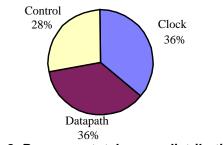

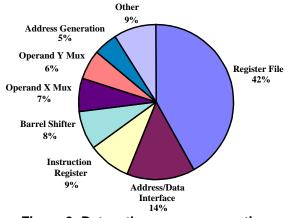

ergy per cycle times the clock frequency. Hence any technique not explicitly changing clock frequency affects both energy and power identically. What fraction of processor and system energy is affected by reduced address bus switching? Burd and Peters [BP94] and Gonzalez and Horowitz [GH96] have profiled the energy distribution of MIPS R3000 processor. Both the studies are based on simulations of a VLSI design for the MIPS R3000 architecture. Burd and Peters [BP94] compute the switched capacitance per cycle as an estimate of energy. The switching frequency of capacitances depends on the control signal, instruction and data correlations. They simulate the MIPS R3000 architecture with several real benchmark programs (from SPECint '92 benchmark suite) to derive a probability for switching for all the internal capacitive nodes. The total expected switched capacitance per clock cycle is 317 pF. The breakdown is as follows: instruction cache (I-Cache) memory: 30%; I-Cache control: 15%; Datapath: 28% with register file accounting for 10%; and ALU & shifter for another 12%; Global buses: 3-4%; Controller: 10%; DCache: 8-9%. The program counter logic (next-PC) takes up another  $\approx 4\%$  energy. Note that the proposed Gray PC (program counter counting in Gray sequence) reduces energy for ICache address decoder and PC logic (and some for global buses) which accounts for  $\approx 21\%$  processor energy.

These numbers did not include the switched capacitance for off-chip memory (address bus on the backplane). Assuming reasonable cache *hit rates*, and given a 25pF external load, the external switched capacitance per cycle is 272 pF! This is almost as high as the processor average switched capacitance of 317 pF. Hence, the proposed Gray PC can potentially have a bigger impact on the input/output energy than on the intra-processor energy. We discuss in Section 5 potential impact of Gray PC on the L1 instruction cache and L2 cache interface.

The literature on logic design for a Gray counter and/or adder is sparse. We propose a design for a Gray counter in Section 3. This design is being implemented so that the counting energy of a Gray PC and a lexicographic PC can be compared. Doran [Dor93] is the most comprehensive reference on Gray adder design. Altera corporation [Cor94] has an application brief dealing with a Gray counter design. Note that in the rest of the paper, we refer to binary reflected Gray code sequence by the term Gray sequence. We also discuss a design for instruction cache decoder in order to better exploit the low Hamming distances of Gray sequences in Section 5. Section 2 describes the experimental setup

<sup>\*</sup>This work was supported in part by NSF grant #MIP9703702.

and results.

Su *et al.* [STD94] also use a Gray PC. They report on the average address bus switching on an internal set of programs, but do not consider other aspects of Gray PC.

#### 2 Experiments and Results

Burd & Peters [BP94] note that the average switching per program counter (PC) bit is a little over 7% over a variety of SPECint '92 benchmarks. Hence, the expected number of bit switchings over a 32 bit address are 2.5. This is consistent with the observation that an average basic block's size is 4-5 instructions, which accounts for about 2.3 least-significant bit switchings. The remaining switching comes with 20-25% frequency when a non-sequential instruction such as a branch or procedure call is encountered. Gray PC ensures that within a basic block (and between basic blocks as well, as often as possible), exactly one address bit switches through the use of Gray sequencing in the PC. Assuming, we can ensure Gray sequencing within all basic blocks, the expected address bus switching based on back-of-theenvelope calculations would be approximately 1.2 (.2 accounts for switching due to non-sequential instructions).

The cache placement of instructions is based on the lexicographic addresses. The locality of program execution is exploited to achieve high hit rates. The cache blocks and sets are organized on the basis of contiguous bits. For instance, the least significant  $k_0$  bits give block-offset, the next  $k_1$  bits give the set address and the remaining bits give the tag. This type of mapping reflects locality based on lexicographic ordering. It is possible that two instructions residing in conflicting blocks in lexicographic ordering may not conflict in Gray ordering or vice versa. Hence we need to calibrate the hit rates of the instruction cache under lexicographic and Gray PCs. If the hit rate goes down significantly with a Gray PC, the increased energy cost of memory accesses might offset any gains derived from reduced address bus switching.

To determine the number of PC bits that switch in a Gray code PC versus a lexicographic PC and to determine any difference in cache performance between the two encoding methods, we conducted our experimental work with a modified version of *sim-cache*, one of the simulation tools available in the SimpleScalar suite of simulators [BAB96]. In addition to determining the total number of switched bits with each encoding method, we also determined the number of times each of the eleven least significant bits of the PC switch. Sim-cache uses a 32 bit address to access 8 byte instructions. As a result, the three least significant bits are always zero. For the remainder of this discussion we ignore bits 0-2 and think of bits 3-10 as the eight least significant bits. To measure differences in the cache performance, we calculated miss rate for the level 1 instruction cache. For purposes of simulation, we maintained the PC as a lexicographic binary number. We incremented the counter and added offsets for jumps and branches in the usual fashion. Before each instruction memory access, including program load and instruction fetch, we converted the PC value to Gray. With SPEC95 integer and FP benchmarks, a Gray code PC produced approximately 40% fewer instruction address bit transitions. Note that the address bus transition frequency is similar over both the integer and FP benchmarks. In Table 1 we present the address bit switching results. For both lexicographic and Gray encoding we show the average number of switched bits per instruction for the entire address and also for the eight least significant bits. The final column shows the percentage change in the total number of switched bits when going from lexicographic encoding to Gray encoding.

The reduction in instruction address bit switches confirms the observations made by Su *et. al.* In addition, we observe that the eight least significant bits account for 90-93% of all switched bits. This suggests the possibility of implementing a PC that is partially lexicographic and partially Gray. The level 1 instruction cache miss rates produced by the two encoding methods were identical. We present these values in Table 2. We used separate level 1 instruction and data caches. Both were 8 KB with 256, 32-byte direct mapped blocks. The 1 MB unified level 2 instruction and data cache had 4096, 4-way associative sets. We used 64 KB blocks and the LRU replacement scheme.

#### 3 Gray Counter Design

There are two general operations performed on the contents of the PC, increment and addition of an offset for jump or branch instruction. We begin by presenting a Gray adder and follow with a Gray counter, which is a specialized adder. Conceptually, addition of Gray numbers is performed by first converting from Gray to lexicographic, adding the numbers, and then converting back to Gray. The disadvantage of this approach is that the Gray to lexicographic conversion is performed beginning with the MSB and working towards the LSB, while addition is performed in the opposite direction. The result is that two passes must be made through the bits instead of the usual single pass. To reduce the time necessary for the Gray to lexicographic conversion, we limit the Gray implementation to the eight least significant bits of the PC and use lexicographic for the remaining high order bits. The interface between the Gray and lexicographic sections is trivial. In addition, we include a parity bit that indicates the parity of the Gray portion of the PC and allows us to convert from Gray to lexicographic beginning with the LSB. The Gray to lexicographic conversion, rather than the addition and conversion back to Gray, is still the limiting factor of this design. We have therefore divided the Gray portion into two nibbles. We convert the high order nibble to lexicographic beginning with its MSB, progressing towards the LSB. For the low order nibble, we work in the opposite direction beginning with its LSB. The conversion to lexicographic of the two nibbles is therefore performed in parallel. Unlike Su et. al., we do not modify the offsets before loading the program into memory. As a result, we need to convert only the PC to lexicographic before adding. Although this does not affect the speed of the conversion, it does reduce the complexity of the adder. For lexicographic addition, a full adder generates sum and carry bits. These are calculated with the following equations:

$s_i = a_i \oplus b_i \oplus c_i$

$c_{i+1} = a_i b_i + c_i (a_i + b_i)$

The symbols are understood as follows:

$a_i$  and  $b_i$  are the two bits being added.  $s_i$  is the sum

|            |               | Lexico   | Lexicographic |          | ray       |          |

|------------|---------------|----------|---------------|----------|-----------|----------|

| Benchmark  | Instr. count  | Switches | Bits 3-10     | Switches | Bits 3-10 | % change |

|            |               | per inst |               | per inst |           |          |

| int:       |               |          |               |          |           |          |

| cc1        | 264,897,677   | 2.3034   | 2.1832        | 1.4222   | 1.3126    | -38.25   |

| li         | 173,965,506   | 2.3358   | 2.1718        | 1.4246   | 1.3217    | -39.01   |

| go         | 132,917,038   | 2.2685   | 2.1504        | 1.3195   | 1.2338    | -41.83   |

| compress95 | 35,684,602    | 2.2812   | 2.1939        | 1.3860   | 1.3044    | -39.24   |

| m88ksim    | 494,917,870   | 2.3333   | 2.2338        | 1.3347   | 1.2681    | -42.80   |

| vortex     | 404,996       | 2.2661   | 2.1858        | 1.3242   | 1.2519    | -41.56   |

| FP:        |               |          |               |          |           |          |

| swim       | 796,527,564   | 2.2343   | 2.1244        | 1.2327   | 1.1241    | -44.83   |

| wave5      | 4,515,144,715 | 2.1081   | 2.0595        | 1.1763   | 1.1538    | -44.20   |

Table 1: Average number of switched bits per instruction for lexicographic and Gray program counters

| Benchmark  | Lexicographic | Gray   |

|------------|---------------|--------|

| int:       |               |        |

| cc1        | 0.0986        | 0.0986 |

| li         | 0.0260        | 0.0260 |

| go         | 0.0854        | 0.0854 |

| compress95 | 0.0005        | 0.0005 |

| m88ksim    | 0.0867        | 0.0867 |

| vortex     | 0.0715        | 0.0715 |

| FP:        |               |        |

| swim       | 0.0132        | 0.0132 |

| wave5      | 0.0179        | 0.0179 |

Table 2: Level 1 Instruction Cache Miss Rates

produced at position *i*.  $c_i$  and  $c_{i+1}$  are the carry in and carry out of position *i*.

$c_0 = 0$  for addition and  $c_0 = 1$  for subtraction.

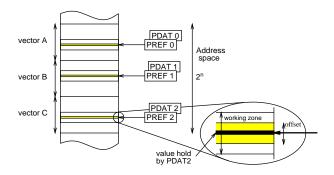

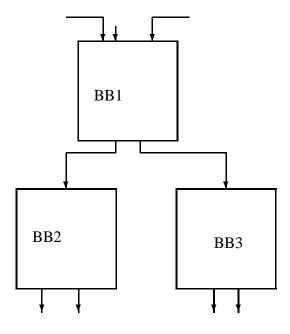

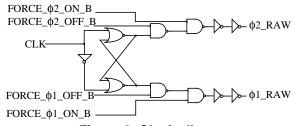

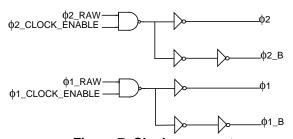

Figure 1 illustrates the dataflow within a Gray adder. In the top sequence (Figure 1 (a)) the conversion to lexicographic is completed before the addition can begin. In the middle sequence (Figure 1 (b)), the conversion to lexicographic is right to left, the addition runs in parallel but slightly behind. In the bottom sequence (Figure 1 (c)), the conversion to lexicographic of the two nibbles is performed in parallel. The addition follows behind the low order nibble conversion but still finishes ahead because it is not delayed by the conversion of the high order nibble.

The equations for a Gray adder are more complicated. This reflects the need for code conversions before and after the addition. For the Gray adder, we are adding a lexicographic number to a Gray number. In the following equations we represent the bits of the lexicographic value with a, the Gray value with g, and the lexicographic equivalent of the Gray value with b. We use p to represent the parity bit. In addition to sum and carry bits for each position, we must also determine the new value of p. These are calculated with the following equations:

$egin{aligned} s_i &= a_i \oplus a_{i+1} \oplus c_i \oplus c_{i+1} \oplus g_i \ s_7 &= a_7 \oplus a_8 \oplus c_7 \oplus c_8 \oplus b_7 \oplus b_8 \ c_{i+1} &= a_i b_i + c_i (a_i + b_i) \ p_{new} &= a_0 \oplus c_0 \oplus p_{old} \end{aligned}$

$c_0 = 0$  for addition and  $c_0 = 1$  for subtraction. We use a different equation for  $s_7$  because  $b_7$  is not derived from  $b_8$ .

For the low order nibble

$$b_i = b_{i-1} \oplus g_{i-1}$$

$$b_0 = p$$

For the high order nibble

$$b_i = b_{i+1} \oplus g_i$$

$$b_7 = q_7$$

Note that we have assumed the bits are labelled 0-7 with 0 being the LSB, so  $g_7$  is the MSB of the Gray number and  $c_8$  is the carry out of the most significant position.  $c_8$  serves as the carry in for the lexicographic adder used to sum the higher order bits. It is possible with a Gray adder, as with a lexicographic adder, to implement carry lookahead across a nibble. The only difference is that we must convert to lexicographic before computing the carry generate and carry propagate signals.

With a lexicographic counter, increment is generally performed by a half-adder. This is possible because, for increment, the number being added to the PC consists of a 1 for the LSB and 0's for all higher bits. Because of this, the equations for both lexicographic and Gray adders are a simplification of those given above. For a lexicographic counter, the equations are as follows:

$$s_{i} = b_{i} \oplus c_{i}$$

$$c_{i+1} = c_{i}b_{i}$$

$$c_{0} = 1$$

For the Gray counter, they are as follows:

$$s_{i} = (c_{i}\overline{b_{i}}) \oplus g_{i}$$

$$c_{i+1} = c_{i}b_{i}$$

$$c_{0} = 1$$

$$p_{new} = \overline{p_{old}}$$

For the low order nibble

$$b_{i} = b_{i-1} \oplus g_{i-1}$$

$$b_{0} = p$$

For the high order nibble

$$b_{i} = b_{i+1} \oplus g_{i}$$

$$b_{0} = g_{7}$$

#### 4 Loader

Loader's task is to assign instructions from the binary executable to the memory address space. Traditionally, it is a straightforward task since the mapping from the original program sequence to the address sequence is an identity (with a linear shift). However, with Gray sequencing, the loader must perform extra work.

A simple loader can take an instruction from address i in the program (*i*th instruction in the static program order) and load it at address base + gray(i) where base is the base address of the text segment, and gray(i) is

Figure 1: Illustration of Dataflow in Gray Counter

Figure 2: Program Flow Graph with Basic Block Nodes

the binary string in the *i*th position in a Gray sequence. This is what we have currently implemented.

However, there is a bigger opportunity for address bit switching reduction at the loader stage. The simplistic approach outlined above results in a single bit switch for the program flow within a basic block. The number of switched bits is not controlled (is comparable to the lexicographic PC scheme) for control flow out of basic blocks (inter basic block transitions). An example of a program flow graph is shown in Figure 2 where nodes represent basic blocks. Each of the edges can be assigned a probability based on static program profiling. Let  $p(BB_i, BB_j)$  be the probability of the transition from the basic block  $BB_i$  to the basic block  $BB_j$ . Let the address assigned to a basic block BB be denoted by A(BB). Let h(xy) be the Hamming distance of two binary strings x and y. Then the following optimization problem models the loader's task.

Input: A directed graph.

**Objective:** Find a memory address (for relocatability, a relative address) A(BB) for each Basic block BB such that

$$\sum_{\text{$\sigma$ enlBB}$} h(A(BB_i), A(BB_j)) * p(BB_i, B B_j)$$

is minimized.

If profiling is not feasible, we can minimize  $\sum_{\sigma \text{ enlBB}} {}_{i,\text{BB}_{j}} h(A(BB_{i}), A(BB_{j})).$

We have represented the Gray chain of addresses assigned to the instruction in a basic block BB by a single address A(BB) in order to bring out the similarities in this optimization problem and the low energy/power state machine synthesis. A common formulation of state assignment problem for low energy is to minimize  $\sum_{s_i,s_j \in S} h(s_i,s_j) * p(s_i,s_j)$ , where  $p(s_i, s_j)$  is the steady state probability of the transition between states  $s_i$  and  $s_j$ ,  $h(s_i, s_j)$  is the Hamming distance between the codes for the two states. We have developed several algorithms [Tya96], [SCT97] for low power state assignment. Our intent is to modify one of them [Tya96] to handle the address assignment problem for the loader. The main problem with this approach is the size of the input problem. The state assignment methods take time typically close to quadratic (or close to  $N^2 \log N$  in number of states N. A typical state machine has about 50-100 states. These approaches can turn out to be impractically expensive for large programs with hundreds of thousands of basic blocks. Hence, we are also looking into heuristics linear in the number of basic blocks. Dichotomy based state assignment methods such as [TPCD94] may be adaptable for an efficient loader algorithm.

#### 5 Future Work and Conclusions

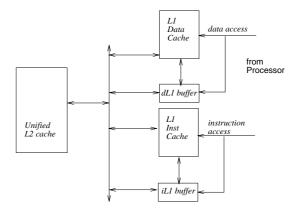

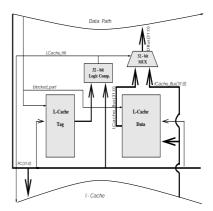

The work reported is still preliminary. There are several interesting threads that we plan to pursue in the future. The reduced address bus switching derived from Gray sequencing is directly visible at the I-cache. However, it is the L1 and L2 cache/memory interface that provides high capacitances for the address bus. But the addresses that appear at the L1/L2 interface are already filtered based on the cache locality characteristics. Are the Gray address sequences any better than the lexicographic address sequences at the L1/L2 interface? Are there any additional constraints on the loader optimization that can reduce the Hamming distance of upper address bits for the sets of addresses likely to collide in the cache? An additional complexity is that at the L1/L2 interface the instruction and data addresses are unified. This effect will further increase the average Hamming distance. Is Harvard architecture a better choice in order to separate the instruction and data data address sequences and retain their low hamming distances?

The decoder in the instruction cache accounts for a significant fraction of energy consumed in the instruction cache [BP94]. However, a typical decoder design is precharged. We plan to experiment with a hybrid static and dynamic decoder design that leverages the low hamming distance in the addresses to reduce energy.

#### References

- [BAB96] D. Burger, T. M. Austin, and S. Bennett. Evaluating Future Microprocessors: The SimpleScalar Tool Set. Technical Report CS-TR-96-1308, University of Wisconsin, Madison, 1996.

- [BP94] T. D. Burd and B. Peters. A Power Analysis of a Microprocessor: A Study of an Implementation of the MIPS R3000 Architecture. Technical report, ERL, University of California, Berkeley, 1994. URL: http://infopad.EECS.Berkeley.edu/~burd/gpp/ gpp.html#published\_papers.

- [Cor94] Altera Corporation. Ripple-Carry Gray Code Counters in FLEX 8000 Devices. Technical Report Application Brief 135, Altera Corporation, May 1994.

- [Dor93] R. W. Doran. The Gray Code. Technical report, Dept. of Computer Science, University of Auckland, 1993. URL: http://www.cs.aucland.ac.nz/~techrep/TR131.

- [GH96] R. Gonzalez and M. Horowitz. Energy Dissipation in General Purpose Microprocessors. *IEEE Journal of Solid State Circuits*, 31:1277–1284, 1996.

- [SCT97] P. Surthi, L. Chao, and A. Tyagi. Low-Power FSM Design using Huffman-Style Encoding. In Proc. of European Design and Test

Conference, IEEE Computer Society Press, pages 521–525, 1997.

- [Sin94] D. Singh. Prospects for Low-Power Microprocessor Design. talk delivered at ACM/IEEE International Workshop on Low Power Design, Napa Valley, CA, 1994.

- [STD94] Ching-Long Su, Chi-Ying Tsui, and Alvin Despain. Low power architectural design and compilation techniques for highperformance processor. In 'Proceedings of COMPCON 94, pages 489–498, February 1994.

- [TPCD94] C. Y. Tsui, M. Pedram, C. Chen, and A. M. Despain. Low Power State Assignment Targeting Two- and Multi-level Logic Implementations. In *Proc. of ICCAD*, pages 82– 87. ACM/IEEE, 1994.

- [Tya96] A. Tyagi. Integrated Area-Power Optimal State Assignment. In Proceedings of the Synthesis and System Integration of Mixed Technologies, SASIMI '96, pages 24– 31. SASIMI, Seiei Insatsu, Osaka, Japan, November 1996.

# Instruction Scheduling for Low Power Dissipation in High Performance Microprocessors

Mark C. Toburen Thomas M. Conte Department of Electrical and Computer Engineering North Carolina State University Raleigh, North Carolina 27695-7911 {mctobure, conte}@eos.ncsu.edu

> Matt Reilly Digital Equipment Corporation Shrewsbury, Massachusetts reilly@rock.enet.dec.com

### Abstract

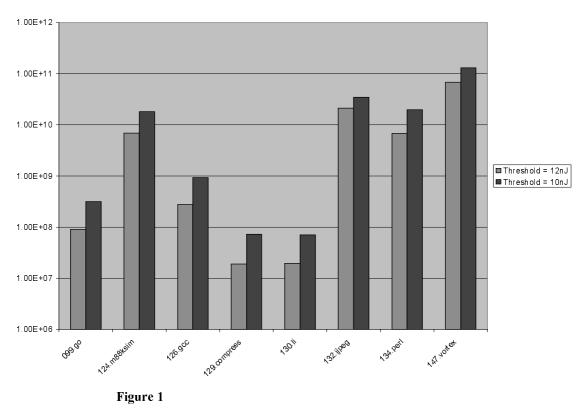

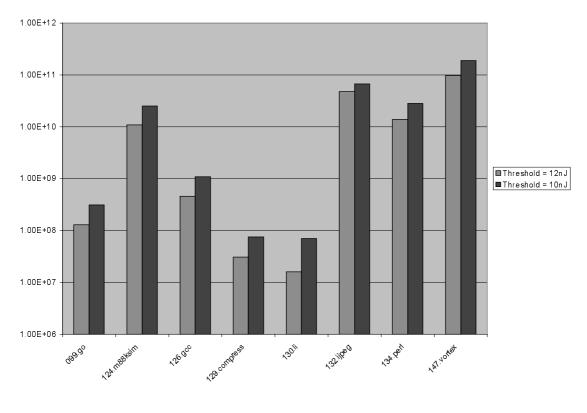

Power dissipation is rapidly becoming a major design concern for companies in the high-end microprocessor market. The problem now is that designers are reaching the limits of circuit and mechanical techniques for reducing power dissipation. Hence, we must turn our attention to architectural approaches to solving this problem. In this work we propose a method of instruction scheduling which limits the number of instructions which can be scheduled in a given cycle based on some predefined per cycle energy dissipation threshold. Through the use of a machine description [8], [9] we are able to define a specific processor architecture and along with that an energy dissipation value associated with each functional unit defined therein. Through careful inspection, we can define the cycle threshold such that the maximal amount of energy dissipation can be saved for a given program while incurring little to no performance impact.

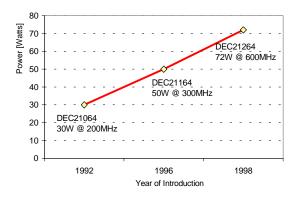

# 1 Introduction

Power dissipation is becoming a vital design issue in today's high-end microprocessor industry. Two examples of high-end processors that suffer from high levels of power dissipation are the DEC 21164a and 21264 The 21164a runs at a clock speed of 600 MHz while dissipating 45.5 Watts of power. The 21264 suffers even worse with internal clock speeds which can reach 666 MHz while dissipating 72 Watts. The problem now is that as power dissipation continues to rise, we are rapidly approaching a point where we will be forced to use cooling techniques which are not suitable for today's personal computers, workstations, and low-end to mid-range servers such as liquid immersion or jet impingement. Circuit designers and thermal engineers have produced some excellent techniques for keeping power dissipation to a minimum in recent years. Clock gating, power supply reduction, smaller

process technology, and state of the art packaging are all examples of the approaches that have been used to date to eliminate the power dissipation problem. However, these approaches are reaching their limitations as the demand for processors with higher clock speeds and denser transistor counts continues to rise.

In this work we propose an architectural/compiler approach towards solving this problem. One way we can reduce peak power dissipation is by preventing the occurrence of current spikes during program execution. If a region of code has a heavy profile weight and contains one or more instructions which require significantly more energy than others, then the execution of this region will lead to repeated current spikes in the processor which results in increased power dissipation. Our goal is to prevent this from occurring by limiting the amount of energy that can be dissipated in any given cycle. Because of schedule slack, this often results in little or no performance impact. In our scheduling model, we schedule as many instructions as possible in a given cycle until the cycle threshold is violated. Once that point is reached, we move on to the next cycle and resume scheduling with the instruction that caused the violation in the previous cycle.

#### 1.1 Previous Work

There have been previous attempts at using scheduling techniques to reduce total power consumption. Su, Tsui, and Despain proposed a technique which combined Gray code addressing and a method called *cold scheduling* to reduce the amount of switching activity in the control path of high performance processors, [1]. Used in conjunction with the traditional list scheduling algorithm, cold scheduling schedules instructions in the ready list based on highest priority. Priority of an instruction is determined by the power cost when the instruction. The power cost is taken from a power cost table which holds power entries, S(I,J), corresponding to the switching activity caused by the execution of instruction I followed by instruction J. Instructions in the ready list with lower power costs have higher priority. After each instruction is scheduled, the power cost of the remaining instructions in the ready list has to be recalculated before scheduling the next instruction. The drawbacks to the cold scheduling approach are obvious. First, a large table is required to hold power costs for all possible instruction combinations. For a high performance processor with a complex instruction set, this table can be extremely large. Second, this table must be accessed for all instructions in the ready list after each new instruction is scheduled. This will make the scheduling process itself slower. However, Su, Tsui, and Despain show that the combination of Gray code addressing and cold scheduling results in a 20-30% reduction in switching activity for the control path.

Another scheduling technique for reducing power consumption was presented by Tiwari, Malik, and Wolfe, [2], [3]. The goal in these works is to schedule code such that instructions are more judiciously chosen as opposed to instruction reordering. In this approach, actual current measurements were taken on general-purpose processors and DSP processors. Current was measured for each instruction and a power table built for single instruction values as well as values for common paired instructions. Then based on these measurements, test programs were rescheduled to use instructions which result in less power consumption. This selection is based on a number of issues such as register accesses as opposed to memory accesses and lower latency instructions. Tiwari, et al., also take into consideration what they term circuit-state overhead which is the switching activity between a pair of specific instructions. In [2] and [3], they argue that for the processors tested that circuit-state overhead is insignificant. However, a detailed analysis of another DSP processor [4], found that circuit-state overhead was much more significant in determining the energy consumption of a pair of instructions. Through this approach of physical measurement and code rescheduling, energy savings up to 40% were achieved on the benchmarks used. Again the problems with this approach are glaring. The process of hand measuring current for all instructions and instruction pairs, while extremely valuable, is extremely time consuming especially in light of the enormous instruction sets used in some of today's high-performance processors. Also, like Su, et al., there is a large table needed to store all power values. This can lead to costly accesses during the scheduling process.

The scheduling approach proposed here is focused on reducing power dissipation as opposed to power consumption. One advantage that our approach provides is that we can explicitly control the amount of power dissipation allowed for any given schedule. The two prior works simply limit power consumption as best they can. In our approach we determine how much power is dissipated which gives us tremendous flexibility in terms of being able to control dissipation for different architectures.

The remainder of this work presents our method of low-power scheduling. Section 2 presents the algorithm itself along with a discussion of the machine description mechanism. Section 3 presents the results of our preliminary investigation into this approach, and in Section 4 we conclude the paper and present plans for future work. All studies presented in this paper were performed using the experimental LEGO compiler designed by the TINKER Research Group at North Carolina State University.

### 2 Low-Power Scheduling

The goal of traditional scheduling algorithms is to improve performance in terms of execution time. This can be done in a number of ways. Such modern approaches as superblock scheduling [5], hyperblock scheduling [6], and treegion scheduling [7] focus mainly on increasing performance through increasing the amount of instruction-level parallelism in program code. In order to schedule for reduced power dissipation, we are forced to sacrifice some of the performance gains provided by these scheduling algorithms in order to obtain the desired reduction in power dissipation. However, the scheduling approach presented here has shown that significant energy savings can be obtained with minimal reduction in program performance.

In this section the method behind out approach will be presented. First we will discuss the machine description mechanism and how energy values are defined therein. Following will be a discussion of the scheduling algorithm itself.

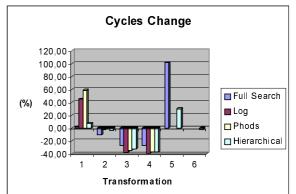

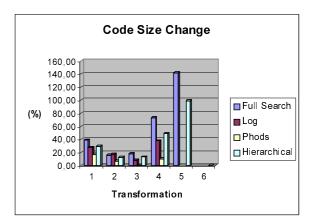

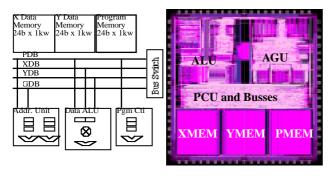

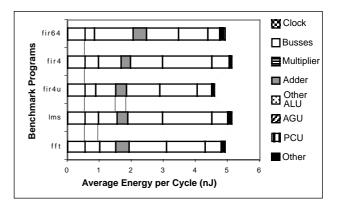

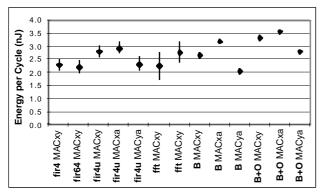

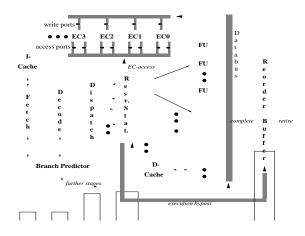

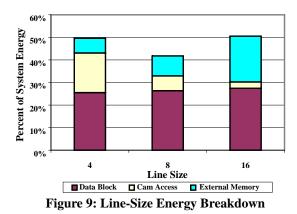

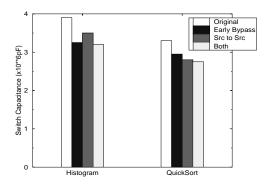

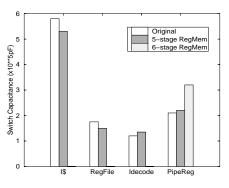

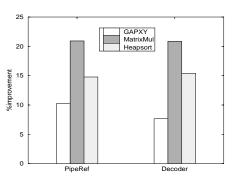

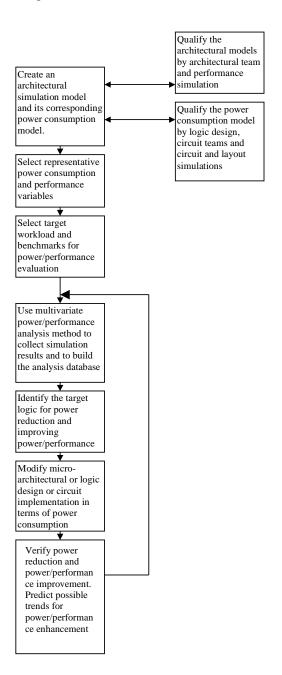

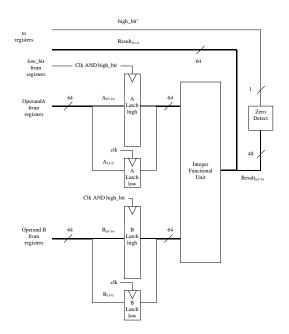

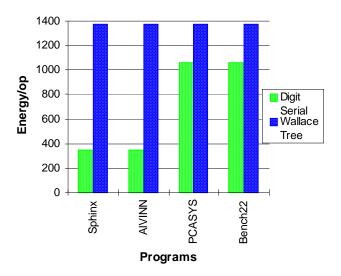

#### 2.1 MDES Machine Description