# 0.61W/mm<sup>2</sup> Resonant Inductively Coupled Power Transfer for 3D-ICs

Sangwook Han and David D. Wentzloff University of Michigan Ann Arbor, MI 48109 USA

Abstract- A high power density wireless inductive power link targeting 3D-ICs and wireless testing is implemented in 65nm CMOS. Its operating frequency is 3.5GHz, the optimal frequency from the trade-off between delivered power and power loss. The link exploits high-Q inductors and resonant inductive coupling to boost the received voltage and maximize the delivered power. A power density of  $0.61 \text{W/mm}^2$  is achieved with  $0.12 \times 0.12 \text{mm}^2$  coils and a  $50 \mu \text{m}$  separation.

# I. INTRODUCTION

3D-IC integration achieves smaller form-factor and low-latency interconnect by stacking multiple die vertically and using through-wafer interconnects such as wireless coupling [1] or through-silicon vias (TSVs) [2] between layers. 3D stacking benefits applications ranging from many-core processors to cubic-mm sensor nodes. Wireless inductive coupling has been demonstrated for signal [3] and power transfer [4][5][6] between 3D-ICs, and is an attractive 3D interconnect solution in particular for processes in which TSV technology does not exist.

Wireless inductive coupling using planar spirals is compatible with nearly all planar processes, allows communication through multiple IC layers, and enables wireless testing to eliminate the Known-Good-Die issue in 3D-ICs. Wireless power transfer using inductive coupling has been demonstrated for 3D-ICs [4][5] and wireless testing [6]. The common drawbacks are less than 100mW/mm<sup>2</sup> power density and less than a 0.1 aspect ratio (ratio of communication distance to coil diameter). These links have used large coils to transmit sufficient power, and separations less than 1/10th the inductor diameter to maximize the coupling coefficient. This paper demonstrates a wireless power transfer link with 0.61W/mm<sup>2</sup>-power density with a simulated aspect ratio of 0.4 in a TSMC 65nm CMOS process. This is achieved by using resonant inductive coupling (RIC), operating at higher frequency for increased coupling coefficient, and a cross-coupled rectifier circuit that benefits from the larger voltage as a result of RIC. This paper presents the design of the inductively coupled link and rectifier, and a comparison with standard inductive coupling (SIC) that highlights the improvement of RIC.

Fig. 1 illustrates the concept of stacking 3D-ICs and using wireless power transfer between layers. Coils are implemented in heterogeneous layers, aligned face-up, and stacked at the wafer level. After dicing, only the top layer has exposed pads for bonding, and all lower layers are wirelessly connected and powered.

Fig. 1. Concept of the wireless inductive power link.

### II. CHANNEL MODELING

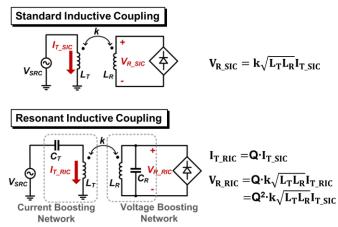

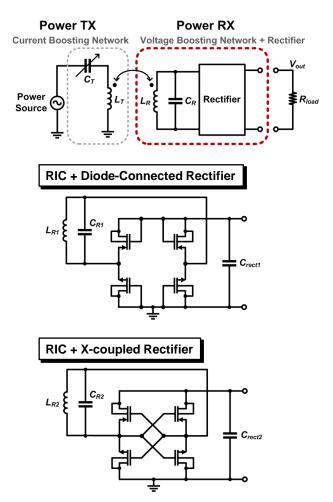

Fig. 2 shows the schematics of a standard inductive coupling (SIC) link and an RIC link. Operating an inductively coupled system at resonance increases the amount of magnetic flux linked between the coils and enhances the ratio of energy delivered to energy consumed in parasitic resistance in the coils [7]. This results in a significant improvement in power transmission, especially at long distances when coupling is low. Fig. 2 shows the improvement of RIC compared to SIC. In a transmitter using RIC, the current  $I_T$  and thus the magnetic flux increases by xQ at the resonant frequency of the series LC tank. This results in an xQ larger voltage  $V_R$  induced in the receiving coil. Furthermore,  $V_R$  is boosted by xQ at the resonant frequency of the receiver LC tank using RIC. Therefore, when the transmitter and receiver resonant frequencies are matched, the received voltage increases by  $xQ^2$ . Because the peak voltage at the receiver is usually a limiting factor of an on-chip rectifier, the boosted voltage can significantly improve range, aspect ratio, and power density.

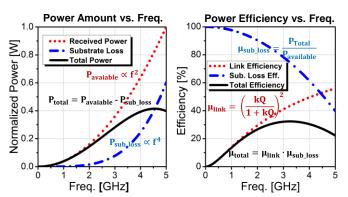

Fig. 3 and Fig. 4 show how the operating frequency and inductor size are selected in order to maximize power density. The power available at the receiver is proportional to  $V_R^2$ , and  $V_R$  is proportional to frequency for current-limited inductive links. Therefore, the available power is proportional to  $\omega^2$ . The power loss depends on  $V_R$ ,  $\omega C_{sub}$ , and  $R_{sub}$ . Since  $V_R$  and  $\omega C_{sub}$  are functions of frequency, the power loss is proportional to  $\omega^4$ , which results in an optimum operating frequency [8]. The net available power after subtracting the loss shows a peak at 4.5GHz. However, the highest power efficiency occurs at 3.5GHz. This frequency is selected, and the inductor is designed so that it has a peak Q-value at 3.5GHz. With fixed

Fig. 2. Resonant inductive coupling for inductive power link.

Fig. 3. Frequency analysis of the inductive power link for high frequency operation.

separation, larger coils will have a higher coupling coefficient k and may typically deliver more power. However, larger coils also have lower self-resonant frequencies and higher  $C_{sub}$ , which means they cannot fully utilize the advantage of high frequency and will have more power loss at the same frequency. To avoid these problems, the inductor size is reduced, decreasing k but providing the best tradeoff with losses.

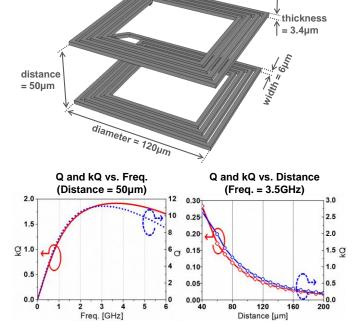

RIC link efficiency is a function of the product kQ [7], therefore a large Q-value can overcome the smaller k due to the reduced coil size. A simulated Q-value of 11 is achieved by using ultra thick metal and an un-doped p-substrate with no metal fill around the coil. In a 3D-IC application, the coupled coils are designed to have a k of 0.18 at a separation of 50 $\mu$ m, which leads to transmit and receive coils that are 120 $\mu$ m-by-120 $\mu$ m. The simulated value of kQ is 1.98, resulting in a link efficiency of 44%.

# III. CIRCUIT DESIGN

A block diagram of the power transfer circuit is shown in Fig. 5. Different from previous links, it has LC tanks to implement RIC: a series LC tank to boost current in the transmitter and a parallel LC tank to boost voltage in the receiver. Two different rectifier circuits are implemented. The typical diode-connected rectifier is made as a benchmark

Fig. 4. Frequency analysis of the inductor design.

circuit, and a cross-coupled rectifier is proposed for higher performance. Both circuits operate at 3.5GHz and use RIC. The transmitter is implemented with a discrete capacitor and wire-wound spiral coil tuned to 3.5GHz, and mounted on a probe station to control its position precisely over the receiver. This demonstrates powering a receiver IC in a wireless testing environment. Simulation results are presented for a transmitter IC using a matched planar spiral for stacked die applications.

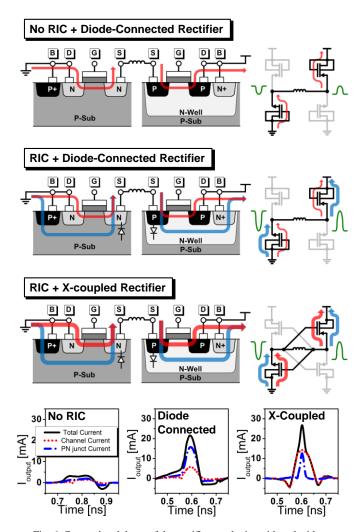

Fig. 6 shows the advantage of the boosted voltage in terms of the current flow. With standard inductive coupling, the nMOS and pMOS channels are weakly depleted, which limits the rectified current. In a diode-connected rectifier with RIC, however, the high voltage enhances not only the channel current but also PN junction forward current. The total current is more than x8 larger compared to SIC at the same separation. Finally, the proposed cross-coupled rectifier further increases VGS and the channel current. This results in a 30% improvement compared to a diode-connected rectifier with RIC and an overall x9 improvement compared to SIC.

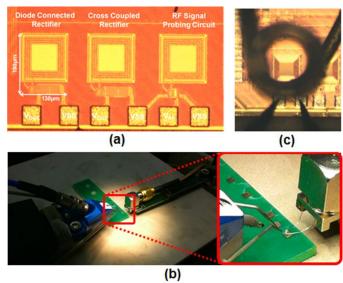

Three different circuits are fabricated in a TSMC 65nm CMOS process with ultra-thick metal and MIM-cap options. All circuits use the same inductor design, with a size of  $120 \times 120 \mu \text{m}^2$ . The rectifier circuits are implemented adjacent to, rather than underneath, the receiving coils, to prevent a decrease in the inductor Q. The rectifiers add an additional area of  $0.008 \text{mm}^2$ . The die photo of them is shown in Fig. 7(a).

# IV. MEASUREMENTS

The inductive power links are tested on a probe station as shown in Fig. 7(b). The power is externally supplied to the transmitter by a signal generator with an input power of

Fig. 5. Schematic of the wireless inductive power link with resonant inductive coupling.

22dBm (158mW). The transmitter is implemented with a series connection of a surface mounted device (SMD)-type capacitor and a wire-wound spiral coil. The coil size is around 200 $\mu$ m and has 3 hand-wound turns with 80 $\mu$ m-thick wire. The resonant frequency of the L and C is 3.5GHz, which is tuned to the same frequency as the receiver coil for implementing RIC. The transmitter is mounted on a probe station so that its position in the x, y, and z-axes can be controlled precisely to overlap the coils each receiver circuit. This transmitter demonstrates wirelessly powering the circuit for e.g. wireless testing. Fig.7 (c) shows photos of transmitting coils over three receiving circuits and measurement results of the transmitting coil.

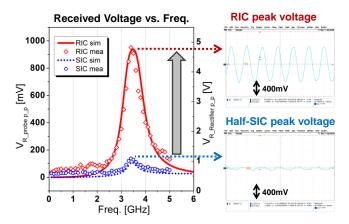

The improvement due to RIC is measured by comparing to a benchmark circuit on the same chip, which has the same LC tank and a high frequency buffer. Fig. 8 shows the measurement results of the RIC improvement over a half-SIC link. Because all circuits share the off-chip transmitter, the benchmark is half-SIC because it uses the same resonant LC tank in the transmitter, but does not implement a resonant tank in the receiver. As expected, RIC shows a more than x3 larger voltage peak at the resonant frequency than the half-SIC link.

Fig. 6. Current breakdown of the rectifier topologies with and without resonant inductive coupling.

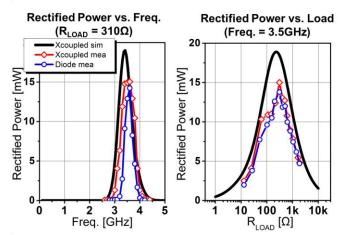

For both rectifiers, the maximum power is achieved at the resonant frequency of 3.5GHz and a load resistance of  $310\Omega$ , as depicted in Fig. 9. The maximum power delivered by the the cross-coupled rectifier is 15mW, resulting in a power density of  $1.04 \text{W/mm}^2$  considering the coil area alone, and  $0.61 \text{W/mm}^2$  including the rectifier circuit, and an efficiency of 9.5%. In comparison, the diode rectifier achieves 13.7 mW, therefore the improvement from the proposed cross-coupled rectifier is 10%.

# V. CONCLUSION

A wireless inductive power link using resonant inductive coupling is presented. The resonant inductive coupling is exploited to boost the received voltage and maximum the transferred power. A power density of  $0.61 W/mm^2$  is achieved with  $0.12 x 0.12 \mu m^2$  coil and  $50 \mu m$  separation. Compared to previous publications, this prototype achieved an improvement of x2.5 in power density and x4 in aspect ratio, as shown in Table I.

Fig. 7. (a) Die photo (b) Measurement Setup (c) aligned transmitting coil

Fig. 8. Benefit of resonant inductive coupling with simulation and measurement results.

Fig. 9. Measurement results depending on load resistance and frequency.

# REFERENCES

- [1] N. Miura, *et al.*, "A 1 Tb/s 3 W Inductive-Coupling Transceiver for 3D-Stacked Inter-Chip Clock and Data Link," IEEE *JSSC*, Jan. 2007.

- [2] H. Chung, et al., "8 Gb 3-D DDR3 DRAM Using Through-Silicon-Via Technology," IEEE JSSC, Jan. 2010.

- [3] N. Miura, *et al.*, "A 0.14pJ/b Inductive-Coupling Transceiver with Digitally-Controlled Precise Pulse Shaping, IEEE *JSSC*, Jan., 2008.

- [4] Y. Yuan, et al., "Digital Rosetta Stone: A Sealed Permanent Memory with Inductive-Coupling Power and Data Link", IEEE Sym. on VLSI Circuits, Jun. 2009.

- [5] Y. Yuan, et al., "Simultaneous 6Gb/s Data and 10mW Power Transmission using Nested Clover Coils for Non-Contact Memory Card," IEEE Sym. on VLSI Circuits, Jun. 2010.

- [6] A. Radecki, et al., "6W/25mm2 Inductive Power Transfer for Non-Contact Wafer-Level Testing," IEEE ISSCC, Feb. 2011.

- [7] S. Han, et al., "Wireless Power Transfer Using Resonant Inductive Coupling for 3D Integrated ICs," IEEE 3DIC, Oct. 2010.

- [8] U. Karthau, et al., "Fully Integrated Passive UHF RFID Transponder IC With 16.7-μW Minimum RF Input Power," IEEE JSSC, Oct. 2003.

- [9] K. Onizuka, et al., "Chip-to-Chip Inductive Wireless Power Transmission System for SiP Applications," IEEE CICC, Sep. 2006.

# TABLE I Performance Comparison

|                                           | This Work                                         | Onizuka<br>CICC '06 [9] | Yuan<br>VLSI '09 [4]  | Yuan<br>VLSI '10 [5]           | Radecki<br>ISSCC '11 [6] |

|-------------------------------------------|---------------------------------------------------|-------------------------|-----------------------|--------------------------------|--------------------------|

| Received Power                            | 15mW                                              | 2.5mW                   | 14mW                  | 10mW                           | 6W                       |

| Coil Size                                 | 0.12x0.12mm <sup>2</sup>                          | 0.7x0.7mm <sup>2</sup>  | 2x2mm <sup>2</sup>    | $0.7 \text{x} 0.7 \text{mm}^2$ | 5x5mm <sup>2</sup>       |

| Distance                                  | 50μm                                              | n/a ( <20μm)            | 200μm                 | 20μm                           | 50~320μm                 |

| Aspect Ratio<br>(Distance / Coil<br>Size) | 0.42                                              | <0.029                  | 0.1                   | 0.029                          | <0.064                   |

| Power Density                             | 1.04W/mm² (Coil only)<br>607mW/mm² (All Circuits) | 5.1mW/mm <sup>2</sup>   | 2.5mW/mm <sup>2</sup> | 20mW/mm <sup>2</sup>           | 240mW/mm <sup>2</sup>    |

| Power Efficiency                          | 19%                                               | -                       | 4.1%                  | 10.2%                          | 17%                      |

| Carrier Frequency                         | 3.5GHz                                            | 150~350MHz              | 250MHz                | -                              | 150MHz                   |

| Technology                                | 65nm CMOS                                         | 0.35μm CMOS             | 0.18μm CMOS           | 65nm CMOS                      | 0.18μm CMOS              |