# HIGH Q InP-BASED VARACTOR DIODES

# T. David\*, S. Arscott, P. Mounaix, X. Mélique, F. Mollot, O. Vanbésien, M. Chaubet and D. Lippens

Institut d'Electronique et de Microélectronque du Nord (UMR 8520)

Université des Sciences et Technologies de Lille

BP 69, 59652 Villeneuve d'Ascq, France

M. Chaubet is with the Centre National d'Etudes Spatiales,

18 Avenue Edouard Belin,

31401 Toulouse Cedex 4, France

\*Corresponding author: thibaut.david@iemn.univ-lille1.fr

Abstract -We report on high quality-factor Heterostructure Barrier Varactor making benefit of epitaxial stacking and planar integration, with a cut-off frequency in the far infrared region. To this aim, high doping concentrations in the depletion (2x10  $^{17}~\rm cm^{\text{-}3}$ ) and contact (1x10  $^{19}\rm cm^{\text{-}3}$ ) InGaAs regions lattice matched to an InP substrate and an InAlAs/AlAs blocking barrier scheme were used. Planar integration of the devices with a number of barriers up to eight in coplanar waveguide and series-type configurations shows a zero-bias capacitance of 3.4 fF/µm² per barrier and a conductance of 3.3 nS/µm² along with an intrinsic capacitance ratio of 4.3:1.

*Index terms -*Varactor diode, harmonic multiplier, heterostructure, substrate-transfer, InP

### I. Introduction

Recently, we reported record performances in terms of conversion efficiency (12.5%) and delivered power (9mW) for a waveguide Heterostructure Barrier Varactor tripler at 250 GHz [1]. These state-of-the art performances can be explained by the use of InP-based materials, which permit us to dramatically improve the voltage handling of the devices by reducing the leakage current [2] increasing by this fact the intrinsic quality factor of the devices. Also, the use of narrow gap cladding and contacting layers were found to be of great benefit in achieving a high modulation velocity of the depleted region [3] and for reducing the series resistance contribution to the cut-off frequency. In order to further increase these performances in terms of frequency and power capability, some improvements were subsequently brought to the epitaxial layers and to the technology aiming at (i) further increasing the current capability of the devices in the undepleted zone alleviating by this means the saturation effect at higher operation frequencies [3] and (ii) reducing the intrinsic series resistance through the use of highly-degenerated thick access and contact layers. In addition, the functionality of the device for a use as a medium-power high-frequency multiplier was improved with the fabrication of air-bridged devices in double and quadruple mesa configurations, with two barriers being stacked during epitaxy. This means that the overall number of elemental devices can be as high as eight. In this communication, we report on the dc and ac characterization of this new batch of devices integrated in: planar coaxial schemes, coplanar waveguide (CPW) and planar series-type configurations.

### II. TECHNOLOGICAL GUIDELINES

The epitaxial material used for fabricating the devices starting from a Semi-Insulating InP substrate, consists of: (i) a 1µm-thick 1x10<sup>19</sup> cm<sup>-3</sup> InGaAs buried layer, (ii) a 200nm-thick 2x10<sup>17</sup> cm<sup>-3</sup> InGaAs cladding layer, (iii) an undoped InAlAs-5nm/AlAs-3nm/InAlAs-5nm barrier, (iv) a 200nm-thick 2x10<sup>17</sup> cm<sup>-3</sup> InGaAs cladding layer and (v) a 500nm-thick 1x10<sup>19</sup> cm<sup>-3</sup> InGaAs capping layer. The Indium content is 53% and 52% for InGaAs and InAlAs respectively, whereas the strained AlAs layer was grown under pseudomorphic conditions. A two barrier-scheme, namely the series integration of two elemental diode structures during epitaxy, was grown without interruption. A higher doping concentration (twice that in previous work [4]) with thicker buried layers was chosen for this batch despite the difficulty to grow under lattice matching thick ternary InGaAs alloys. The epitaxial quality was found to be instrumental in order to achieve the high quality factor device. This fact explains why the AlAs layer thickness was kept at 3nm (3D growth was found for 5nm AlAs layers) hence, two barriers were integrated.

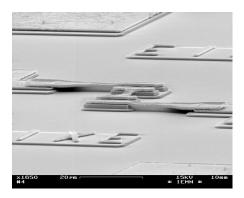

Figure 1: SEM view of an eight-barrier device. The air-bridges, 3μm-width, 40 μm-long and 0.8 μm-thick, were fabricated by photoresist molding techniques and electron gun evaporation.

## III. INTEGRATION TECHNIQUES

The devices were fabricated for the realization of harmonic triplers at J band (220-325 GHz). Also a more prospective project targeting the integration of the diodes in a non-linear transmission line was investigated. With respect to these goals, it was decided to further integrate the devices by taking advantage of a planar integration in close proximity by low dimensional air-bridge connection. To this aim, advanced fabrication techniques were employed which consist in the writing of the micron-

sized dimension top contacts by electron beam (PMMA resist), the ohmic contact deposition by electron gun evaporation (a sequential Ni/Ge/Au/Ti/Au multilayer ohmic contact annealed by RTA at  $400^{\circ}$ C during 40 s), the etching of mesas by Reactive Ion Etching (CH<sub>4</sub>/H<sub>2</sub>/Ar gases) and the fabrication of evaporated air-bridges using a double resist layer molding scheme. The underneath resist layer was pyrolized in order to achieve a convex mold shape and avoid resist mixing [5]. Figure 1 shows a Scanning Electron Micrograph of a completed device. For the present example, the number of barriers was eight (2 epitaxially × 4 mesas in series).

#### IV. DC AND AC MEASUREMENTS

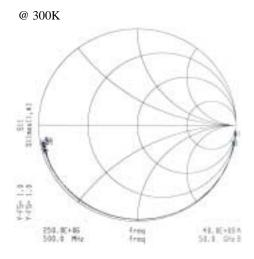

For the characterization of the devices, we took advantage of various transmission line topologies. The outputs are the values of the small signal equivalent circuit, which permits one to subsequently simulate the large signal behavior of the devices under large signal conditions by a harmonic balance method. Also the electromagnetic (EM) behavior of the devices can be assessed using EM codes combined with network analysis through the use of scattering matrix [6]. The intrinsic elements, namely the level of conductance, which describes the leakage current through (tunneling effects) and over (thermionic emission) the barrier along with the intrinsic capacitance non-linearity, can be obtained using the coaxial type configuration (see Figure 5). Figure 2 shows the locus of the complex reflection coefficient versus frequency between 500 MHz and 40 GHz at zero-bias. A near pure capacitive behavior is apparent in this figure. The real part of the impedance was found to be as low as  $0.8~\Omega$ , irrespective of the applied bias.

Figure 2: Plot on Smith chart of the frequency dependence of the reflection coefficient at zero-bias for a coaxial-type device configuration ( $\varnothing$  20  $\mu$ m).

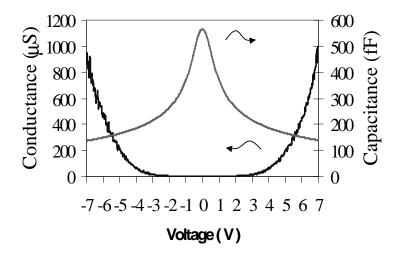

These measurements can be used for investigating the intrinsic capacitance-voltage characteristics whose examples are shown in Figure 3. The devices exhibit an excellent symmetry with respect to the Y-axis. For this dual barrier scheme the zero-bias capacitance is 1.7 fF/ $\mu$ m<sup>2</sup>. At 8V the capacitance reaches practically its saturation value of 0.39 fF/ $\mu$ m<sup>2</sup>, yielding a capacitance ratio of 4.3:1. Concerning the leakage current, which is characterized by the conductance-voltage plot (also shown in Figure 3), we found a value of 1.37 $\mu$ S/ $\mu$ m<sup>2</sup> at the reference voltage of 6 V, which corresponds to an increase in the conduction mechanisms due to impact ionization in the 2×10<sup>17</sup> cm<sup>-3</sup> InGaAs (Eg =0.8 eV) cladding layer. The quality factors at 5 GHz are 20800 (0V), 2720 (2V), 80 (4V), 11(6V) respectively. By assuming a predominance of displacement current (J<sub>D</sub>) for J<sub>D</sub>/J<sub>C</sub>= 10:1 (J<sub>C</sub> being the leakage current) it is believed that the diode could operate correctly under a full 8V peak to peak pump voltage @ 250 GHz.

Figure 3: Measured capacitance and conductance-voltage characteristics for a two-barrier coaxial-type device ( $\emptyset$  20  $\mu$ m).

### V. INFLUENCE OF DOPING CONCENTRATION

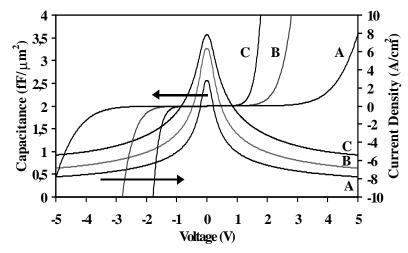

In order to have further insight into the capacitance-voltage relationship when the doping concentration is varied, we show in Figure 4 the simulated capacitance-voltage curves for a one barrier scheme. In order to obtain these data, we solved the Poisson equation in the Thomas-Fermi approximation. This means that the charges resulting from the leakage current are neglected (zero-current approximation). The electronic charges in the accumulation layer, which are trapped in front of the blocking barrier, can be calculated using a semi-classical distribution function.

| Doping (cm <sup>-3</sup> ) | 1×10 <sup>17</sup> | 2×10 <sup>17</sup> | 4×10 <sup>17</sup> |

|----------------------------|--------------------|--------------------|--------------------|

| $C_0 (fF/\mu m^2)$         | 2.6                | 3.25 (3.4)         | 3.6                |

| Csat (fF/\(\mu\)m^2)       | 0.4                | 0.65 (0.78)        | 0.9                |

| C <sub>0</sub> / Csat      | 6.5:1              | 5:1 (4.3:1)        | 4:1                |

Table 1: Summary of C-V characteristics in terms of zero-bias  $(C_0)$ , capacitance saturation  $(C_{sat})$  and capacitance ratio. The measured data are in brackets.

Further details on the assumptions and the numerical procedure can be found in ref [7]. A comparison between calculated and measured data (shown in brackets in table 1), for the 2×10<sup>17</sup> cm<sup>-3</sup> doping concentration, gives a satisfactory agreement and supports the validity of calculations. With respect to the trends, as a function of the doping concentration, it can be noted, as expected, that any increase in the donor concentration degrades the capacitance contrast with a concomitant increase in the capacitance level. However such a degradation is of minor importance in comparison with the associated benefit in terms of current capability.

Figure 4: Simulated capacitance and current-density characteristics for different doping concentrations (single barrier),  $A=1\times10^{17}$  cm<sup>-3</sup>  $B=2\times10^{17}$  cm<sup>-3</sup> ,  $C=4\times10^{17}$  cm<sup>-3</sup> .

From the leakage current point of view, a degradation of voltage handling can be observed. Therefore for a 8 A/cm<sup>-2</sup> reference, the breakdown voltages are 5V (1×10<sup>17</sup>), 2.8V (2×10<sup>17</sup>) and 1.9V (4×10<sup>17</sup>), respectively. Tunneling effects through the barrier are responsible for the leakage current at moderate voltages whereas the breakdown effect can be explained by impact ionization in the adjacent low gap layer. Increasing the doping concentration strengthens both leakage mechanisms via an increase in the Fermi level and the internal electric field in the InGaAs layer. On the basis of this study carried out on a single barrier device, which takes the doping concentration as a parameter, the benefit of epitaxial and/or planar stacking is quite

obvious by preserving the voltage handling of the device and a capacitance level which are compatible with high frequency operation. However, in order to alleviate the decrease in the capacitance ratio, it is believed that other routes have to be chosen, notably those involving planar doping or pre- and post-well configurations. In both cases, the basic idea is to shorten the screening length by accumulating electrons closer to the barrier (quantum well scheme or delta doped concentration). Both techniques have respective advantages and some conclusions can be found in ref [8] and [9].

#### VI. DE-EMBEDDING AND FURTHER IMPROVEMENTS

The capacitance variations can also be recorded for the CPW and series type configurations. For the latter, which have to be "flip-chip" mounted in the tripler blocks, there are no coplanar footprints for wafer probing of the devices, only pads. In this particular case, two of the three probes were used to contact the two pads facing each other. It can be shown that this kind of arrangement gives experimental data sufficiently accurate for de-embedding an equivalent circuit, which now takes into account, not only the intrinsic elements, but also the parasitics depending on the topology of the diodes.

These parasitics are the self-inductance and the pad-to-pad and bridge-to-pad capacitances, due to interconnections and the series resistance. A knowledge of these parameters is of prime importance for accessing the capability of the device for use in a tripler block, and for operating at very high frequency via the cut-off frequency. Ideally, special patterns have to be planned in the mask set to help in the derivation of parasitics. Notably a TLM pattern is generally set in the test field along with open-circuit (Cp) and air-bridged pads (Lp). Short-circuited devices yielded a self-inductance value in the 60 pH range for a single device whereas the capacitance parasitic value was found in the 20 fF range, with a large uncertainty due to the calibration and error measurements of reflection coefficients.

It can be shown, provided no extra resistive term was added, that the tripler efficiency is not affected by the reactive elements. This is true only for a perfect matching of the large signal admittance of the diode to the circuit, which is not always satisfied in practice. Improvements in the parasitics were demonstrated over the past through an optimized topology and/or the surface channel technology [10]. Deep etching was not performed here explaining why the parasitic capacitance is relatively high. This can be envisaged on the basis of Schottky technology carried out at the University of Lille [11] for which a post-process deep-etch was conducted, aimed at lowering the value of Cp.

Another key figure of merit is the series resistance. With respect to this specific issue, encouraging results were shown in Figure 2 with value as low as  $0.8~\Omega$  being observed. However, a major drawback associated with the planar integration of series type devices, instead of full epitaxial stacking, stems from an increase in the series resistance. The overall series resistance increases as the number of interconnected

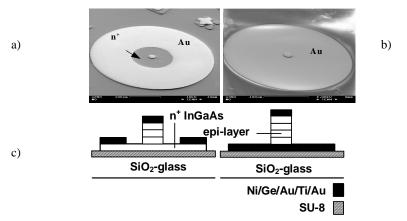

devices increases, due to the combination of vertical and planar topologies. Reducing the total series resistance can be achieved by reducing the "spreading resistance", which is believed to be a major contribution towards r<sub>s</sub>. There are currently two methods to achieve this goal: increasing the epitaxial thickness of the buried n+ layer [12] and/or increasing the doping density of this layer. In our current work, we kept the thickness to 1 µm since increasing this thickness to several microns is not technologically realistic using MBE growth, whilst we increased the doping density to  $1x10^{19}$  cm<sup>-3</sup>. We believe that the low value of the series resistance, which was observed in our measurements, is a direct consequence of the elevation of this doping density. Remembering that the n+ layer serves two purposes (i) ohmic contacts and (ii) mesa interconnect, another potential method is to introduce a transfer step [13]. Prior to this transfer, a gold layer can be deposited, this metallic layer can now function as the mesa-contacting layer. By these means we have greater control over the device topology. Therefore a quasi-vertical topology can be achieved. In the past such a scheme had been attempted by taking benefit of substrate-less technology [14]. However such a technology was found to be very difficult to fabricate practically whereas a transfer technique onto a host substrate could avoid most of the difficulties encountered with free standing membrane structures having post-metallization. In order to illustrate the advantages afforded by a substrate-transfer process onto a host quartz substrate, Figure 5 shows an SEM view and corresponding schematics of two transferred devices. In the type I configuration, the "spreading resistance" dominates the value of r<sub>s</sub>, whereas in the type II configuration, a vertical current flow is preserved so that an improvement in the series resistance can be pointed out. Details of the technology of SU-8 grafting techniques and RF assessment can be found in [15].

Figure 5: SEM view of various topologies of transferred HBV devices (a) **type I**: n<sup>+</sup>mesa-contact, (b) **type I**: gold mesa-contact and (c) schematics of both topologies.

#### V. CONCLUSION

New degrees of freedom in the fabrication of high performance devices were afforded by epitaxial stacking and planar integration, which open the way to a full 3D integrated solid-state multiplier. The advantage of a series type connection was demonstrated with a zero-bias capacitance as low as  $0.425 \text{ fF/}\mu\text{m}^2$  for a eight-barrier scheme, while preserving a capacitance ratio of 4.3:1.

A significant degradation of the series resistance  $(r_s)$  was noted for air-bridge contacted devices with respect to vertical devices which exhibit a record  $r_s$  as low as 0.8  $\Omega$ . Nevertheless it is believed that intrinsic cut-off frequencies in the far infrared region can be achieved owing to the drastic decrease in the capacitance level. High quality factors have been obtained together with a high power handling capability. A different device topology is also proposed, which could lead to a further reduction in the value of  $r_s$ . This has been made possible by using substrate-transfer techniques.

#### VI. ACKNOWLEDGMENTS

The authors would like to thank E. Delos and S. Lepilliet for their help during the characterization.

This work was supported by CNES contract # 714/98/CNES/7280/00 and ESA contract # 13927.99.

# VII. REFERENCES

- [1] X. Mélique, A. Maestrini, P. Mounaix, M. Favreau, O. Vanbésien, J.M. Goutoule, G. Beaudin, T. Nähri and D. Lippens, "Record performance of a 250 GHz InP-based heterostructure barrier varactor tripler", Electronics Letters, vol. **35**, n°11, pp. 938-939, May 1999 and to be published in IEEE Microwave Theory and Techniques, June 2000.

- [2] J. Stake, L. Dillner, S. Jones, C. Mann, J. Thornton, J. Jones, W. Bishop and E. Kollberg, "Effects of Self-heating on planar heterostructure barrier varactor diodes", IEEE Transactions on Electron Devices, vol. **45**, n°45, pp.2298-2303, 1998.

- [3] E. Kollberg, T. Tolmunen, M. Frerking, and J. East, "Current saturation in submillimeter wave varactors", IEEE Transactions Microwave Theory and Techniques, vol. **40**, n°5, p.831, May 1992.

- [4] E. Lheurette, P. Mounaix, P. Salzenstein, F. Mollot and D. Lippens, "High performance InP-based heterostructure barrier varactor in single and stack configuration", Electronics Letters, vol. 32, n°15, pp.1417-1418, July 1996.

- [5] G. Porkolab, Y Chen, S. Tabatabaei, S. Agarwala, F. Johnson O. King, R. Frizzel, W. Beard and D. Stone, "Air-bridges, air-ramps, planarization, and encapsulation using pyrolitic photoresist in the fabrication of three dimensionnal microstructures", J. Vac. Sci. Technol., vol. B **15**, n°6, pp.1961-1965, Nov/December 1997.

- [6] J. Carbonell *et al*, Proceedings of the "28<sup>th</sup> European Microwave Conference", Amsterdam, The Netherlands, 1998.

- [7] R. Harvart, E. Lheurette, O. Vanbésien, P. Mounaix, F. Mollot and D.Lippens, "Step-like heterostructure barrier varactor", IEEE Transactions on Electron Devices, vol. **45**, n°11, pp. 2291-2297, November 1998.

- [8] V. Duez, X. Mélique, O. Vanbésien, P. Mounaix, F. Mollot and D.Lippens, "High Capacitance ratio with GaAs/InGaAs/AlAs heterostructure quantum well-barrier varactor", Electronics Letters, vol. **34**, n°19, pp.1860-1861, September 1998.

- [9] E. Lheurette, X. Mélique, P. Mounaix, F. Mollot, O. Vanbésien and D.Lippens, "Capacitance Engineering for InP-based Heterostructure Barrier Varactor", IEEE Electron Device Letters, vol. 19, n°9, pp.338-340, September 1998.

- [10] S. Marazita, W. Bishop, T. Cunningham, P. Koh, T. Crowe and R. Weikle, "8<sup>th</sup> Symposium on Space Terahertz Technology", Harvard University, March 1997.

- [11] F. Podevin et al, "11th Symposium on Space Terahertz Technology", Ann Arbor, MI, in this issue.

- [12] J. Jones, W. Bishop, S. Jones, G. Hait, "Planar multibarrier 80/240 GHz heterostructure barrier varactor tripler", IEEE Transactions on Microwave Theory and Techniques, vol. **45**, n°4, p. 512, 1997.

- [13] S. Arscott, P. Mounaix and D. Lippens "Transferred In-P based HBVs on glass substrate", Electronics Letters, vol. **35**, n°17, pp.1493-1494, August 1999 and S. Arscott, P. Mounaix and D. Lippens, "Substrate transfer process for InP-based heterostructure barrier varactor devices", J.Vac. Sci. Technol. , vol. B **18**, n°1, pp.150-155, Jan/February 2000.

- [14] A. Simon, A. Crub, V. Krozer, K. Beilenhoff and H. Hartnagel, "4<sup>th</sup> Symposium on Space Terahertz Technology", Los Angeles, CA, USA, pp. 392-403, Mar. 30-Apr. 1 1993.

- [15] S. Arscott, T. David, X. Mélique, P. Mounaix, and D. Lippens, "Towards terahertz circuits via InP micromachining techniques", "12<sup>th</sup> International Conference on Indium Phosphide and Related Materials (IPRM00)", Williamsburg, VA, USA, May 2000.