# EECS 583 – Fall 2012 – Midterm Exam

Monday, November 19, 2012 10:40-12:30: open book, open notes

Name: KEY

Please sign indicating that you have upheld the Engineering Honor Code at the University of Michigan.

"I have neither given nor received aid on this examination."

Signature:

There are 12 questions divided into 3 sections. The point value for each question is specified with that question. Please show your work unless the answer is obvious. If you need more space, use the back side of the exam sheets.

Part I: Short Answer 4 questions, 12 pts total

Score:

Part II: Short Problems 6 questions, 58 pts total

Score:

Part II: Longer Problems 2 questions, 30 pts total

Score:

Total (100 possible):

Page 1 of 8

## Part I. Short Answer (Questions 1-4) (12 pts)

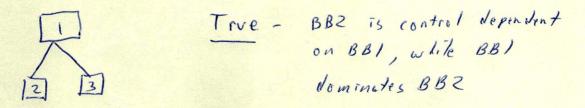

1) A basic block can be control dependent on an edge coming from a *dominating* basic block? Is this statement True or False, briefly explain. (3 pts)

2) Compilers often provide warnings if local variables can be used without first being defined in a function. Circle the standard dataflow analysis provides the best information to issue such warnings. (3 pts)

| Liveness ) | Reaching defs | Available defs | Available exprs |  |

|------------|---------------|----------------|-----------------|--|

|            |               |                |                 |  |

3) When scheduling a basic block, all instructions must be scheduled at their Estart time to achieve the *minimum* schedule length. Is this statement True or False, briefly explain. (3 pts)

False - Instructions can be scheduled in the Finish the busic block with minimum length.

4) Compute the *ResMII* for a loop with 8 memory and 20 arithmetic instructions on a processor with 2 fully pipelined MEM units and 3 fully pipelined ALUs. (3 pts)

Re, MII:

$$max\left(\left\lceil \frac{8}{2} \right\rceil, \left\lceil \frac{20}{3} \right\rceil\right) = 7$$

BBG

# Part II. Short Problems (Questions 5-10) (58 pts)

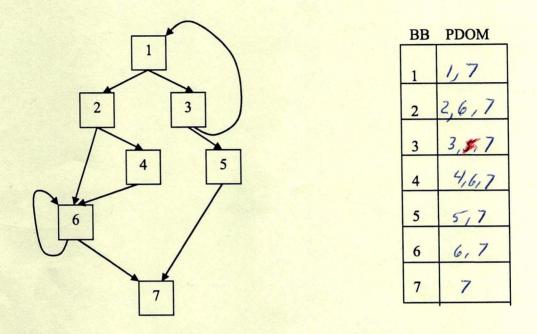

5) Compute the post dominator (PDOM) set for each basic block in the following control flow graph. (5 pts)

6) Draw the control flow graph (CFG) and determine the *minimum* number of predicates required to if-convert the code. (10 pts)

BBI =0 i = 0;do { if (A[i] && A[i]->b && A[i]->b->c) BDZ x++; else y++; BB3  $\} while (++i < 100);$ BB CD BBY 1 2 -BAT X++ 3 -2 -3 -4 2,3,4 => 4 unique CD sets => 4 predicides 4 -3 y++ 5 6 7 BB7 ++ 1

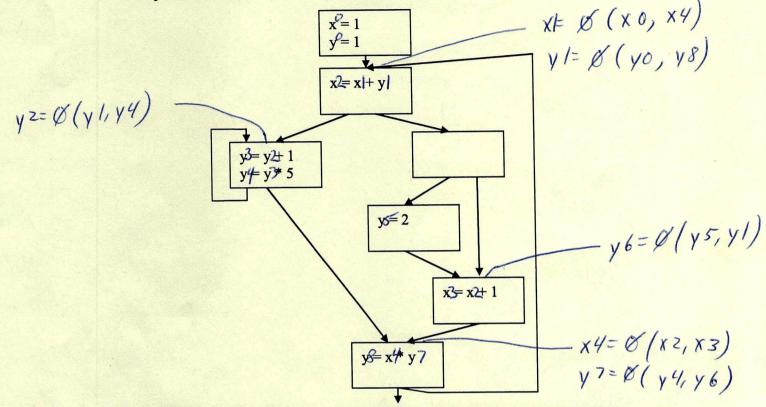

7) Convert the following program segment into static single assignment (SSA) form. You should perform the necessary renames and show the Phi nodes. Solving by inspection is fine and you can put your solution directly on the diagram. (10 pts)

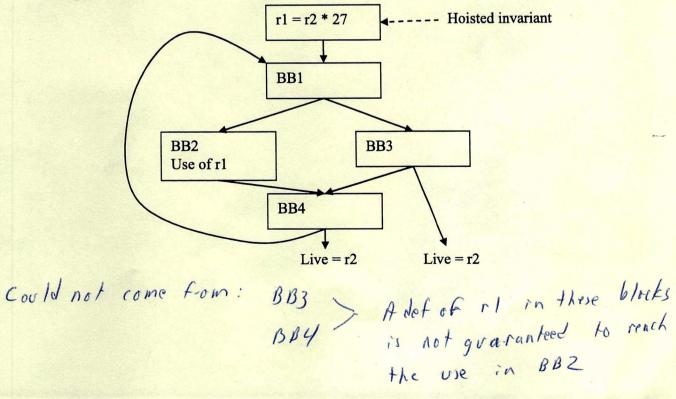

8) In the following loop consisting of basic blocks 1-4 with 2 exit points, LICM has been applied to the instruction "r1 = r2 \* 27". Assuming the optimization was legal, which block(s) could *not* be the original home of the invariant instruction? Explain. (8 pts)

9) Generate the II=4 modulo schedule for the following dependence graph and processor model. Show the unrolled and rolled schedules for your answer. You can assume that instruction 1 is the highest priority, 2 is second highest, etc. and you do not need to assign staging predicates. (15 pts)

Processor model 2 fully pipelined function units 1 ALU, 1 MEM

Instructions 1 and 2 are memory Instructions 3, 4, 5 and 6 use the ALU Instruction 6 is the branch

Unrolled Scholule

| 1           |

|-------------|

| instruction |

| 1           |

| 2           |

| 5           |

|             |

| 3           |

|             |

|             |

|             |

|             |

| 4           |

|             |

| 6           |

|             |

Rolled Schelule

| time | instruction |

|------|-------------|

| 0    | 1,3         |

| 1    | 2,4         |

| 2    | 5           |

| 3    | 6           |

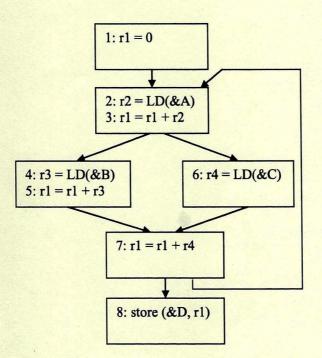

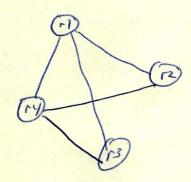

10) Consider the following code segment. How many physical registers are necessary to allocate virtual registers r1, r2, r3, r4 without spilling? Assume that &A, &B, &C, and &D are compile time constants and do not require registers. Justify your answer. (10 pts)

$$LR(r1) = 1, 2, 3, 4, 5, 6, 7, 8$$

$$LR(r2) = 2, 3$$

$$LR(r3) = 4, 5$$

$$LR(r1) = 6, 7, 2, 3, 4, 5$$

| 1 |           |     |          |

|---|-----------|-----|----------|

| 3 | registers | are | required |

### Part III. Longer Problems (Questions 11-12) (30 pts)

11) Suppose that you are given a new dataflow problem, MustDef. At a point p in a program, MustDef is defined as the set of variables that are guaranteed to be defined along all paths from ENTRY to p.

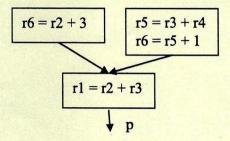

So for example, at point p, MustDef contains r1 and r6, but not r5.

Define the set of dataflow equations to solve for MustDef. You should define GEN, KILL, IN, and OUT. (15 pts)

This analysis is similiar to available definitions, but of the variables rather than the actual instructions.

IN/OUT calculation

while (change) for each basic block, X  $\mp N(X) = \Lambda (OUT(Y)), for all predetersons$ yot X $OUT(X) = <math>\epsilon EN(X) + (EN(X) - K/LL(X))$

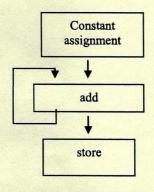

12) You are the professor in a compiler construction class and have to write an exam question on optimization. Create a small pseudo assembly function which reduces to three instructions: a constant assignment, an add, and a store, each in its own basic block with the implied control flow as shown below. Note: you do not need to include a branch instruction. You should use the optimizations listed below, they must be applied once each (exhaustively), in an order selected by you.

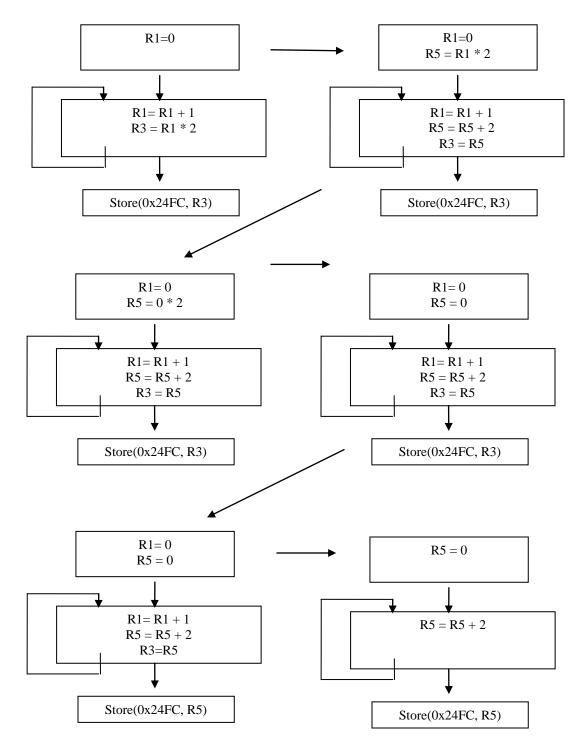

Create the answer key by showing the code before and after each optimization. Assume that each optimization must fire at least <u>one time</u>. You may use all or a subset of  $\{r1, r2, r3, r4, r5\}$  as extra registers, and your starting code *should not contain any dead code*. (15 pts)

Code template after all optimizations

#### **Optimizations:**

Constant folding Dead code elimination Constant propagation Induction variable strength reduction Copy propagation Many possible answers... Induction variable strength reduction is a good candidate to go first as it creates additional instructions.

Order: Strength reduction, constant prop, constant folding, copy prop, dead code elimination