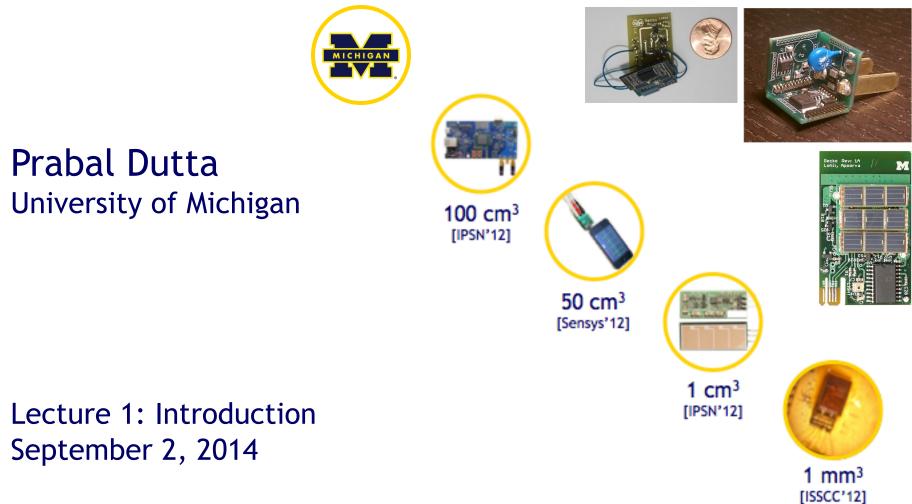

# EECS 373 Design of Microprocessor-Based Systems

http://web.eecs.umich.edu/~prabal/teaching/eecs373

1

# What is an embedded system?

#### Embedded, Everywhere

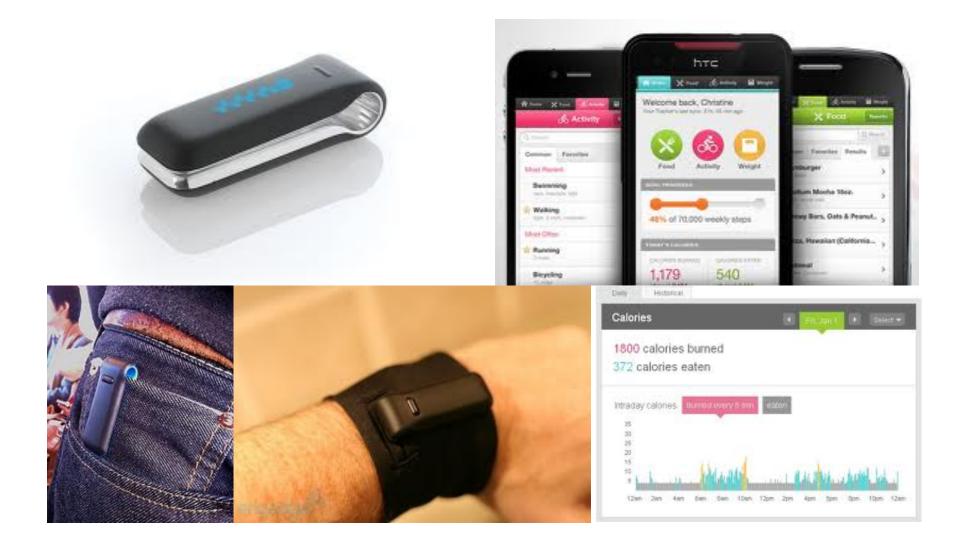

#### Embedded, Everywhere - Fitbit

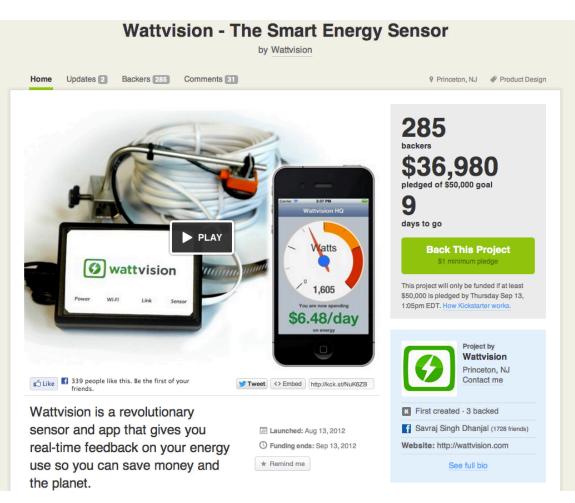

#### Embedded, Everywhere - WattVision on Kickstarter

# What is driving the embedded everywhere explosion?

#### Outline

Technology Trends

**Design Questions**

Course Administrivia

Tools Overview/ISA Start

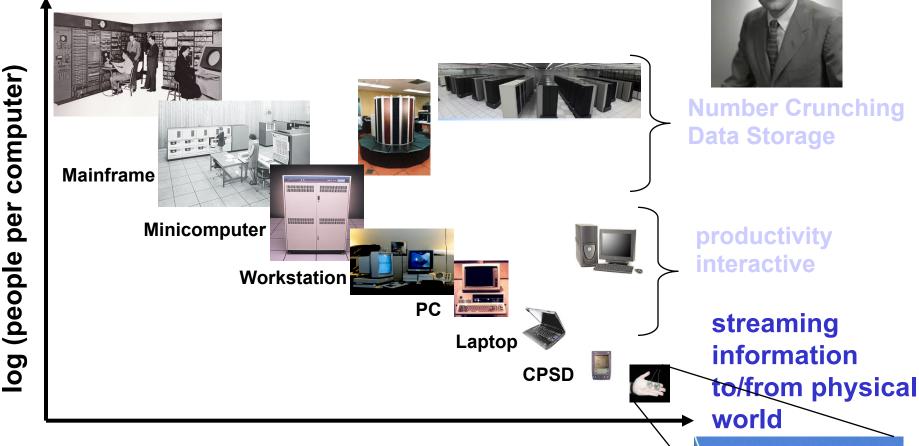

### Bell's Law of Computer Classes: A new computing class roughly every decade

Adapted from

D. Culler

#### vear

"Roughly every decade a new, lower priced computer class forms based on a new programming platform, network, and interface resulting in new usage and the establishment of a new industry."

#### Moore's Law (a statement about economics): IC transistor count doubles every 18-24 mo

Photo Credit: Intel

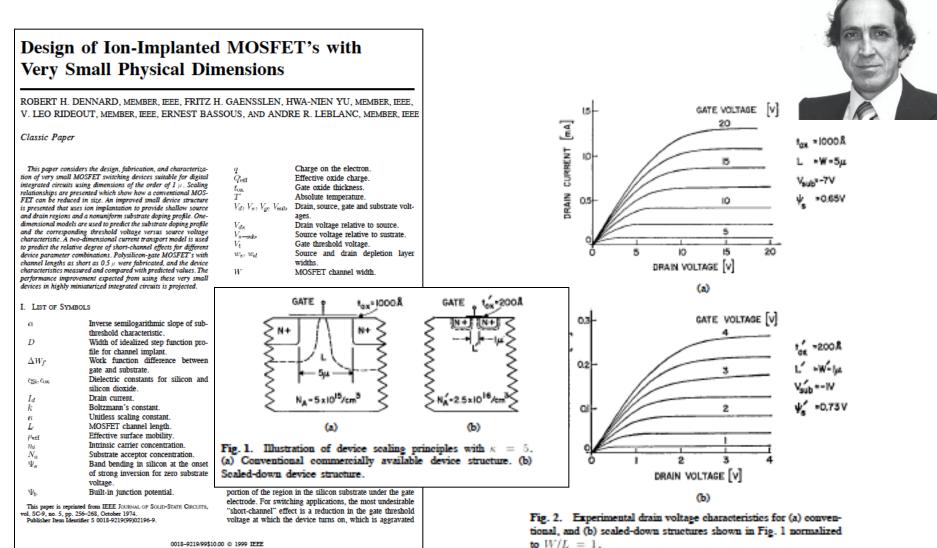

#### Dennard Scaling made transistors fast and low-power: So everything got better!

0018-9219/99\$10.00 @ 1999 IEEE

11

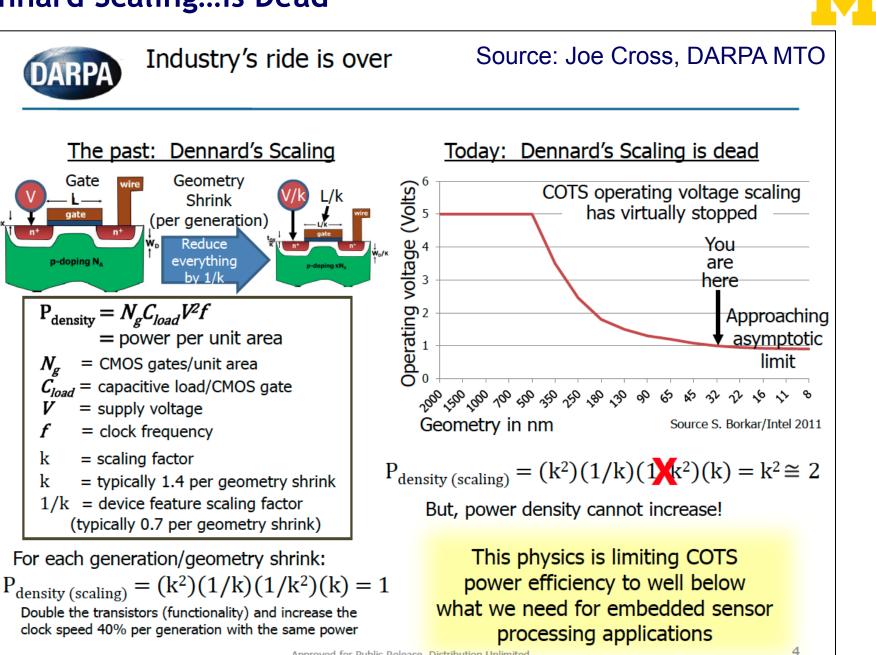

#### Dennard Scaling...is Dead

Approved for Public Release, Distribution Unlimited

# And the Party's Over

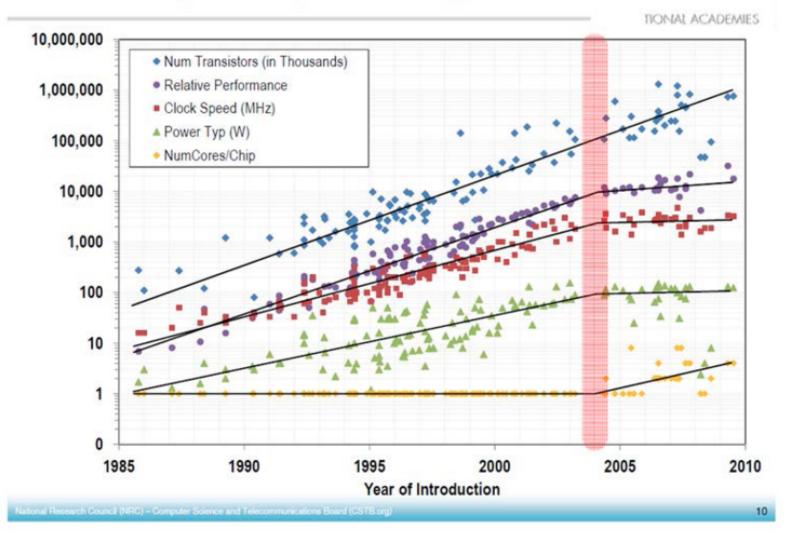

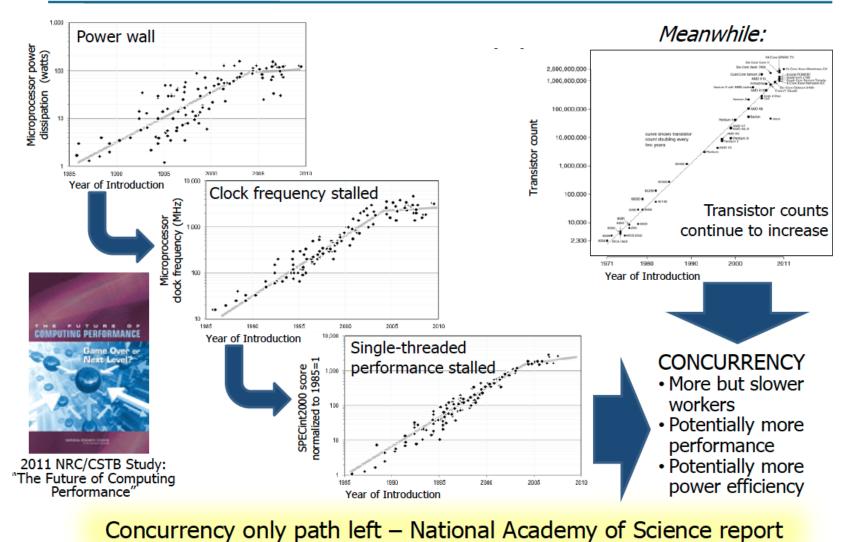

#### Decades of exponential performance growth stalled in 2004

Source: NRC, The Future of Computing Performance, Game Over or Next Level?

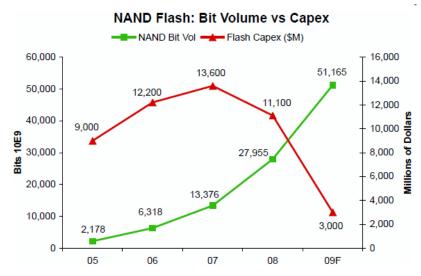

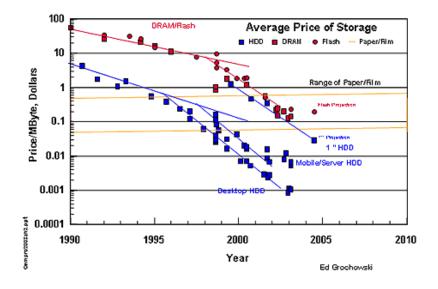

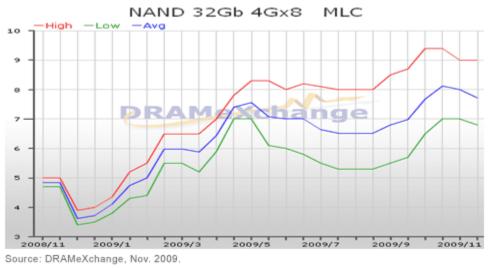

#### Flash memory scaling: Rise of density & volumes; Fall (and rise) of prices

Figure-1 32Gb MLC NAND Flash contract price trend

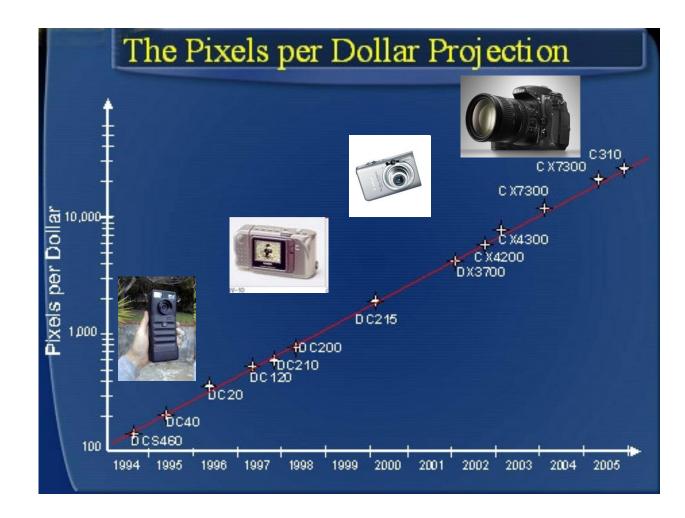

## Hendy's "Law": Pixels per dollar doubles annually

#### Credit: Barry Hendy/Wikipedia

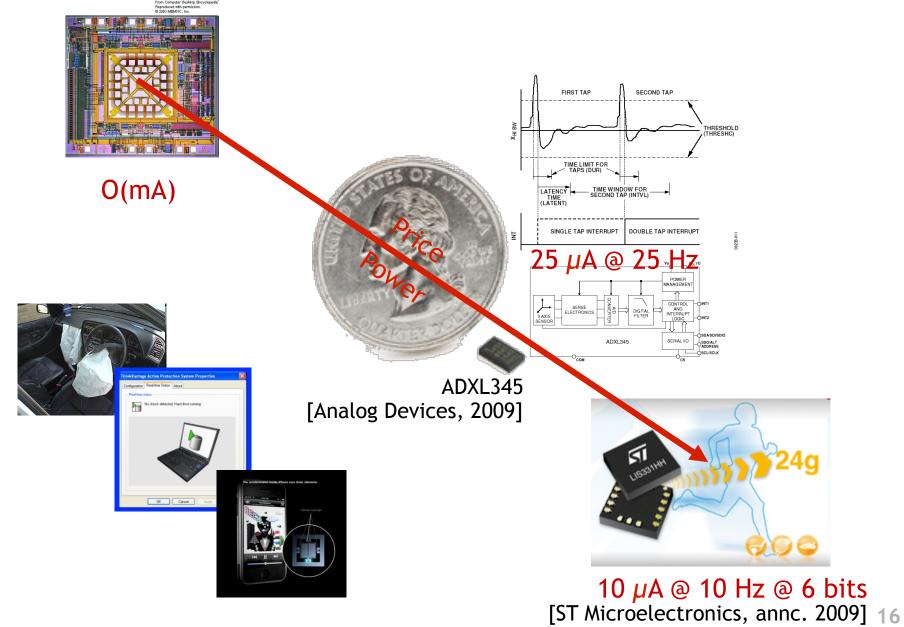

### **MEMS Accelerometers:** Rapidly falling price and power

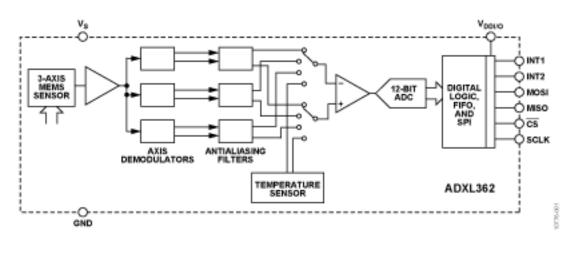

#### **MEMS Accelerometer in 2012**

1.8 μA @ 100 Hz @ 2V supply!

ADXL362 [Analog Devices, 2012]

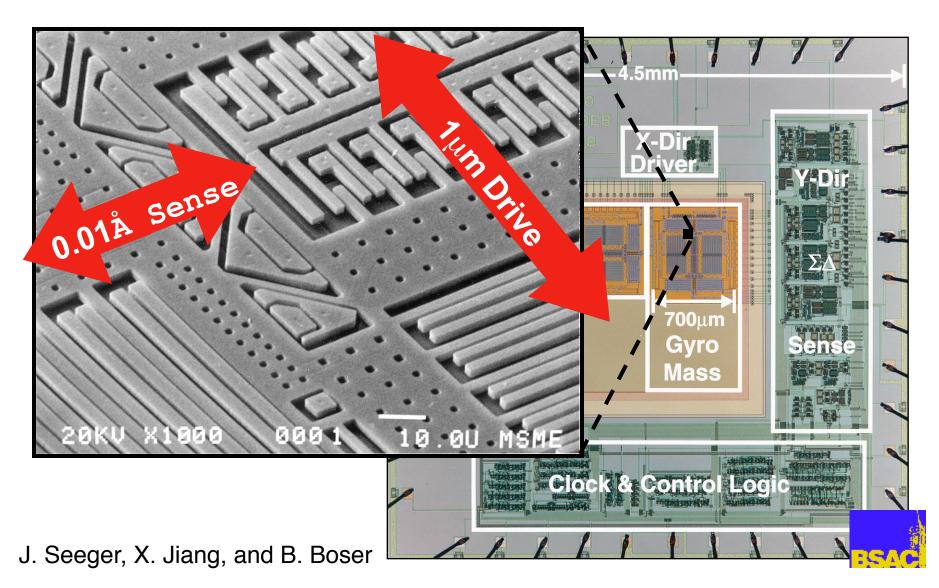

#### **MEMS Gyroscope Chip**

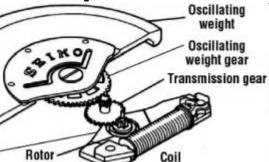

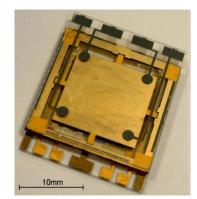

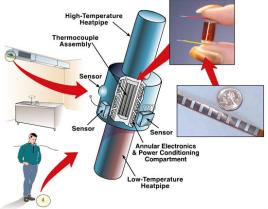

### Energy harvesting and storage: Small doesn't mean powerless...

RF [Intel] Clare Solar Cell

Thin-film batteries

Piezoelectric [Holst/IMEC]

Stator

BOOSTCAP

Electrostatic Energy Harvester [ICL]

Shock Energy Harvesting CEDRAT Technologies

Thermoelectric Ambient Energy Harvester [PNNL]

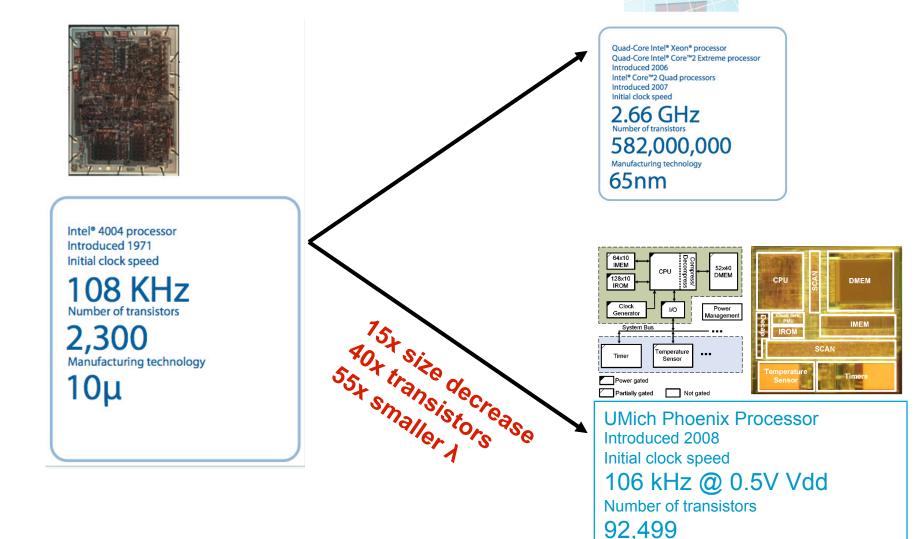

### Bell's Law, Take 2: Corollary to the Laws of Scale

Photo credits: Intel, U. Michigan

20

Manufacturing technology

0.18 µ

Outline

Technology Trends

**Design Questions**

Course Administrivia

Tools Overview/ISA Start

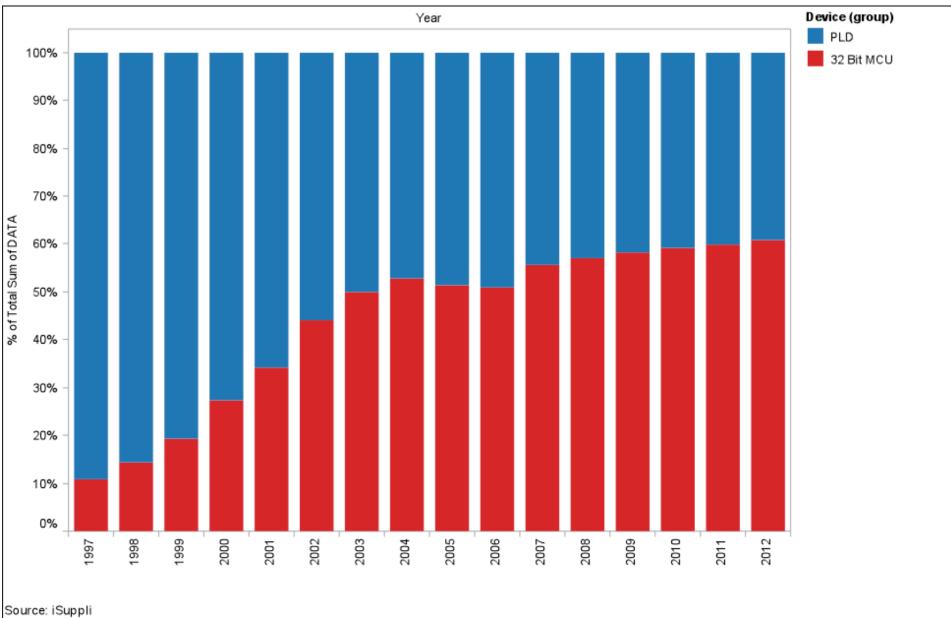

# Why study 32-bit MCUs and FPGAs?

#### MCU-32 and PLDs are tied in embedded market share

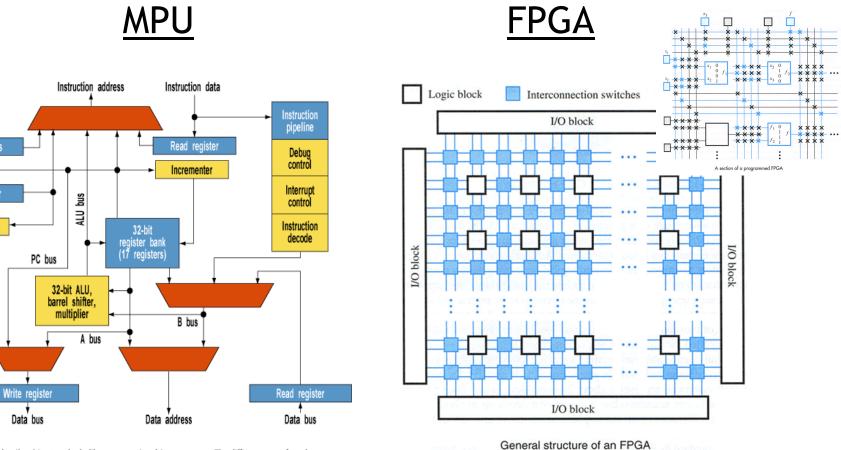

# What distinguishes a Microprocessor from an FPGA?

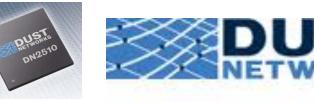

The Cortex M3's Thumbnail architecture looks like a conventional Arm processor. The differences are found in the Harvard architecture and the instruction decode that handles only Thumb and Thumb 2 instructions.

Interrupt address

Address register

Incrementer

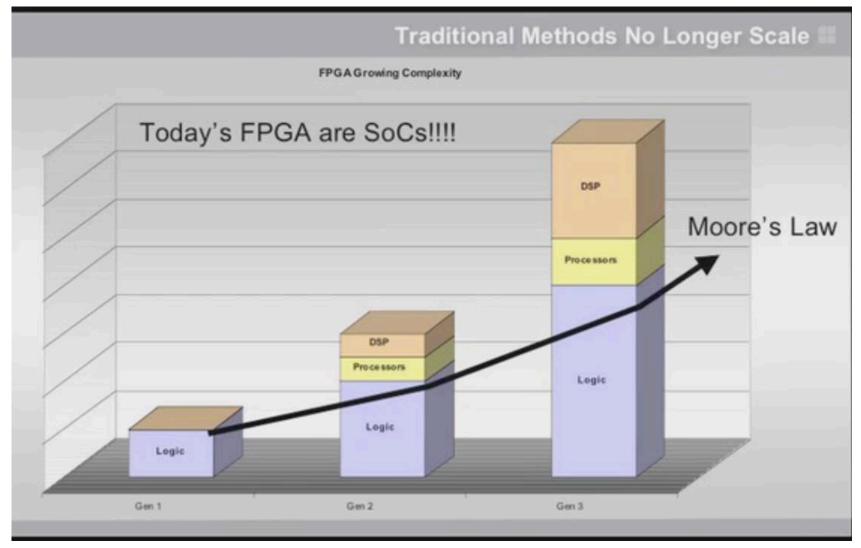

# Modern FPGAs: best of both worlds!

#### Is the party really over?

Technology landscape: move past power limitations, effectively utilize concurrency

Approved for Public Release, Distribution Unlimited

3

# Why study the ARM architecture (and the Cortex-M3 in particular)?

#### Lots of manufacturers ship ARM products

### ARM is the big player

- ARM has a huge market share

- As of 2011 ARM has chips in about 90% of the world's mobile handsets

- As of 2010 ARM has chips in 95% of the smartphone market, 10% of the notebook market

- Expected to hit 40% of the notebook market in 2015.

- Heavy use in general embedded systems.

- Cheap to use

- ARM appears to get an average of 8¢ per device (averaged over cheap and expensive chips).

- Flexible

- Spin your own designs.

# What differentiates these products from one another?

#### The difference is...

Outline

Technology Trends

**Design Questions**

**Course Overview**

Tools Overview/ISA Start

## F' 14 Instructional Staff (see homepage for contact info, office hours)

PrabalMattChrisChrisRyanDiliDuttaSmithFularaHeyerWoosterHuInstructorLabInstructorIAIAGrader

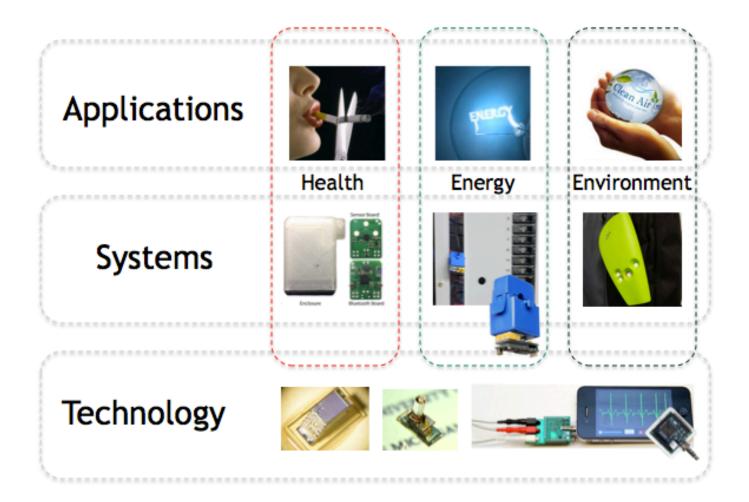

#### My research interests

#### **Course goals**

- Learn to implement embedded systems including hardware/software interfacing.

- Learn to design embedded systems and how to think about embedded software and hardware.

- *Design and build* non-trivial projects involving both hardware and software.

## **Prerequisites**

- EECS 270: Introduction to Logic Design

- Combinational and sequential logic design

- Logic minimization, propagation delays, timing

- EECS 280: Programming and Intro Data Structures

- C programming

- Algorithms (e.g. sort) and data structures (e.g. lists)

- EECS 370: Introduction to Computer Organization

- Basic computer architecture

- CPU control/datapath, memory, I/O

- Compiler, assembler

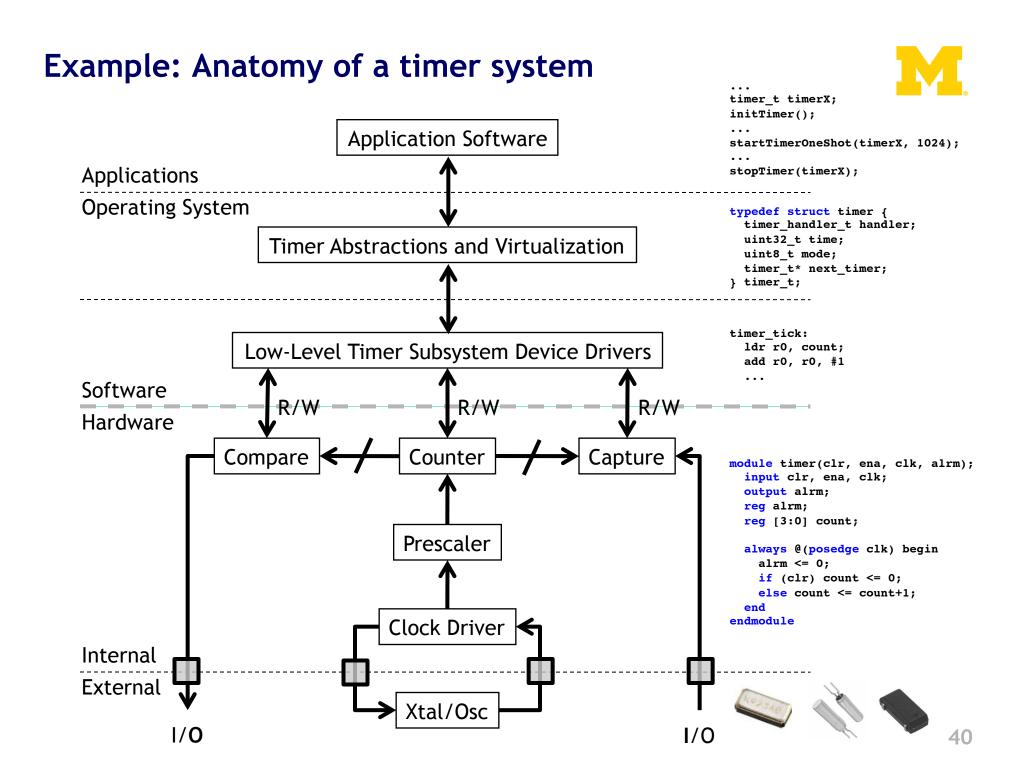

# Topics

- Memory-mapped I/O

- The idea of using memory addressed to talk to input and output devices.

- Switches, LEDs, hard drives, keyboards, motors

- Interrupts

- How to get the processor to become "event driven" and react to things as they happen.

- Working with analog signals

- The real world isn't digital!

- Common peripheral devices and interfaces

- Serial buses, timers, etc.

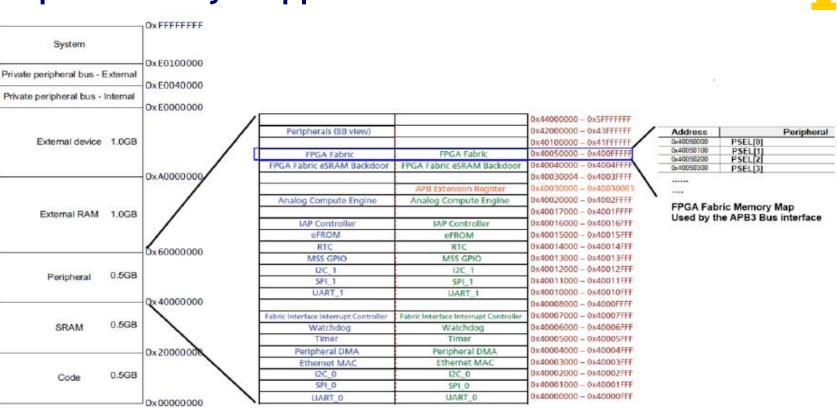

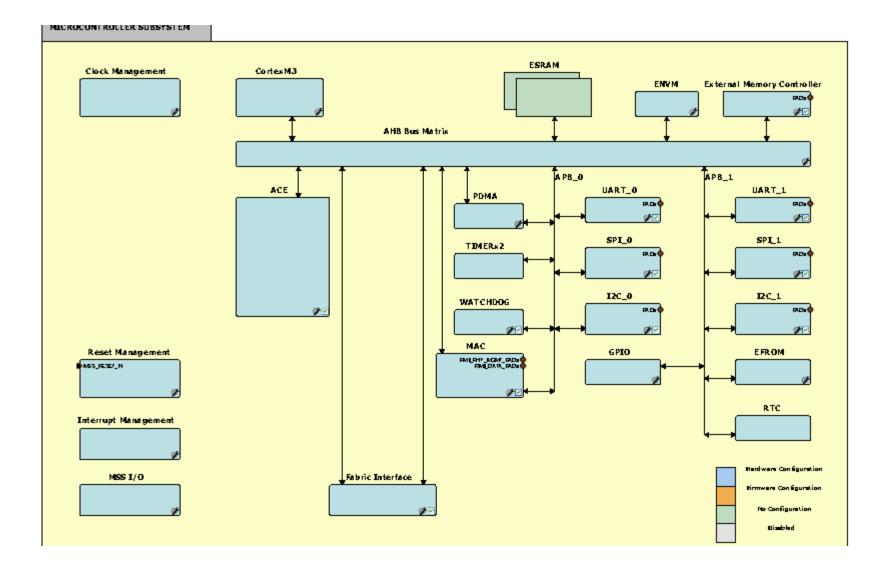

## Example: Memory-mapped I/O

• This is *important*.

Cortex-M3 Memory Map

- It means our software can tell the hardware what to do.

- In lab 3 you'll design hardware on an FPGA which will control a motor.

SmartFusion Peripheral Memory Map

- But more importantly, that hardware will be designed so the software can tell the hardware exactly what to do with the motor. All by simply writing to certain memory locations!

- In the same way, the software can read memory locations to access data from sensors etc...

## Grades

| Item              | Weight      |              |                     |     |        |

|-------------------|-------------|--------------|---------------------|-----|--------|

| =====             |             |              |                     |     |        |

| Labs (7)          | <b>25</b> % |              |                     |     |        |

| Project           | <b>25</b> % |              |                     |     |        |

| Exams             | 35%         | <b>(15</b> % | <pre>midterm;</pre> | 20% | final) |

| HW/Guest talks    | <b>10</b> % |              |                     |     |        |

| Oral presentation | 5%          |              |                     |     |        |

- Project & Exams tend to be the differentiators

- Class median is generally a B+

## Time

- Assume you are going to spend a lot of time in this class.

- 2-3 hours/week in lecture (we cancel a few classes during project time)

- 8-12 hours/week working in lab

- Expect more during project time; some labs are a bit shorter.

- ~20 hours (total) working on homework

- ~20 hours (total) studying for exams.

- ~8 hour (total) on your oral presentation

- Averages out to about 15-20 hours/week preproject and about 20 during the project...

- This is more than we'd like, but we've chosen to go with state-of-the-art tools, and those generally have a steep learning curve.

## Labs

- Start TODAY!

- 7 labs, 8 weeks, groups of 2

- 1. FPGA + Hardware Tools

- 2. MCU + Software Tools

- 3. Memory + Memory-Mapped I/O

- 4. Interrupts

- 5. Timers and Counters

- 6. Serial Bus Interfacing

- 7. Data Converters (e.g. ADCs/DACs)

- Labs are very time consuming.

- As noted, students estimated 8-12 hours per lab with one lab (which varied by group) taking longer.

## **Open-Ended Project**

- Goal: <u>learn how to build embedded systems</u>

- By <u>building</u> an embedded system

- Work in teams of 2 to 4

- You design your own project

- The major focus of the last third of the class.

- Labs will be done and we will cancel some lectures and generally try to keep you focused

- Important to start early.

- After all the effort in the labs, it's tempting to slack for a bit. The best projects are those that get going right away (or even earlier)

- Some project lead to undergraduate research

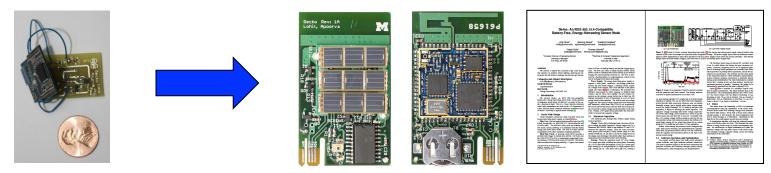

# Sample projects from F' 10 and their results

Energy-harvesting sensors →

Sensys demo, IPSN paper, TI project, Master's thesis

Wireless AC Power Meter →

SURE, IPSN demo, NSF GRFP, SenSys paper, Grad School

## Letters of recommendation for graduate school

- Grad school apps will require supporting letters

- Faculty write letters and read "coded" letters

- Strong letters give evidence of research ability

- Strong letters can really help your case

- Weak letters are vague and give class standing

- Weak letters are useless (or even worse)

- Want a strong letter?

- Do well in this class

- Pull off an impressive project

- Continue class project as independent research in W'15

## Homework

- Start TODAY!

- 4-5 assignments

- A few "mini" assignments

- Mainly to get you up to speed on lab topics

- A few "standard" assignments

- Hit material we can't do in lab.

- Also a small part is for showing up to guest lectures

- And a tiny bit for doing completing evaluations

## **Midterm and Final Exams**

- Midterm (Thu, Oct 16, 2014 from 10:30am-12:00pm)

- Emphasize problem solving fundamentals

- Final (Tue, Dec 16, 2014 from 1:30-3:30pm)

- Cumulative topics w/ experience of projects

- Some small amount of material from presentations

# Looking for me?

- Nominal Office Hours

- Tuesdays: 1:30-3:00pm in 4773 BBB

- Sometimes in lab sections

- Traveling next week so

- Guest lectures on Tue 9/9 and Thu 9/11

- No office hours next week

Outline

Technology Trends

**Design Questions**

**Course Overview**

Tools Overview/ISA Start

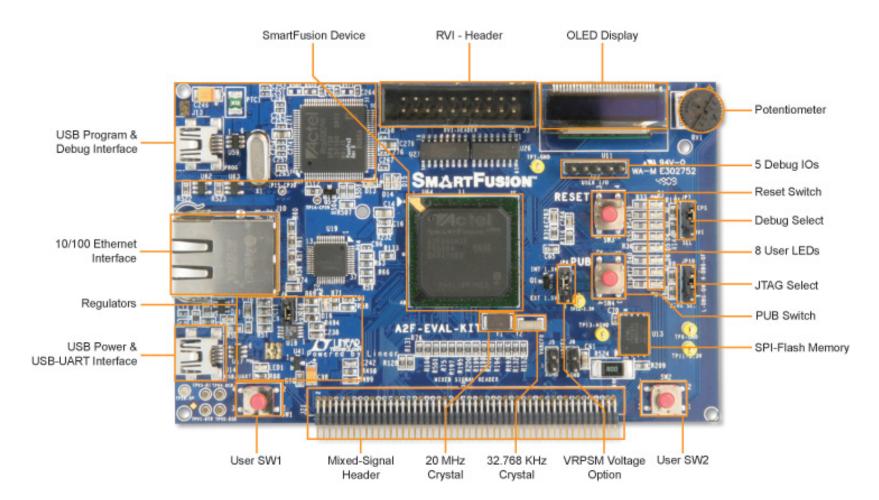

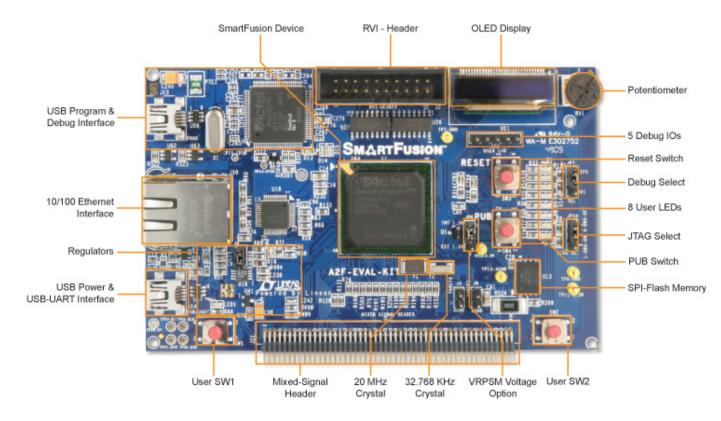

# We are using Actel's SmartFusion Evaluation Kit

#### A2F200M3F-FGG484ES

- 200,000 System FPGA gates, 256 KB flash memory, 64 KB SRAM, and additional distributed SRAM in the FPGA fabric and external memory controller

- Peripherals include Ethernet, DMAs, I<sup>2</sup>Cs, UARTs, timers, ADCs, DACs and additional analog resources

- USB connection for programming and debug from Actel's design tools

- USB to UART connection to UART\_0 for HyperTerminal examples

- 10/100 Ethernet interface with on-chip MAC and external PHY

- Mixed-signal header for daughter card support

### **FPGA** work

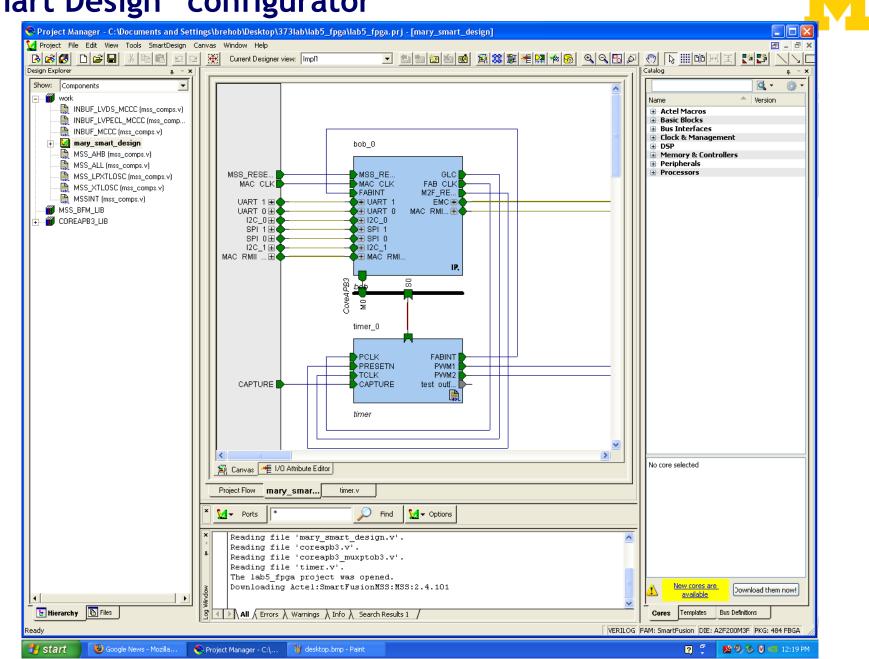

# "Smart Design" configurator

# Eclipse-based "Actel SoftConsole IDE"

\_ @ X

SC C/C++ - lab5/main.c - Actel SoftConsole IDE v3.2 File Edit Source Refactor Navigate Search Project Run Window Help

#### 💼 • 🗒 💩 📾 🗄 💓 🖾 4 📷 • 🚳 • 💣 • 🧭 • 🐐 • 🚳 • 🐐 • 🚱 • 🐐 • 🚱 • 🖉 • 🖓 • 🖉 • 🖓 • 🖉 • 🖓 • 🖉 😭 🏇 Debug 🛛 📅 C/C++ Project Explorer 🖾 📄 🔄 🍸 🗖 🗖 🔂 main.c 🛛 🗖 🗖 📴 Outlin 🕱 💿 Make 🗖 🗖 💼 assembly\_test 56 ^ = 🎼 💘 💊 💘 🎽 -- 💼 forCheatSheet 57 if(status & OxO1) 📲 stdio.h -- 💼 Lab2 58 { drivers/mss\_uart/mss\_uart - 📋 lab3\_test 59 printf("Overflow latency %ld\n\r", 0-time); drivers/mss\_watchdog/mss -- 💼 lab4 60 wytimer.h 📹 lab4again 61 if(status & OxO2) Fabric IROHandler(void) : 🛓 💕 lab5 62 { 👩 main() : int printf("Compare latency %ld\n\r", (1<<29) - time);</pre> 63 64 } 65 if(status & Ox4) 66 { 67 printf("Capture SYNC %ld\n\r", sync cap); 68 } 69 if(status & Ox8) 70 { 71 printf("Capture ASYNC %ld\n\r", async\_cap); 72 3 73 NVIC ClearPendingIRQ( Fabric IRQn ); 74} 75 76int main() 77 ( 78 /\* Watchdog Disabling function \*/ 79 MSS\_WD\_disable(); 80 81 /\* Setup MYTIMER \*/ 82 MYTIMER init(); 83 MYTIMER load((1<<31)); // low time MYTIMER compare((1<<27)); // high time 84 85 86 // MYTIMER enable overflow(); //MYTIMER enable compare(); 87 88 MYTIMER enable capture(); MYTIMER enable pwm(); 89 90 // MYTIMER\_enable\_interrupts(); 91 92 NVIC EnableIRQ(Fabric IRQn); 93 94 MYTIMER enable(); maintf ("HElloopoo 05 Anterth < > < 📑 🗉 - 📬 - 🗆 🗖 🛃 Problems 🙋 Tasks 📃 Console 🛛 🔪 🔲 Properties 🕸 Debug No consoles to display at this time. ₽≎ Writable Smart Insert 79 : 1 🕲 Google News - Mozilla... ? 1 🅦 🧐 🦻 🕅 🥶 12:21 PM 🛃 start 🛛 😪 Project Manager - C:\... 🦉 desktop2.bmp - Paint SC C/C++ - lab5/main.c ...

## Debugger is GDB-based. Includes command line. Works really quite well.

| ▶ Debug 🛛                      |                                       |                               |                   |                      |                      |               |                 |                     |

|--------------------------------|---------------------------------------|-------------------------------|-------------------|----------------------|----------------------|---------------|-----------------|---------------------|

| 🌣 Debug 🛛                      | - T 🖉 T 🍲 T e 🗁 🛷 T e 🌽 e S           | <b>}</b> - <b>¦</b> - ⇔ - ⇒ - |                   |                      |                      |               | 🖺 🏇 Debug       | ) 🔂 C/0             |

|                                | M 🖷 🗈 🛸 🗱                             | 1 3. 3. 12 🛒 ið 😿             | 🧑 🍸 🗖 🗖 😡= Varial | oles 💁 Breakpoints 🔀 | 🐰 👬 Registers 🛋 Modu | les 🔉         | < 🔆 🤣 🖓 🖓 🔪 🖪 🔁 | × ۲                 |

|                                |                                       |                               |                   |                      |                      |               |                 |                     |

|                                |                                       |                               |                   |                      |                      |               |                 |                     |

|                                |                                       |                               |                   |                      |                      |               |                 |                     |

|                                |                                       |                               |                   |                      |                      |               |                 |                     |

|                                |                                       |                               |                   |                      |                      |               |                 |                     |

|                                |                                       |                               |                   |                      |                      |               |                 |                     |

|                                |                                       |                               |                   |                      |                      |               |                 |                     |

| main.c 🛛                       |                                       |                               |                   |                      | -                    | 🗆 📴 Outline ( | 🗟 Disassembly 🛛 | $\overline{\nabla}$ |

| 56                             |                                       |                               |                   |                      | ^                    |               | in operation of |                     |

| 57 if(status                   | 2 Ox01)                               |                               |                   |                      |                      |               |                 |                     |

| 58 {                           |                                       |                               |                   |                      |                      |               |                 |                     |

|                                | ("Overflow latency %ld\n\r",          | O-time);                      |                   |                      |                      |               |                 |                     |

| 60 }                           |                                       |                               |                   |                      |                      |               |                 |                     |

| 61 <b>if</b> (status -<br>62 { | ; 0x02)                               |                               |                   |                      |                      |               |                 |                     |

|                                | f("Compare latency %ld\n\r",          | (1<<29) - time):              |                   |                      |                      |               |                 |                     |

| 64 }                           | in compare facency that his ,         | (1((1))) 01110))              |                   |                      |                      |               |                 |                     |

| 65 if (status                  | ; 0x4)                                |                               |                   |                      |                      |               |                 |                     |

| 66 {                           |                                       |                               |                   |                      | _                    |               |                 |                     |

|                                | ("Capture SYNC %ld\n\r", sync         | _cap);                        |                   |                      |                      |               |                 |                     |

| 68 }<br>69 <b>if</b> (status   | ( 0x8)                                |                               |                   |                      |                      |               |                 |                     |

| 70 {                           |                                       |                               |                   |                      |                      |               |                 |                     |

|                                | ("Capture ASYNC %ld\n\r", asy         | nc_cap);                      |                   |                      |                      |               |                 |                     |

| 72 }                           |                                       |                               |                   |                      |                      |               |                 |                     |

| 73 NVIC_Clear<br>74)           | <pre>PendingIRQ( Fabric_IRQn );</pre> |                               |                   |                      |                      |               |                 |                     |

| 75                             |                                       |                               |                   |                      |                      |               |                 |                     |

| 76 <mark>int main()</mark>     |                                       |                               |                   |                      |                      |               |                 |                     |

| 77 (                           |                                       |                               |                   |                      |                      |               |                 |                     |

|                                | Disabling function */                 |                               |                   |                      |                      |               |                 |                     |

| 79 MSS_WD_dis:<br>80           | uble();                               |                               |                   |                      |                      |               |                 |                     |

| 81 /* Setun M                  | TIMER */                              |                               |                   |                      | *                    |               |                 |                     |

|                                |                                       |                               |                   |                      | >                    | <             |                 | >                   |

| 5                              |                                       |                               |                   |                      |                      |               | 🛃 📃 * [         | <del>)</del> -      |

| Console 🛛 🖉 Tasks              | 🛣 Problems 🚺 Executables 🚺 Memory     |                               |                   |                      |                      |               |                 |                     |

SC Debug - lab5/main.c -...

🛃 start

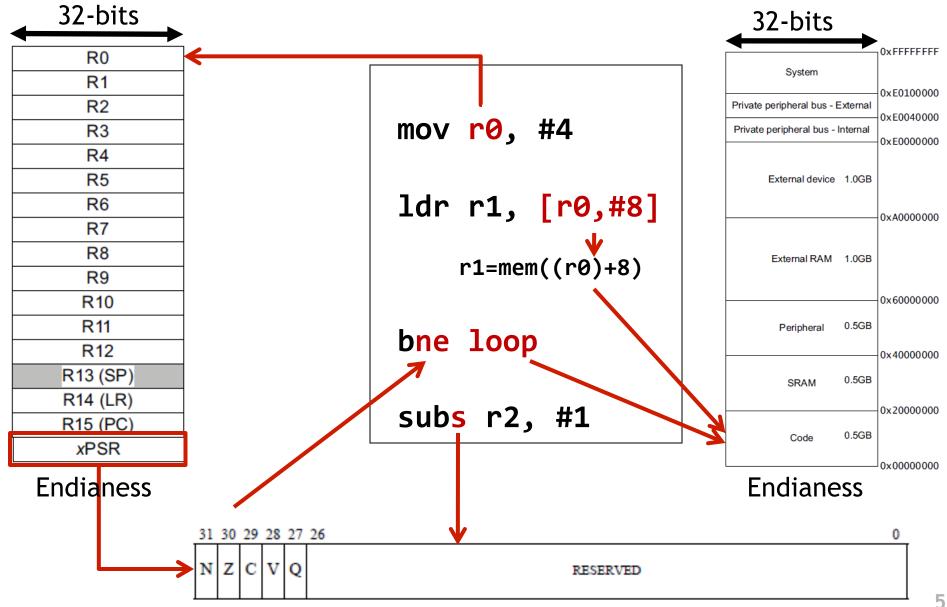

# **ARM ISA**

# <u>Major</u> elements of an Instruction Set Architecture

(registers, memory, word size, endianess, conditions, instructions, addressing modes)

# Assembly example

| data: |                                    |

|-------|------------------------------------|

| .by   | te 0x12, 20, 0x20, -1              |

| func: |                                    |

|       | mov r0, #0                         |

|       | mov r4, #0                         |

|       | <pre>movw r1, #:lower16:data</pre> |

|       | <pre>movt r1, #:upper16:data</pre> |

| top:  | ldrb r2, [r1],#1                   |

|       | add r4, r4, r2                     |

|       | add r0, r0, #1                     |

|       | cmp r0, #4                         |

|       | bne top                            |

# Questions?

# Comments?

Discussion?