# EECS 373 Design of Microprocessor-Based Systems

### Branden Ghena University of Michigan

Lecture 5: Memory and Peripheral Buses January 22, 2015

#### Announcements

- I'm not Prabal

- You probably noticed

- He's in Washington DC doing this and this

- He regrets that he cannot be here today and will not have OH

- We're working on additional GSI/IA office hours (OH)

Pat Pannuto 10-11am MW in EECS Learning Center

- (Glass rooms between BBB and Dow)

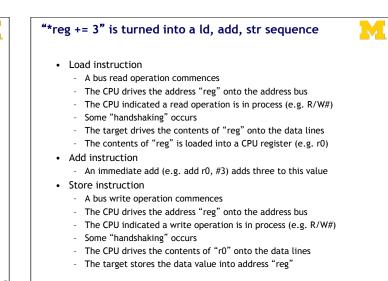

What happens when this "instruction" executes?

#include <stdio.h>

#include <inttypes.h>

#define REG\_FO0 0x40000140

main () {

uint32\_t \*reg = (uint32\_t \*)(REG\_FO0);

\*reg += 3;

printf("0x%x\n", \*reg); // Prints out new value

}

#### Some useful C keywords

- const

- Makes variable value or pointer parameter unmodifiable

- const foo = 32;

- register

- Tells compiler to locate variables in a CPU register if possible

- register int x;

- static

- Preserve variable value after its scope ends

- Does not go on the stack

- static int x;

- volatile

- Opposite of const

- Can be changed in the background

- volatile int I;

# Outline

- Announcements

- Accessing memory from Assembly/C

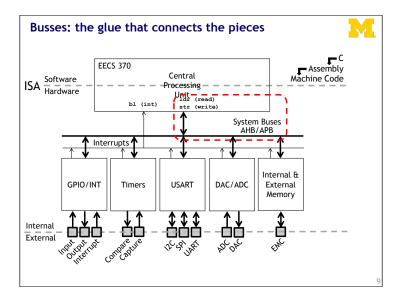

- Busses: The glue that connects the pieces

- ARM Advanced Peripheral Bus (APB)

- ARM Advanced High-performance Bus Light (AHB-Lite)

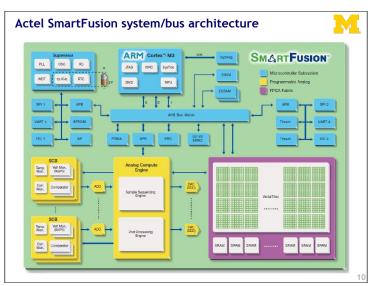

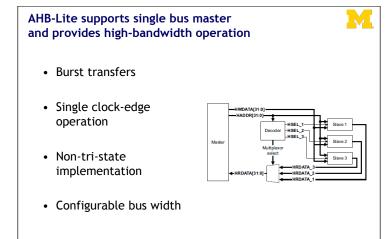

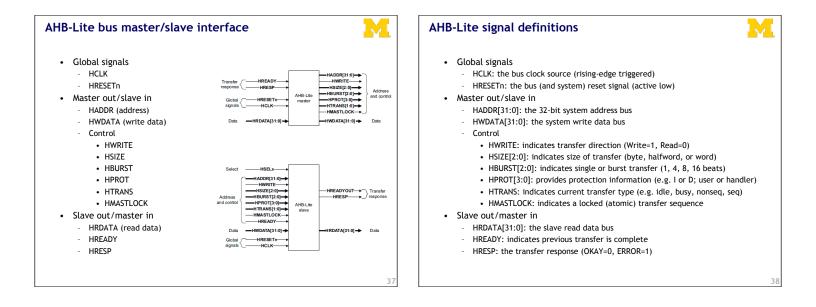

Advanced Microcontroller Bus Architecture (AMBA)

DMA bus master

High-bandwidth on-chip RAM

- Advanced High-performance Bus (AHB)

High-performance ARM processor

- Advanced Peripheral Bus (APB)

- Many designs considerations

- Master vs Slave

- Internal vs External

- Bridged vs Flat

- Memory vs Peripheral

- Synchronous vs Asynchronous

- High-speed vs low-speed

- Serial vs Parallel

- Single master vs multi master

- Single layer vs multi layer

- Multiplexed A/D vs demultiplexed A/D

- Discussion: what are some of the tradeoffs?

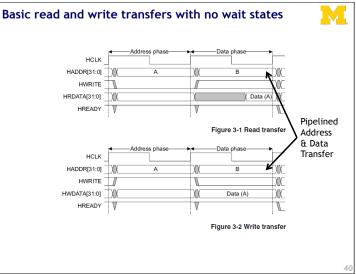

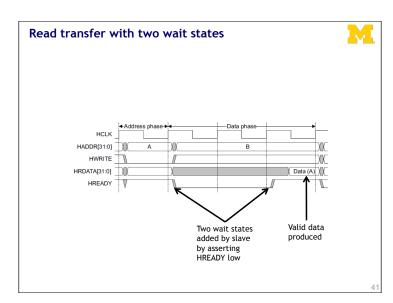

• High performance

High-bandwidth Memory Interfac

- Pipelined operation

- Burst transfers

- Multiple bus masters

- Split transactions

- APB

- Low power

AHR to APR Brid

- Latched address/control

- Simple interface

- Suitable of many peripherals

### Outline

- Announcements

- Accessing memory from Assembly/C

- Busses: The glue that connects the pieces

- ARM Advanced Peripheral Bus (APB)

- ARM Advanced High-performance Bus Light (AHB-Lite)

#### APB: a simple bus that is easy to work with

- Low-cost

- Low-power

- Low-complexity

- Low-bandwidth

- Non-pipelined

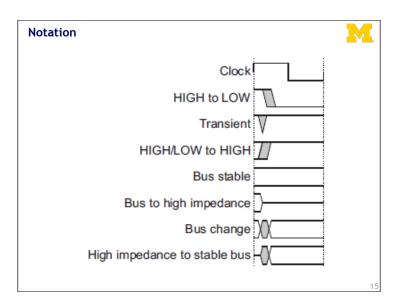

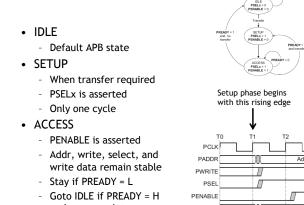

APB bus state machine

• Ideal for peripherals

#### and no more data Goto SETUP is PREADY = H

and more data pending

İγγ PWDATA PREADY Setup Access Phase Phase

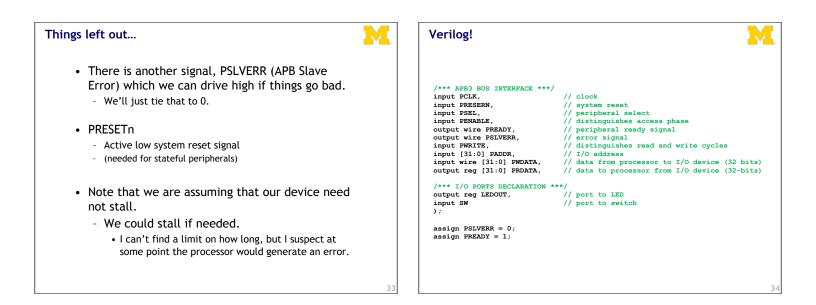

#### **APB** signal definitions

- PCLK: the bus clock source (rising-edge triggered)

- PRESETn: the bus (and typically system) reset signal (active low)

- PADDR: the APB address bus (can be up to 32-bits wide)

- PSELx: the select line for each slave device

- PENABLE: indicates the 2<sup>nd</sup> and subsequent cycles of an APB xfer

- PWRITE: indicates transfer direction (Write=H, Read=L)

- PWDATA: the write data bus (can be up to 32-bits wide)

- PREADY: used to extend a transfer

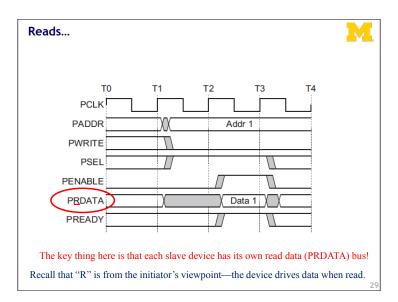

- PRDATA: the read data bus (can be up to 32-bits wide)

- PSLVERR: indicates a transfer error (OKAY=L, ERROR=H)

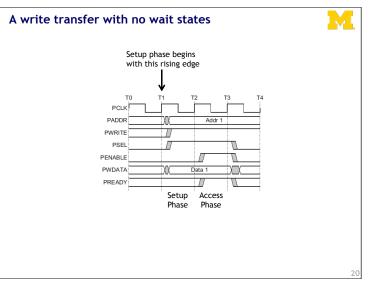

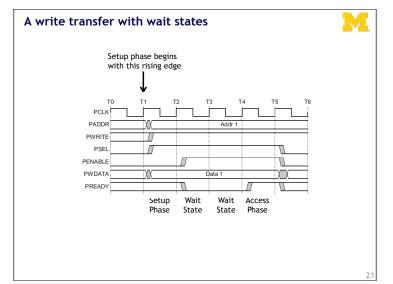

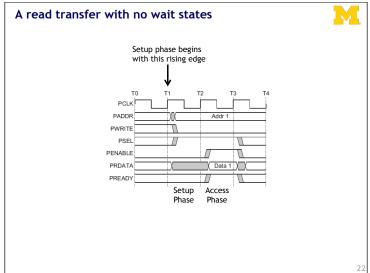

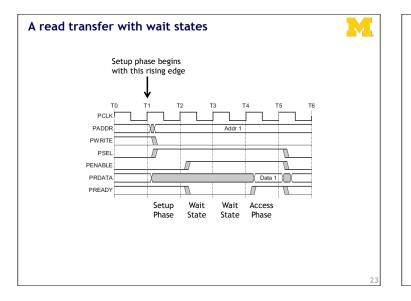

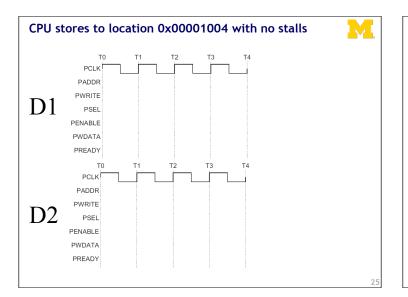

## APB bus signals in action

- PCLK

- Clock

- PADDR

- Address on bus

- PWRITE

- 1=Write, 0=Read

- PWDATA

- Data written to the I/O device. Supplied by the bus

- master/processor.

#### **APB** bus signals

- PSEL

- Asserted if the current bus transaction is targeted to <u>this</u> device

- PENABLE

- High during entire transaction other than the first cycle.

- PREADY

- Driven by target.

Similar to our #ACK.

Indicates if the target is <u>ready</u> to do transaction.

Each target has it's own PREADY

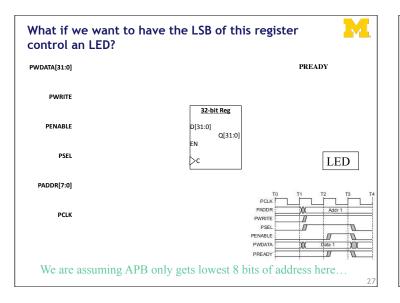

| <b>//ri</b> | Vrites                           |    |  |  |  |

|-------------|----------------------------------|----|--|--|--|

|             | Let's do some hardware examples! |    |  |  |  |

|             |                                  |    |  |  |  |

|             |                                  |    |  |  |  |

|             |                                  |    |  |  |  |

|             |                                  |    |  |  |  |

|             |                                  |    |  |  |  |

|             |                                  | 26 |  |  |  |

|             |                                  |    |  |  |  |

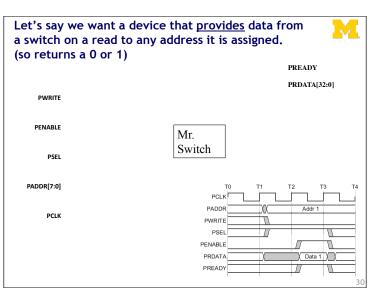

|             | ovides data from swit<br>100 is read from. B if |        |        | M       |

|-------------|-------------------------------------------------|--------|--------|---------|

| is read fro | om                                              |        |        |         |

|             |                                                 |        | PREAD  | Y       |

|             |                                                 |        | PRDATA | A[31:0] |

| PWRITE      |                                                 |        |        |         |

|             |                                                 |        |        |         |

| PENABLE     |                                                 |        | 1      |         |

|             |                                                 | Mr.    |        |         |

| PSEL        |                                                 | Switch |        |         |

|             |                                                 | Mrs.   |        |         |

| PADDR[7:0]  |                                                 | Switch |        |         |

|             |                                                 |        | 1      |         |

| PCLK        |                                                 |        |        |         |

|             |                                                 |        |        |         |

|             |                                                 |        |        |         |

|             |                                                 |        |        |         |

|             |                                                 |        |        |         |

|             |                                                 |        |        | 31      |

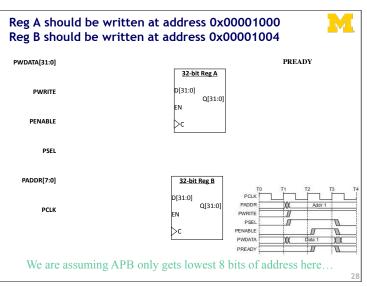

| reads read from r  | egister, all writes write         | M                                                        |

|--------------------|-----------------------------------|----------------------------------------------------------|

| PWDATA[31:0]       |                                   | PREADY                                                   |

| PWRITE             |                                   | PRDATA[31:0]                                             |

| PENABLE            | 32-bit Reg<br>D[31:0]             |                                                          |

| PSEL               | Q[31:0]<br>EN<br>>C               |                                                          |

| PADDR[7:0]         | r                                 |                                                          |

| PCLK               |                                   | 1 T2 T3                                                  |

| PREADY             | PSEL                              | 11<br>11<br>12<br>12<br>12<br>12<br>12<br>12<br>12<br>12 |

| We are assuming Al | PB only gets lowest 8 bits of add | lress here                                               |

Α

# Outline

- Announcements

- Accessing memory from Assembly/C

- Busses: The glue that connects the pieces

- ARM Advanced Peripheral Bus (APB)

- ARM Advanced High-performance Bus Light (AHB-Lite)

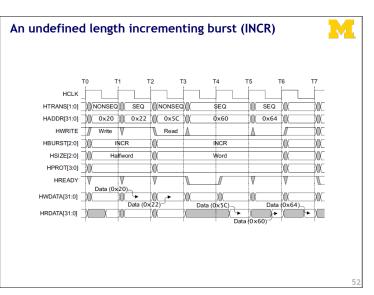

### Transfers can be of four types (HTRANS[1:0])

#### • IDLE (b00)

- No data transfer is required

- Slave must OKAY w/o waiting

- Slave must ignore IDLE

- BUSY (b01)

- Insert idle cycles in a burst

Burst will continue afterward

- Buist will continue arterward

- Address/control reflects next transfer in burst

- Slave must OKAY w/o waiting

- Slave must ignore BUSY

#### NONSEQ (b10)

- Indicates single transfer or first transfer of a burst

- Address/control unrelated to prior transfers

- SEQ (b11)

- SEQ (DIT)

- Remaining transfers in a burst

Addr = prior addr + transfer size

M A four beat burst with master busy and slave wait Master busy indicated by HTRANS[1:0] Т2 HCLK ((NONSEQ)) BUSY () SEQ () SEQ () SEO XX HTRANS[1:0] HADDR[31:0] () 0x20 () 0x24 () 0x24 () 0x28 () XX dx2C XX 1 Δ 1 HBURST[2:0] INCR İXX XX ŤΧΙΧ HREADY V V W N Data (0x20) HRDATA[31:0] Data (0x28) x28) ) Data (0x2C) X Data (0x24) )(+ X One wait state added by slave by asserting HREADY low

| Controlling the size (width) of a                | trans    | fer      |          |                | M           |

|--------------------------------------------------|----------|----------|----------|----------------|-------------|

| • HSIZE[2:0] encodes the size                    |          |          |          |                |             |

| • The cannot exceed the data bus                 | HSIZE[2] | HSIZE[1] | HSIZE[0] | Size<br>(bits) | Description |

| width (e.g. 32-bits)                             | 0        | 0        | 0        | 8              | Byte        |

|                                                  | 0        | 0        | 1        | 16             | Halfword    |

| <ul> <li>HSIZE + HBURST is determines</li> </ul> | 0        | 1        | 0        | 32             | Word        |

| wrapping boundary for wrapping                   | 0        | 1        | 1        | 64             | Doubleword  |

| bursts                                           | 1        | 0        | 0        | 128            | 4-word line |

|                                                  | 1        | 0        | 1        | 256            | 8-word line |

| HSIZE must remain constant                       | 1        | 1        | 0        | 512            | -           |

| throughout a burst transfer                      | 1        | 1        | 1        | 1024           | -           |

|                                                  |          |          |          |                |             |

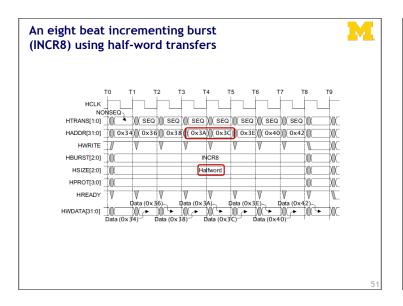

| A four beat inc | rement  | ting b  | urst (l | NCR4)     |         |        |     | Ξ¥. |

|-----------------|---------|---------|---------|-----------|---------|--------|-----|-----|

|                 |         |         |         |           |         |        |     |     |

|                 |         |         |         |           |         |        |     |     |

|                 |         |         |         |           |         |        |     |     |

|                 | T0 1    | 1       | T2 1    | гз 1<br>∟ | 4       | 15 1   | F6  |     |

| HCLK            |         |         |         |           |         |        |     |     |

| HTRANS[1:0]     | NONSEC  | XX      | \$EQ    | ) SEQ     | ) SEQ   | XX     | XX  |     |

| HADDR[31:0]     | () 0x38 | XX      | 0×3C    | ))( 0×40  | () 0×44 | XX     | XXC |     |

| HWRITE          | 1       | Δ       |         | Δ         | Δ       | /      | XX  |     |

| HBURST[2:0]     | XX      |         | INCR4   |           |         | XX     | XX  |     |

| HSIZE[2:0]      | XX      |         | Word    |           |         | XXX    | XXX |     |

| HPROT[3:0]      | X       |         |         |           |         | XX     | XXC |     |

| HREADY          |         | h       | π       | V         | W       |        | 1   |     |

| TIREADT         | v       | Data (0 | )x38)_  | V<br>Data | (0x40)  | v      | ₩_  |     |

| HRDATA[31:0]    | X X     | X       | L)( 🗣   | X )+      | X X+    | X )+   | X   |     |

|                 | 1       |         | Data    | (0x3C)    | Data    | (0x44) |     |     |

|                 |         |         |         |           |         |        |     |     |

|                 |         |         |         |           |         |        |     |     |

|                 |         |         |         |           |         |        |     |     |

|                 |         |         |         |           |         |        |     |     |

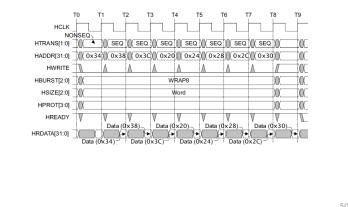

An eight beat wrapping burst (WRAP8)