# **EECS 373**

# Design of Microprocessor-Based Systems

# Prabal Dutta University of Michigan

Lecture 6: Interrupts January 27, 2015

Slides developed in part by Mark Brehob

#### **Announcements**

- Additional GSI/IA office hours (OH)

- Pat Pannuto 10-11am MW in EECS Learning Center

- (Glass rooms between BBB and Dow)

2

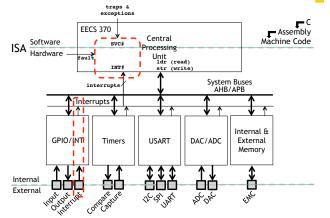

### Interrupts, traps, exceptions, and faults

#### Interrupts

#### Merriam-Webster:

- "to break the uniformity or continuity of"

- · Informs a program of some external events

- · Breaks execution flow

## Key questions:

- Where do interrupts come from?

- How do we save state for later continuation?

- · How can we ignore interrupts?

- · How can we prioritize interrupts?

- How can we share interrupts?

4

# Interrupts

#### Interrupt (a.k.a. exception or trap):

- An event that causes the CPU to stop executing current program

- Begin executing a special piece of code

- Called an interrupt handler or interrupt service routine (ISR)

- Typically, the ISR does some work

- Then resumes the interrupted program

#### Interrupts are really glorified procedure calls, except that they:

- can occur between any two instructions

- are "transparent" to the running program (usually)

- are not explicitly requested by the program (typically)

- call a procedure at an address determined by the type of interrupt, not the program

# Two basic types of interrupts (1/2)

- Those caused by an instruction

- Examples:

- TLB miss

- Illegal/unimplemented instruction

- div by 0

- SVC (supervisor call, e.g.: SVC #3)

- Names:

- Trap, exception

# Two basic types of interrupts (2/2)

- · Those caused by the external world

- External device

- Reset button

- Timer expires

- Power failure

- System error

- Names:

- interrupt, external interrupt

#### Why are interrupts useful? Example: I/O Data Transfer

Two key questions to determine how data is transferred to/from a non-trivial I/O device:

- 1. How does the CPU know when data is available?

- a. Polling

- b. Interrupts

- 2. How is data transferred into and out of the device?

- a. Programmed I/O

- b. Direct Memory Access (DMA)

#### How it works

- Something tells the processor core there is an interrupt

- Core transfers control to code that needs to be executed

- Said code "returns" to old program

- Much harder then it looks.

- Why?

#### Devil is in the details

- · How do you figure out where to branch to?

- How to you ensure that you can get back to where you started?

- Don't we have a pipeline? What about partially executed instructions?

- What if we get an interrupt while we are processing our interrupt?

- · What if we are in a "critical section?"

#### Where

- If you know what caused the interrupt then you want to jump to the code that handles that interrupt.

- If you number the possible interrupt cases, and an interrupt comes in, you can just branch to a location, using that number as an offset (this is a branch table)

- If you don't have the number, you need to poll all possible sources of the interrupt to see who caused it.

- Then you branch to the right code

# Get back to where you once belonged

- Need to store the return address somewhere.

- Stack might be a scary place.

- That would involve a load/store and might cause an interrupt (page fault)!

- So a dedicated register seems like a good choice

- But that might cause problems later...

- What happens if another interrupt happens?

#### Modern architectures

- A modern processor has *many* (often 50+) instructions in-flight at once.

- What do we do with them?

- · Drain the pipeline?

- What if one of them causes an exception?

- · Punt all that work

- Slows us down

- What if the instruction that caused the exception was executed before some other instruction?

- What if that other instruction caused an interrupt?

#### **Nested interrupts**

- If we get one interrupt while handling another what to do?

- Just handle it

- But what about that dedicated register?

- What if I'm doing something that can't be stopped?

- Ignore it

- But what if it is important?

- Prioritize

- Take those interrupts you care about. Ignore the rest

- Still have dedicated register problems.

#### Critical section

- We probably need to ignore some interrupts but take others.

- Probably should be sure our code can't cause an exception.

- Use same prioritization as before.

- What about instructions that shouldn't be interrupted?

- Disable interrupts while processing an interrupt?

#### Our processor

- Over 100 interrupt sources

- Power on reset, bus errors, I/O pins changing state, data in on a serial bus etc.

- Need a great deal of control

- Ability to enable and disable interrupt sources

- Ability to control where to branch to for each interrupt

- Ability to set interrupt priorities

- Who wins in case of a tie

- Can interrupt A interrupt the ISR for interrupt B?

- If so, A can "preempt" B.

- All that control will involve memory mapped I/O.

- And given the number of interrupts that's going to be a pain

16

## SmartFusion interrupt sources

17

| Cortice-M3 NVIC Input | RQ Label           | IRQ Source       |

|-----------------------|--------------------|------------------|

| NMI                   | WDOGTIMEOUT_RQ     | WATCHDOG         |

| INTISR(0)             | WDOGWAKEUP_IRQ     | WATCHDOG         |

| INTISR[1]             | BROWNOUT1_5V_IRQ   | VR/PSM           |

| INTER[2]              | BROWNOUT3_3V_IRQ   | VRFSM            |

| INTISR[3]             | RTCMATCHEVENT_IRQ  | RTC              |

| INTER[4]              | PU_N_IRQ           | RTC              |

| INTISR[5]             | EMAC_IRQ           | Ethernet MAC     |

| INTISR[6]             | M3_IAP_IRQ         | IAP              |

| INTISR[7]             | ENVM_0_IRQ         | ENVM Controller  |

| INTER[6]              | ENVM_1_RQ          | ENVM Controller  |

| INTISR[9]             | DMA_RIQ            | Peripheral DMA   |

| INTER[10]             | UART_0_IRQ         | UART_0           |

| INTISR[11]            | UART_1_IRQ         | UART_1           |

| INTISR[12]            | SPI_0_IRQ          | SPI_0            |

| INTISR[13]            | SPI_1_IRQ          | SPI_1            |

| INTER[14]             | 12C_0_RQ           | 120_0            |

| INTISR[15]            | I2C_0_SMBALERT_IRQ | 120_0            |

| INTISR[16]            | I2C_0_SMBSUS_IRQ   | 120_0            |

| INTISR[17]            | 12C_1_IRQ          | 120_1            |

| INTISR[18]            | I2C_1_SMBALERT_IRQ | 120_1            |

| INTISR[19]            | I2C_1_SMBSUS_IRQ   | 120_1            |

| INTISR[20]            | DAL_1_R1MIT        | TIMER            |

| INTISR[21]            | TIMER_2_RQ         | TIMER            |

| INTISR[22]            | PLLLOCK_IRQ        | MSS_CCC          |

| INTISR[23]            | PLLLOCKLOST_IRQ    | MSS_CCC          |

| INTISR[24]            | ABM_ERROR_RQ       | AHB BUS MATRO    |

| INTISR[25]            | Reserved           | Reserved         |

| INTISR[26]            | Reserved           | Reserved         |

| INTISR[27]            | Reserved           | Reserved         |

| INTISR[28]            | Reserved           | Reserved         |

| INTISR[29]            | Reserved           | Reserved         |

| INTISR[30]            | Reserved           | Reserved         |

| INTISR[31]            | FAB_IRQ            | FABRIC INTERFACE |

|                       |                    |                  |

| INTISR[65] | ACE_PC0_FLAG1_RQ       | ACE |

|------------|------------------------|-----|

| INTISR[66] | ACE_PC0_FLAG2_RQ       | ACE |

| INTISR[67] | ACE_PC0_FLAG3_IRQ      | ACE |

| INTISR[68] | ACE_PC1_FLAGE_RRQ      | ACE |

| INTISR[60] | ACE_PC1_FLAG1_RQ       | ACE |

| INTISR[70] | ACE_PC1_FLAG2_IRQ      | ACE |

| INTISR[71] | ACE_PC1_FLAG3_RQ       | ACE |

| INTISR[72] | ACE_PC2_FLAGE_RRQ      | ACE |

| INTISR[73] | ACE_PC2_FLAG1_RQ       | ACE |

| INTISR[74] | ACE_PC2_FLAG2_RQ       | ACE |

| INTISR[75] | ACE_PC2_FLAG3_IRQ      | ACE |

| INTISR[76] | ACE_ADC0_DATAVALID_IRQ | ACE |

| INTISR[77] | ACE_ADC1_DATAVALID_IRQ | ACE |

| INTISR[78] | ACE_ADC2_DATAVALID_IRQ | ACE |

| INTISR[79] | ACE_ADC0_CALDONE_IRQ   | ACE |

| INTISR(80) | ACE_ADC1_CALDONE_IRQ   | ACE |

| INTISR[81] | ACE_ADC2_CALDONE_IRQ   | ACE |

| INTISR(82) | ACE_ADCO_CALSTART_IRQ  | ACE |

| INTISR(83) | ACE_ADC1_CALSTART_IRQ  | ACE |

| INTISR[84] | ACE_ADC2_CALSTART_IRQ  | ACE |

| INTISR[85] | ACE_COMP0_FALL_IRQ     | ACE |

| INTISR[86] | ACE_COMP1_FALL_RQ      | ACE |

| INTISR[87] | ACE_COMP2_FALL_IRQ     | ACE |

| INTISR(88) | ACE_COMP3_FALL_IRQ     | ACE |

| INTISR(89) | ACE_COMP4_FALL_IRQ     | ACE |

| INTISR[90] | ACE_COMPS_FALL_IRQ     | ACE |

| INTISR[91] | ACE_COMP6_FALL_IRQ     | ACE |

| INTISR[92] | ACE_COMP7_FALL_IRQ     | ACE |

| INTISR[93] | ACE_COMP8_FALL_IRQ     | ACE |

| INTISR[94] | ACE_COMP9_FALL_IRQ     | ACE |

| INTISR(95) | ACE                    |     |

54 more ACE specific interrupts

GPIO\_3\_IRQ to GPIO\_31\_IRQ cut

Usage fault

Debug monitor Programmable Debug monitor (preekpoints, watchpoi external debug requests)

Reserved NA — Rogrammable Pendable Service Call

SYSTICK Programmable System Tick Timer

| Table 7.2 List of External | Table 7.2 List of External Interrupts |              |  |  |  |  |

|----------------------------|---------------------------------------|--------------|--|--|--|--|

| Exception Number           | Exception Type                        | Priority     |  |  |  |  |

| 16                         | External Interrupt #0                 | Programmable |  |  |  |  |

| 17                         | External Interrupt #1                 | Programmable |  |  |  |  |

|                            |                                       | •••          |  |  |  |  |

| 255                        | External Interrupt #239               | Programmable |  |  |  |  |

18

# And the interrupt vectors (in startup\_a2fxxxm3.s found in CMSIS, startup\_gcc)

| fnVecto | rs:                |

|---------|--------------------|

| .word   | _estack            |

| .word   | Reset_Handler      |

| .word   | NMI_Handler        |

| .word   | HardFault_Handler  |

| .word   | MemManage_Handler  |

| .word   | BusFault_Handler   |

| .word   | UsageFault_Handler |

| .word   | 0                  |

| .word   | SVC_Handler        |

| .word   | DebugMon_Handler   |

| Exception<br>Number | Exception Type         | Priority     | Description                                                                                                                                                                              |

|---------------------|------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                   | Reset                  | -3 (Highest) | Reset                                                                                                                                                                                    |

| 2                   | NM                     | -2           | Normaskable interrupt (external N                                                                                                                                                        |

| 3                   | Hard fault             | -1           | All fault conditions if the correspon<br>handler is not enabled                                                                                                                          |

| 4                   | MemManage fault        | Programmable | Memory management fault; Memo<br>Protection Unit (MPU) violation or<br>to lilegal locations                                                                                              |

| 5                   | Bus fault              | Programmable | Bus error; occurs when Advanced<br>Parformance Bus (AHB) interface<br>error response from a bus slave (a<br>prefetch abort if it is an instruction<br>data abort if it is a data access) |

| 6                   | Usage fault            | Programmable | Exceptions resulting from program<br>trying to access coprocessor (the<br>does not support a coprocessor)                                                                                |

| 7-10                | Reserved               | NA           | _                                                                                                                                                                                        |

| 11                  | SVC                    | Programmable | Supervisor Call                                                                                                                                                                          |

| 12                  | Dabug monitor          | Programmable | Debug monitor (breakpoints, wato<br>external debug requests)                                                                                                                             |

| 13                  | Reserved               | NA           |                                                                                                                                                                                          |

| 14                  | PendSV                 | Programmable | Pendable Service Call                                                                                                                                                                    |

| 15                  | SYSTICK                | Programmable | System Tick Timer                                                                                                                                                                        |

| Table 7.2 List      | of External Interrupts |              |                                                                                                                                                                                          |

| Exception Nun       |                        | ception Type | Priority                                                                                                                                                                                 |

| 0                     | 16  |

|-----------------------|-----|

| •                     | 17  |

| PendSV Handler        | *** |

|                       | 255 |

| SysTick_Handler       |     |

| WdogWakeup_IRQHandler |     |

| BrownOut_1_5V_IRQHand | ler |

|                       |     |

.word BrownOut\_3\_3V\_IRQHandler

.....(they continue)

.word

.word

How to change where to go on an interrupt? Answer: edit the interrupt vector table [IVT]

```

23 privectors:

24 .word _estack

25 .word Reset Handler

26 .word NMI_Handler

27 .word HardFault Handler

28 .word MemManage_Handler

29 .word BusFault_Handler

30 .word UsageFault_Handler

31 .word 0

32 .word 0

32 .word 0

32 .word 0

35 .word 0

36 .vord 0

37 .word 0

38 * Reset_Handler

39 */

195 .global Reset_Handler

396 .type Reset_Handler, %function

397 Reset_Handler:

398 _start:

```

20

19

• Interrupt Set Enable and Clear Enable

Enabling and disabling interrupt sources

- 0xE000E100-0xE000E11C, 0xE000E180-0xE000E19C

| 0xE000E100 | SETENA0 | R/W | 0 | Enable for external interrupt #0-31              |

|------------|---------|-----|---|--------------------------------------------------|

|            |         |     |   | bit[0] for interrupt #0 (exception #16)          |

|            |         |     |   | bit[1] for interrupt #1 (exception #17)          |

|            |         |     |   |                                                  |

|            |         |     |   | bit[31] for interrupt #31 (exception #47)        |

|            |         |     |   | Write 1 to set bit to 1; write 0 has no effect   |

|            |         |     |   | Read value indicates the current status          |

| 0xE000E180 | CLRENA0 | R/W | 0 | Clear enable for external interrupt #0-31        |

|            |         |     |   | bit[0] for interrupt #0                          |

|            |         |     |   | bit[1] for interrupt #1                          |

|            |         |     |   |                                                  |

|            |         |     |   | bit[31] for interrupt #31                        |

|            |         |     |   | Write 1 to clear bit to 0; write 0 has no effect |

|            |         |     |   | Read value indicates the current enable status   |

## Configuring the NVIC (2)

- Set Pending & Clear Pending

- 0xE000E200-0xE000E21C, 0xE000E280-0xE000E29C

| 0xE000E200 | SETPEND0 | R/W | 0 | Pending for external interrupt #0-31 bit[0] for interrupt #0 (exception #16) bit[1] for interrupt #1 (exception #17) bit[31] for interrupt #31 (exception #47) Write 1 to set bit to 1; write 0 has no effect                                                         |

|------------|----------|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          |     |   | Read value indicates the current status                                                                                                                                                                                                                               |

| 0xE000E280 | CLRPENDO | R/W | 0 | Clear pending for external interrupt #0-31 bit[0] for interrupt #0 (exception #16) bit[1] for interrupt #1 (exception #17) bit[31] for interrupt #31 (exception #47) Write 1 to clear bit to 0; write 0 has no effect Read value indicates the current pending status |

-l 22

# Configuring the NVIC (3)

- Interrupt Active Status Register

- 0xE000E300-0xE000E31C

| Address    | Name    | Type | Reset Value | Description                                 |

|------------|---------|------|-------------|---------------------------------------------|

| 0xE000E300 | ACTIVE0 | R    | 0           | Active status for external interrupt #0-31  |

|            |         |      |             | bit[0] for interrupt #0                     |

|            |         |      |             | bit[1] for interrupt #1                     |

|            |         |      |             |                                             |

|            |         |      |             | bit[31] for interrupt #31                   |

| 0xE000E304 | ACTIVE1 | R    | 0           | Active status for external interrupt #32-63 |

|            | _       | -    | -           | _                                           |

# Interrupt types

- Two main types

- Level-triggered

- Edge-triggered

#### Level-triggered interrupts

- · Signaled by asserting a line low or high

- Interrupting device drives line low or high and holds it there until it is serviced

- · Device deasserts when directed to or after serviced

- Can share the line among multiple devices (w/ OD+PU)

- · Active devices assert the line

- · Inactive devices let the line float

- Easy to share line w/o losing interrupts

- But servicing increases CPU load → example

- · And requires CPU to keep cycling through to check

- Different ISR costs suggests careful ordering of ISR checks

- Can't detect a new interrupt when one is already asserted

25

#### **Edge-triggered interrupts**

- Signaled by a level \*transition\* (e.g. rising/falling edge)

- · Interrupting device drive a pulse (train) onto INT line

- What if the pulse is too short? Need a pulse extender!

- Sharing \*is\* possible...under some circumstances

- INT line has a pull up and all devices are OC/OD.

- Devices \*pulse\* lines

- Could we miss an interrupt? Maybe...if close in time

- · What happens if interrupts merge? Need one more ISR pass

- Must check trailing edge of interrupt

- Easy to detect "new interrupts"

- Benefits: more immune to unserviceable interrupts

- · Pitfalls: spurious edges, missed edges

- · Source of "lockups" in early computers

26