Your state machine will also interact with another device: a 4-bit binary counter. Your state machine will control that counter and use it as an input. This type of interaction between a state machine and another device is fairly common---and in this case it greatly reduces the number of states needed.

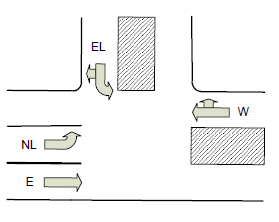

In this lab, there are 4 inputs (the traffic sensors), and 4 outputs (the traffic lights associated with each sensor) as well as a reset. The sensor names are:

- W -- West-bound straight (and north left)

- E -- East-bound straight

- NL -- North-bound left

- EL -- East-bound left

Each sensor is either on (indicating a car is present in that lane) or off (indicating no car is present).

The traffic lights associated with each direction have the same name, but end in a "TL". So ETL is the east-bound straight traffic light. Each light can be Green, Yellow or Red.

You DO NOT need a turn light to go north from the west bound lane (W) or west from the east left lane (EL). Assume the driver will yield to traffic.

Figure 1: The Intersection

The system clock is assumed to have a period of 1 second.

Your traffic light controller is to follow the following rules. These rules are NOT a complete specification. That is, there is some ambiguity in what to do in certain situations. You need to pick some reasonable behavior for those situations.

- Two lanes of traffic are considered to "conflict" if having both of them going at the same time could cause a collision (that is if their paths cross). For example, having the both Eastbound straight light and Eastbound left light Green or Yellow at the same time could cause a collision, so those lanes "conflict" with each other.

- No two lanes in conflict should have "Green" or "Yellow" at the same time.

- When a light is to change from Green to Red, it should be Yellow for exactly one second in between the Green and Red. A light may never go from yellow to green, nor from red to yellow.

- There should be no "starvation". That is, if a given sensor is on, its lane should get a Green light at some point, no matter the state of the other sensors.

- When sensors for two conflicting lanes are on, no one direction should be Green for more than 10 seconds.

- When only one sensor is on, that light must become Green as quickly as possible and stay Green until some sensor input changes, without violating the other rules.

- No Green should be less than 3 seconds in duration.

- When no sensor is on, the default configuration should rotate through different states so that all lights are green at some point. (So if all the sensors stop working no one will have to wait forever).

- You should not give a lane a red light when there is no traffic conflicting with that lane. In other words, it should never be the case that a given light could be Green (at the same time as another lane) but isn't.

- The controller should have a reset. When reset is high the system should go to (and stay in) some legal state. As in the previous lab, this should be a synchronous reset.

- If there are exactly two sensors activated for non-conflicting lanes, both of these lights should become green as quickly as possible without violating the other rules.

- The traffic lights should behave in a way that you think would best move traffic through the intersection given the above rules.

The Counter

All timing-related issues greater than 1 second are to be handled by a 4-bit saturating counter. You may use the Verilog operators >, < and == to compare to the current value of the counter. The only control you have over the counter is a reset line. The counter reset is independent of the system reset. You may want to label it counter reset in your design. A counter module is provided for you (on the lab web page).

Mapping inputs and outputs

- The clock is to be the right-most push-button.

- The sensors E, NL, EL and W should be mapped to dip switches 3 to 0 in that order.

- The traffic light status

should be displayed on the hex

displays 3 to 0 in the same order as their respective sensors.

- When Red, the display should be "r".

- When Green, the display should be "g".

- When Yellow, the display should be "E"

Finally, we strongly suggest you write the state machine the way that we show in the sequential logic tutorial. You are required to have separate always blocks for the next-state logic and the output logic.

- The best starting point is to figure out how many "basic" states you will have. That is, how many different states have only green and red lights? Draw those states, then think about what you want to do when transitioning between them.

- Think about how to use the counter. If you find yourself doing complex comparisons, you are probably doing something wrong. Also think about when you will need to reset the counter.

- Make heavy use of Verilog macros or parameters, both to name the states and to describe the outputs to the hex displays.

- You may need to add other inputs or outputs (reset for the counter, perhaps?)

- You should need no more than four bits to keep track of the state, though the instructor's solution uses only three.

- To plan your state transitions, you may find it helpful to designate a "default" rotation (which satisfies rule number 8). Then think about what input combinations would require your machine to deviate from this default rotation. If you think about the transitions out of a particular state in terms of if/else statements, the special cases would be the "if" and the default would be the "else."

- You

should not be assigning values to individual hex segments.

(These are examples and may not specifically apply to this lab) Instead

you should be assigning to all of the hex segments in a given

display at once. So ETL=7'b1111010;

(or better yet, ETL=Red,

where Red is a parameter set to 7'b1111010), rather than

ETL[0]=1;

ETL[1]=1;

etc. - Your output logic should look similar to this

begin

WLTL = Red;

SLTL = Red;

WTL = Green;

Provide a state diagram that implements your traffic light controller. The logic on the transitions may be fairly complex, so feel free to simply label the transitions and put the logic equation elsewhere on the page. You may use if then else statements to express your transition equations as you will in Verilog. As in the previous lab, do not include reset on this diagram. Use the naming conventions used above. You should expect to have things like "Counter<3" as conditions on your state machine. Also think about when you want to reset the counter (this should be an output of your state machine).

Get started on the In-Lab!

Demonstrate your working traffic light controller (55 points)

Post-Lab

(30 Points) Submit answers to the following questions.

- List the inputs and

outputs for the next-state logic (remember

that

next state is a function of sensor inputs, current state, and count).

How

many rows and columns would this truth table have? (5 points)

- List the inputs and outputs for the output logic, not including

the counter.(Hex outputs are a function of current state.) How many

rows and columns would this truth table have? (5 points)

- How many states are there in your FSM? How many D flip-flops are required to hold all of these states? Do you have unused states? If so, how many? (5 points).

- If you had used a one-hot

encoding, how many D flip-flops

would you need? (5 points).

- Each segment of the 7 segment displays is the output of a logic function of the current state. Determine the logical function for segment 3 of the W, 7-segment display. Provide the minimal SOP and K-map. (10 points)