# EECS 470 Midterm Exam

## Winter 2018

| Name:                                           | unique name:                            |

|-------------------------------------------------|-----------------------------------------|

| Sign the honor code:                            |                                         |

| I have neither given nor received aid on this e | exam nor observed anyone else doing so. |

### Scores:

### **NOTES:**

- Open book and Open notes

- Calculators are allowed, but no PDAs, Portables, Cell phones, etc.

- Don't spend too much time on any one problem.

- You have about 120 minutes for the exam.

- There are  $\underline{9}$  pages including this one.

- Be sure to show work and explain what you've done when asked to do so.

- The last page has two "answer areas" for the last question. Clearly mark which one you want graded or we will grade the first one.

- 1. Fill-in-the-blank or circle the best answer [17 points, -2 per wrong/blank, minimum 0]

- a. When using the R10K algorithm, if you have B reorder buffer entries, S reservation stations, and A architected registers you can be sure that you will not have a use for more than  $\underline{B+S/B+A/A+S}$  physical registers.

- b. In the P6 scheme an instruction might find its data in one of three places. Those three places are \_\_\_\_\_\_\_, \_\_\_\_\_\_\_, or \_\_\_\_\_\_\_. In the R10K scheme there are two / three / four places an instruction might find its data.

c. Given an 8-KB four-way associative cache with 16-byte cache lines and a 32-bit address space there will be \_\_\_\_\_\_\_ bits used for the index. If that same cache were fully-associative you'd need \_\_\_\_\_\_ bits to be used for the index.

- d. The BTB generally does a poor job with predicting the target address of a *function call / function return / PC-relative branch*.

- e. A cylindrical metal wire which is 1mm long and has a diameter of 10nm will have the *higher / lower / the same* resistance as a wire made of the same material which is 2mm long and has a diameter of 20nm.

- f. Adding more reservation stations will reduce the amount of time that the processor stalls due to <u>structural hazards / data hazards / control hazards</u> but may decrease the <u>number of branch delay slots / clock period / clock frequency.</u>

- g. In the R10K scheme, if you have 32 RoB entries, 16 architected registers, 6 reservation stations and 48 PRFs, you should never have a structural hazard due to the lack of a *PRF entry / reservation station / RoB entry / floating point divide*.

| 2. | hazard). Sand that the instruction | the pipelined processor you did as part of project 3 (including the structural Say 20% of all instructions were loads, 25% were branches, and 10% were stores are program was quite long (millions and millions of instructions). 20% of all as are data dependent on the instruction in front of them, and branches are taken the time. What would you expect the CPI to be? Show your work. [6 points] |

|----|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3. |                                    | ach of the following questions in 40 words or less. [11 points]  Why don't we let stores write to memory as soon as their address and data are known? [3]                                                                                                                                                                                                                                                |

|    | b.                                 | In the P6 scheme, under what circumstances does a committing instruction update the RAT? Be precise and be sure to consider all types of instructions. [4]                                                                                                                                                                                                                                               |

- 4. Consider a set of code where there are three classes of instructions.

- "Short" instructions are not dependent on any other instruction and can execute in 4 cycles.

- "Long" instructions are not dependent on any other instruction and can execute in 50 cycles.

- "Dependent" instructions are (only) dependent on the instruction in front of them and take 4 cycles to execute.

Say you have a machine which can issue one instruction per cycle, finish execution of one instruction per cycle, and retire one instruction per cycle. This machine implements what we have called the "P6" algorithm and it keeps an instruction in its RS until that instruction has finished executing. The machine has an RS size of 12 and a RoB size of 64 unless otherwise noted. You may assume the machine otherwise has unlimited resources (execution units etc.) You must show/explain your work to get credit!

| _  | [12 points]                                                                                                              |

|----|--------------------------------------------------------------------------------------------------------------------------|

| a. | What is the best CPI this machine could achieve if the program being run consisted of only "long" instructions? [3]      |

| b. | What is the best CPI this machine could achieve if the program being run consisted of only "short" instructions? [3]     |

| c. | What is the best CPI this machine could achieve if the program being run consisted of only "dependent" instructions? [3] |

d. What is the best CPI this machine could achieve if the program being run consisted of groups of 50 instructions, where the first 49 were "dependent" and the last was "short"? Assume there are a large number of these groups. [3]

5. Consider the following pseudo-assembly code:

```

r2=0

r4=0

r5=0

bob: r3=(r2 mod 3) // remainder when r2 is divided by 3

if(r3==0) goto next // Branch 1

r6=r6+1

next: r5=r5+4

r2=MEM[r5+0] // Load

if(r6<1000000) goto bob // Branch 2</pre>

```

"bob" has an address of 0x1000. The predictors all use the least significant bits of the PC other than the word-offset. Predictors are all initialized to "0" or "00" which is "not-taken" and "strongly not-taken" respectively. Global history is initialized as if all branches had been not taken.

You are to consider how different branch predictors will behave on this code under different circumstances.

- <u>Case 1:</u> The data from the load will be "1" the first time, "2" the second, "3" the third etc.

- <u>Case 2:</u> The data random. That is it could be any value that fits in a 32-bit integer with equal probability.

You are now to consider 3 branch predictors:

- **Predictor 1:** A bimodal predictor with 4 entries each a 2-bit saturating counter.

- **Predictor 2:** A bimodal predictor with 8 entries each 1 bit.

- **Predictor 3:** A Gshare predictor with 4 entries each 1 bit.

What are the expected *mispredict* rates for each of the following? You only need to worry about steady state values (assume 1000000 is a really big number.)

[15 points, -1.5 per wrong or blank box, min 0]

|             | Case 1   |          | Case 2   |          |  |

|-------------|----------|----------|----------|----------|--|

|             | Branch 1 | Branch 2 | Branch 1 | Branch 2 |  |

| Predictor 1 |          |          |          |          |  |

| Predictor 2 |          |          |          |          |  |

| Predictor 3 |          |          |          |          |  |

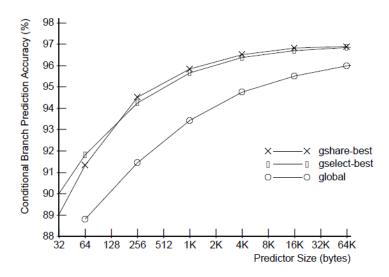

6. The graph to the right comes from the "Combining Branch Predictors" paper that was assigned as a reading for the course. In your own words, describe what "best" means in the context of both gselect-best and gshare-best.

[7 points]

a. "gselect-best" [3]

b. "gshare-best" [4]

- 7. MOV instructions in modern x86 architectures can often be implemented without actually writing the value from one register to another. Instead, the Map Table simply renames the architectural register of the destination to the same physical register as the source at dispatch. This is often called Move Elimination. Move Elimination effectively takes the MOV instruction out of the execution pipeline as it doesn't need to be issued. For this question, assume you are implementing this feature on top of an R10k microarchitecture. [13 points]

- a. Name one advantage to this technique other than speeding up the MOV instruction.[2]

b. Does the MOV instruction need to broadcast on the CDB? Why or why not? [5]

c. Consider the following code running on a processor where Move Elimination has been implemented. When can you free the physical register that is assigned to \$r0 in the first instruction? Explain your answer. [6]

```

ADD $r4 $r2 $r0

//r0 = r4 + r2

//r1 = r0

MOV $r0 $r1

MOV $r1 $r13

//r13 = r1

ADD $r9 $r1 $r1

//r1 = r9 + r1

ADD $r6 $r0 $r0

//r0 = r6 + r0

//r7 = r13 * r3

MUL $r13 $r3 $r7

//r13 = r0 + r1

ADD $r0 $r1 $r13

ADD $r0 $r13 $r1

//r1 = r0 + r13

MUL $r7 $r1 $r0

//r0 = r7 * r1

```

8. Consider the following state of a machine implementing what we've called Tomasulo's third algorithm. [19 points]

| RAT           |              |  |  |  |

|---------------|--------------|--|--|--|

| Arch<br>Reg # | Phy.<br>Reg# |  |  |  |

| 0             | 7            |  |  |  |

| 1             | 6            |  |  |  |

| 2             | 3            |  |  |  |

| 3             | 4            |  |  |  |

| 4             | 9            |  |  |  |

| ROB              |    |           |             |              |                                         |  |  |

|------------------|----|-----------|-------------|--------------|-----------------------------------------|--|--|

| Buffer<br>Number | PC | Executed? | Dest<br>ARN | Dest.<br>PRN | Replaced<br>Phy. Reg#<br>(Back pointer) |  |  |

| 0                | 12 | N         | 0           | 0            | 1                                       |  |  |

| 1                | 16 | Y         | 1           | 6            | 2                                       |  |  |

| 2                | 20 | N         | 0           | 7            | 0                                       |  |  |

| 3                | 24 | Y         |             |              |                                         |  |  |

| 4                | 80 | N         | 4           | 8            | 5                                       |  |  |

| 5                | 84 | Y         | 4           | 9            | 8                                       |  |  |

| 6                |    |           |             |              |                                         |  |  |

| 7                |    |           |             |              |                                         |  |  |

| 8                |    |           |             |              |                                         |  |  |

| Initial Head=0 | _ |

|----------------|---|

| Initial Tail=6 |   |

| Final Head= |

|-------------|

| Final Tail= |

|     | RS         |               |                  |               |                  |             |     |  |  |

|-----|------------|---------------|------------------|---------------|------------------|-------------|-----|--|--|

| RS# | Op<br>Type | Op1<br>Ready? | Op1<br>PRN/value | Op2<br>Ready? | Op2<br>PRN/value | Dest<br>PRN | ROB |  |  |

| 0   | Add        | Y             | -1               | Y             | 2                | 0           | 0   |  |  |

| 1   | Mult       | N             | 7                | Y             | 4                | 8           | 4   |  |  |

| 2   | Add        | N             | 0                | Y             | 2                | 7           | 2   |  |  |

| 3   |            |               |                  |               |                  |             |     |  |  |

| 4   |            |               |                  |               |                  |             |     |  |  |

| PRF         |    |      |       |  |  |  |

|-------------|----|------|-------|--|--|--|

| Phy Reg #   |    | Free | Valid |  |  |  |

| 0           | 1  | N    | N     |  |  |  |

| 1           | 2  | N    | Y     |  |  |  |

| 2           | -1 | N    | Y     |  |  |  |

| 1<br>2<br>3 | 4  | N    | Y     |  |  |  |

| 4           | 5  | N    | Y     |  |  |  |

| 5           | 6  | N    | Y     |  |  |  |

| 6           | 20 | N    | Y     |  |  |  |

| 7           | 8  | N    | N     |  |  |  |

| 8           | 9  | Y    | N     |  |  |  |

| 9           | 10 | Y    | Y     |  |  |  |

| 10          | 11 | Y    | N     |  |  |  |

| 11          | 12 | Y    | N     |  |  |  |

| 12          | 13 | Y    | N     |  |  |  |

### KEY:

- **Op1 PRN/value** is the value of the first argument if "Op1 ready?" is yes; otherwise it is the Physical Register Number that is being waited upon.

- Op2 PRN/value is the same as above but for the second argument.

- **Dest. PRN** is the destination Physical Register Number.

- **Dest. ARN** is the destination Architectural Register Number.

- **ROB** is the associated ROB entry for this instruction.

- **Free/Valid** indicates if the PRF entry is currently available for allocation and if the valid in it is valid, *No register should be valid and free!*

- a. Say that the instruction in ROB #3 is a branch and it was mis-predicted: the next PC should have been 28. Say that the instruction in memory location 28 is R2=R0+R4 and in 32 is R2=R4+R2. Update the machine to the state where the branch has left the RoB, and the instructions at memory locations 28 and 32 have <u>dispatched</u> but <u>not executed</u>. When allocating a new PRF entry, pick the <u>highest</u> number available. Otherwise, when faced with an arbitrary decision, just be sure to make a legal choice. [16]

- b. What was the assembly instruction that is found at memory location 80? Your answer should be of the form: "r1=r2+r3" or something similar. *Your answer may not include an immediate*. [3]

On the following page is an extra copy of this state. You may use this one or the one on the next page but be sure to cross out (with a BIG X) the one you don't want graded. *Also, be sure to answer the following question.*

| R.A          | RAT           |  |  |  |  |

|--------------|---------------|--|--|--|--|

| Arch<br>Reg# | Phy.<br>Reg # |  |  |  |  |

| 0            | 7             |  |  |  |  |

| 1            | 6             |  |  |  |  |

| 3            | 3             |  |  |  |  |

| 3            | 4             |  |  |  |  |

| 4            | 9             |  |  |  |  |

| ROB              |    |           |             |              |                                         |  |

|------------------|----|-----------|-------------|--------------|-----------------------------------------|--|

| Buffer<br>Number | PC | Executed? | Dest<br>ARN | Dest.<br>PRN | Replaced<br>Phy. Reg#<br>(Back pointer) |  |

| 0                | 12 | N         | 0           | 0            | 1                                       |  |

| 1                | 16 | Y         | 1           | 6            | 2                                       |  |

| 2                | 20 | N         | 0           | 7            | 0                                       |  |

| 3                | 24 | Y         |             |              |                                         |  |

| 4                | 80 | N         | 4           | 8            | 5                                       |  |

| 5                | 84 | Y         | 4           | 9            | 8                                       |  |

| 6                |    |           |             |              |                                         |  |

| 7                |    |           |             |              |                                         |  |

| 8                |    |           |             |              |                                         |  |

| Initial Head=0 |  |

|----------------|--|

| Initial Tail=6 |  |

| Final Head= |

|-------------|

| Final Tail= |

| RS  |            |               |                  |               |                  |             |     |  |

|-----|------------|---------------|------------------|---------------|------------------|-------------|-----|--|

| RS# | Op<br>Type | Op1<br>Ready? | Op1<br>PRN/value | Op2<br>Ready? | Op2<br>PRN/value | Dest<br>PRN | ROB |  |

| 0   | Add        | Y             | -1               | Y             | 2                | 0           | 0   |  |

| 1   | Mult       | N             | 7                | Y             | 4                | 8           | 4   |  |

| 2   | Add        | N             | 0                | Y             | 2                | 7           | 2   |  |

| 3   |            |               |                  |               |                  |             |     |  |

| 4   |            |               |                  |               |                  |             |     |  |

| PRF             |       |      |       |  |  |  |

|-----------------|-------|------|-------|--|--|--|

| Phy<br>Reg<br># | Value | Free | Valid |  |  |  |

| 0               | 1     | N    | N     |  |  |  |

| 1               | 2     | N    | Y     |  |  |  |

| 2               | -1    | N    | Y     |  |  |  |

|                 | 4     | N    | Y     |  |  |  |

| 4               | 5     | N    | Y     |  |  |  |

| 5               | 6     | N    | Y     |  |  |  |

| 6               | 20    | N    | Y     |  |  |  |

| 7               | 8     | N    | N     |  |  |  |

| 8               | 9     | N    | N     |  |  |  |

| 9               | 10    | N    | Y     |  |  |  |

| 10              | 11    | Y    | N     |  |  |  |

| 11              | 12    | Y    | N     |  |  |  |

| 12              | 13    | Y    | N     |  |  |  |

### KEY:

- **Op1 PRN/value** is the value of the first argument if "Op1 ready?" is yes; otherwise it is the Physical Register Number that is being waited upon.

- Op2 PRN/value is the same as above but for the second argument.

- **Dest. PRN** is the destination Physical Register Number.

- **Dest. ARN** is the destination Architectural Register Number.

- **ROB** is the associated ROB entry for this instruction.

- **Free/Valid** indicates if the PRF entry is currently available for allocation and if the valid in it is valid, *No register should be valid and free!*

Be sure to cross out (with a BIG X) the one (this one or the one on the previous page) you don't want graded

Notice that there is a part "b" to the question. Please answer it on the previous page.