# Early Design Cycle Timing Simulation of Caches

## **Preliminary Exam Report**

Edward S. Tam estam@eecs.umich.edu

Advisor: Edward S. Davidson davidson@eecs.umich.edu

Department of Electrical Engineering and Computer Science The University of Michigan Ann Arbor, Michigan

September 9, 1996

| Table | of | Contents |

|-------|----|----------|

|-------|----|----------|

| List of | Figure | s                                                                | iii |

|---------|--------|------------------------------------------------------------------|-----|

| List of | Tables |                                                                  | iv  |

| Abstra  | .ct    |                                                                  | v   |

| 1.0     | Introd | action                                                           | 1   |

| 2.0     | Cache  | overview                                                         | 3   |

|         | 2.1    | Components of cache design                                       |     |

|         | 2.2    | Terminology                                                      | 6   |

| 3.0     | Overv  | iew of cache simulation                                          | 8   |

|         | 3.1    | Currently available behavioral cache simulators                  | 8   |

|         | 3.2    | The LE cache model                                               | 9   |

| 4.0     | Impler | nenting the LE cache model                                       | 17  |

|         | 4.1    | DineroIII                                                        |     |

|         | 4.2    | Resource Conflict Methodology                                    |     |

|         | 4.3    | Implementing LE on top of DineroIII                              |     |

|         | 4.4    | The LE cache model outside of DineroIII                          |     |

|         |        | 4.4.1 Trailing edge effects                                      |     |

|         |        | 4.4.2 Bus width issues                                           |     |

|         |        | 4.4.3 Number of outstanding accesses                             |     |

|         |        | 4.4.4 Port limitations                                           |     |

|         |        | 4.4.5 Flow chart diagramming the operation of the LE cache model |     |

|         | 4.5    | Using the RCM model to implement LE                              |     |

| 5.0     | Experi | mental results                                                   |     |

|         | 5.1    | Characterizing the RS/6000 cache                                 |     |

|         | 5.2    | Comparing the simulator output to actual machine performance     |     |

|         |        | 5.2.1 Load/store kernel simulation performance                   |     |

|         |        | 5.2.2 The Livermore Loop Kernels                                 |     |

|         | 5.3    | Accuracy of the output                                           |     |

|         | 5.4    | Analyzing the flexibility of the LE cache model                  |     |

|      | 5.4.1         | Varying latencies                                    |  |

|------|---------------|------------------------------------------------------|--|

|      | 5.4.2         | Varying the number of ports                          |  |

|      | 5.4.3         | Varying bus widths                                   |  |

|      | 5.4.4         | Varying the number of outstanding accesses allowable |  |

| 6.0  | Execution tim | nes                                                  |  |

| 7.0  | LE output     |                                                      |  |

| 8.0  | Conclusion    |                                                      |  |

| 9.0  | Future work   |                                                      |  |

| 10.0 | Acknowledgr   | nents                                                |  |

| 11.0 | References    |                                                      |  |

~

## List of Figures

| Figure 1:  | Program 1                                                                                 | 9   |

|------------|-------------------------------------------------------------------------------------------|-----|

| Figure 2:  | One block-aligned portion of memory (blocksize = 64B)                                     |     |

| Figure 3:  | Execution behavior of Program 1 according to unmodified DineroIII                         | 10  |

| Figure 4:  | Execution behavior of Program 1 for leading edge latency-augmented DineroIII              | .11 |

| Figure 5:  | Execution of Program 1 when trailing edge effects are taken into account and 4 read       |     |

|            | ports are available                                                                       | 12  |

| Figure 6:  | Execution of Program 1 with words from memory returning in sequential cycles              |     |

|            | with only 1 read port to the cache                                                        | 13  |

| Figure 7:  | Program 2                                                                                 | 13  |

| Figure 8:  | Another block-aligned portion of memory (blocksize = 64B)                                 |     |

| Figure 9:  | Execution of Program 2 with words returning from memory in sequential cycles              | 14  |

| Figure 10: | Execution of Program 1 on a processor whose cache can only sustain two outstanding        |     |

|            | accesses at a time with 1 read port to the cache                                          | 15  |

| Figure 11: | Program 3                                                                                 | 16  |

| Figure 12: | Execution of Program 3 on a processor whose cache can only sustain two outstanding        |     |

|            | accesses at a time                                                                        |     |

| Figure 13: | State of update_buffer when the access to address C is being evaluated                    |     |

| Figure 14: | State of update_buffer after access to address C has been evaluated                       | 22  |

| Figure 15: | Flow chart showing the operation of the LE cache model                                    |     |

| Figure 16: | A high-level picture of the overall processor/cache simulator, RCM_brisc+LE               | 31  |

| Figure 17: | Interaction between the processor simulator, RCM_brisc, and LE                            | 32  |

| Figure 18: | Basic cache parameterization program                                                      | 33  |

| Figure 19: | Example load kernel                                                                       |     |

| Figure 20: | Load kernel performance                                                                   | 34  |

| Figure 21: | Sample store kernel                                                                       | 35  |

| Figure 22: | Store kernel performance                                                                  | 35  |

| Figure 23: | Execution times of each of the load/store subkernels as simulated by RCM_brisc with       |     |

|            | the 4 cache models and as measured on an actual RS/6000                                   |     |

| Figure 24: | Execution times of each of the load/store subkernels as simulated by RCM_brisc with       |     |

|            | the 4 cache models and as measured on an actual RS/6000                                   | 40  |

| Figure 25: | The effect of varying the load miss latency on the number of stall cycles due to trailing |     |

|            | edge effects and the number of read delayed hits for the kernel loadtranstride4           |     |

| Figure 26: | The effect of varying the number of read ports and the cache-to-memory bus width on       |     |

|            | the number of stall cycles due to port conflicts for kernel loadtranstride2               | 51  |

| Figure 27: | The effect of varying the number of read ports and the cache-to-memory bus width on       |     |

|            | the number of stall cycles due to bus width considerations for kernel loadtranstride2 | 54   |

|------------|---------------------------------------------------------------------------------------|------|

| Figure 28: | The effect of varying the number of outstanding accesses allowable on the number of   |      |

|            | stall cycles due to a blocked cache for kernel loadtranstride4                        | . 56 |

| Figure 29: | LE simulation output for Livermore Loop Kernel 3                                      | . 59 |

## List of Tables

| Table 1: | Inputs used to configure the LE cache simulator                                      | 31  |

|----------|--------------------------------------------------------------------------------------|-----|

| Table 2: | Cache characteristics used to model the RS/6000 Model 320H                           | 37  |

| Table 3: | Comparison of relative execution times of each of the Livermore Loop Kernels as      |     |

|          | simulated by the four simulators vs. the actual execution times                      | 43  |

| Table 4: | Comparing the expected number of delayed hits with the actual number of delayed hits |     |

|          | seen from program simulation                                                         | .47 |

| Table 5: | Relative simulator run time for the LE and LE-nominal cache models over RCM_brisc    |     |

|          | alone                                                                                | 57  |

## Abstract

Cache performance is a key component of a microprocessor's overall performance, as it is the cache that buffers the high speed CPU from the much slower main memory. Behavioral cache simulators indicate the performance of a given cache configuration in terms of the number of hits and misses experienced when running a piece of code. One can attach a leading edge penalty or "effective" penalty estimate to each miss to get a first order idea of run time. However, individual timing penalties are not assessed within these models, nor are the various factors that can affect each memory access' latency. Our Latency Effects (LE) cache model accounts for additional latencies due to trailing edge effects, bus width considerations, the number of outstanding accesses allowable, and port limitations.

A tool implementing the LE cache model has been built on top of a behavioral cache simulator, DineroIII, in the spirit of the Resource Conflict Methodology developed by J-D Wellman. The tool was combined with Wellman's RCM\_brisc processor simulator to provide a realistic interaction of the cache with the processor (including the latency masking effects of processor activity) and to assess the accuracy of the model when simulating the execution of actual programs. The combined tool accurately mirrors the effects of changing a cache's configuration for a given processor configuration running a variety of programs. While the reported execution times do not exactly match the total execution times of the same programs running on actual hardware, the tool provides enough useful information to guide processor/cache designers early in the design cycle toward optimal configurations for target applications. This addition of cache modeling to the RCM\_brisc instruction-level processor simulator with perfect cache increases simulation time by only 17% (less than 5% over a constant miss penalty cache model), which is reasonable given the added benefits of using the LE cache model.

## **1.0** Introduction

Cache performance is a key component of a microprocessor's overall performance, as it is the cache that buffers the high speed CPU from the much slower main memory. Behavioral cache simulators indicate the performance of a given cache configuration in terms of the number of hits and misses experienced when running a piece of code. Timing penalties are not assessed within these models, giving a false perception of a cache's actual impact on a system. In a simple model, which can be applied to the behavioral simulator output, each miss is simply assigned a minimum (leading edge) penalty, or an effective (average) penalty. However, there are actually a variety of latency-adding effects that depend upon such things as which words within a cache block are accessed (upon and soon after a miss), the width of the busses between the CPU and cache and between the cache and next level of memory, the number of outstanding accesses the cache can sustain, and the number of available ports to the cache.

Detailed circuit level simulators (timers) do characterize these additional effects, but these simulators are specific to a given machine. As opposed to behavioral simulators, which sacrifice detail for configurability, circuit level simulators target a specific machine and simulate its actual operation. Typically, circuit level simulators can only be created after the cache design is near its final, detailed implementation. A simulator that achieves a compromise between behavioral simulators and timers would be very useful for assessing the benefits of using a particular cache configuration in a given processor. Such a simulator could be employed much earlier in the design cycle than a traditional timer and could run at comparable speeds, or much faster, while producing results that adequately reflect the execution of a given program running on actual hardware. Furthermore, it would retain the flexibility of a behavioral simulator, allowing many configurations to be evaluated in a reasonable time while producing a much more realistic performance assessment. If the tool adequately models a majority of the effects that would be seen in normal execution, the performance estimate should be quite accurate, helping designers to identify the changes that are needed to obtain high performance at a reasonable cost.

We have implemented such a configurable cache simulator that is more realistic, and thus more accurate, than a behavioral simulator, yet is more paramaterizeable than a machine-specific timer. The tool uses an experimentally developed Latency Effects (LE) cache model for a machine of interest and some parameterized extensions to determine the access latency for each memory access in a trace. The access latency depends not only upon whether the access is a hit or miss, but on its relationship to other accesses in process, the width of the memory busses, the number of outstanding accesses that the cache can sustain, and the number of ports to the cache. Specific latency-adding effects are derived from the experimental model as a function of the specific reference patterns in the trace.

As a first step in assessing the correctness of the LE cache model, the cache simulator has been combined with J-D Wellman's RCM\_brisc tool [Wellman95], which is based upon his Resource Conflict Methodology (detailed in Section 4.2). Together, the combined tool, RCM\_brisc+LE, simulates an RS/6000-like (POWER) microprocessor with cache. Our simulation results show that for memory stressing codes, the output of the resulting simulator, RCM\_brisc+LE, closely follows the trends seen by the same programs running on actual hardware. Furthermore, detailed analysis of those programs and the resulting output of the simulator show that the output corresponds closely to the results we would expect to see on a corresponding processor/cache configuration running those programs. In addition, a variety of useful statistics are provided by the new tool which serve to aid computer architects and programmers in the design and use of caches for target applications. These added benefits are provided with a maximum increase in simulation time of 17% over a processor-only simulator that assumes a perfect cache, and only 4.5% over a combined simulator that assumes a constant miss penalty.

Before we discuss the LE cache model and its implementation, we present an overview of caches and cache simulation in Sections 2.0 and 3.0, respectively. Then, the implementation of the LE cache model is presented in Section 4.0, followed in Section 5.0 by experimental results from the LE cache model implementation and an assessment of their accuracy. The cost of using the LE cache model is presented in Section 6.0, followed by a description of the simulator's output in Section 7.0. Conclusions are drawn in Section 8.0 and future work is discussed in Section 9.0.

## 2.0 Cache overview

A cache is a small, fast memory that is managed so that it contains recently accessed blocks of memory. The first level of the memory hierarchy encountered once the address leaves the CPU is generally a cache [Hennessy96]. The use of caches is based on the principle of locality, which says that most programs do not access all code or data uniformly. Instead, code or data is accessed in groups (spatial locality) or it is accessed repeatedly in a short period of time (temporal locality). To make use of locality, this small, fast memory is placed between the CPU and the slower, larger next level of memory. In general, several levels of cache may be used and separate caches at the same level may be used for instructions and data. The level of hierarchy targeted in this paper is the first level of data cache, known as the L1 data cache.

The L1 data cache (herein referred to simply as cache) is the smallest, fastest memory that the CPU can access. It can service memory requests at or near the CPU's execution frequency, but may incur longer latencies when requested information is not present in the cache. When an access is made to data not already allocated in the cache, the data must be obtained from the next level of the memory hierarchy. This process is called servicing a cache miss, and usually takes many more cycles to satisfy than a cache hit. Requests that reference data that is allocated in the cache return the desired data in less time than the full miss latency and are called hits to the cache. As we will see in Section 2.2, there are actually several types of hits with various access delays that they may suffer; for Section 2.1, the simple concept that a hit returns data immediately to the CPU will suffice.

#### 2.1 Components of cache design

There are many well-known components to cache design. The cache is broken into chunks called blocks (also referred to as lines). A block is a collection of contiguous data that is treated as a single entity of cache storage. Blocks often consist of multiple words, with the typical word size being 32 or 64 bits for today's microprocessors. Larger blocks (e.g. blocks consisting of a greater number of words) take more advantage of spatial locality, as more data close to recently accessed data is stored in

#### Early Design Cycle Timing Simulation of Caches

the cache within one atomic cache allocation unit. However, blocks that are too large sacrifice temporal locality, as having larger blocks for a fixed size cache reduces the number of different blocks that can be stored in the cache at once. Furthermore, using larger blocks can increase the miss latency, as a greater number of cycles may be required to fill a cache block with data from the next level of memory for a fixed size cache-to-memory bus. Larger blocks can also increase cache pollution because superfluous data may be brought into the cache within the referenced blocks. Blocks that are too small sacrifice spatial locality, as data close to, but not in the same block as recently requested data already present in the cache may have to be fetched from the next level of memory when it is requested. Typically, block sizes in today's caches range from 32 to 128 bytes.

Each block maps into a single set in the cache. A set is a group of blocks in the cache; in a kway associative cache, a set can simultaneously hold any k of the blocks that map to it. Higher associativity provides more flexibility as to which blocks may simultaneously reside in a fixed size cache, and hence generally results in a higher hit ratio (the fraction of memory accesses found in the cache). However, increasing the associativity of a cache increases the number of tags that must be checked to see if the referenced data is in the cache. Thus, the time to access requested data in a highly associative cache grows due to the increased time required to perform and resolve the increased number of comparisons within a set to find the desired data. Due to its faster access and simpler implementation, the associativity of caches is kept low in most cache designs. Typically, today's caches are direct mapped, two-, or four-way set associative.

Every time memory is accessed, a check must be made to see if the referenced data is in the cache. If the data is in the cache, the reference is a cache hit, and the data is returned directly from the cache. If the desired data is not in the cache, the reference is a miss and the transaction must access a higher level of the memory hierarchy. In detail, a miss may be handled in different ways, depending upon the configuration and management policies of the cache and whether the access is a read or a write.

When a read miss occurs, a block in the cache is replaced with the desired data. There are several methods to determine which block should be replaced (Least Recently Used, random, and optimal, among others) [Hennessy96]. Some approximation of the LRU replacement algorithm is usually used in today's caches. Random replacement is sometimes used in large caches to reduce the

implementation cost. Our simulations assume LRU replacement, but other strategies can be selected. The optimal algorithm may be used to determine an upper bound on cache performance; however, it is not implementable as it requires knowledge of the future in order to make its replacement decisions.

For all write accesses, be they hits or misses, the next level of memory must eventually be updated with the new changes. Two write policies are commonly used: write through and write back. In the write through policy, the information written to the cache is written to the next level of memory at the same time or soon thereafter. In write back, the information is initially written only to the cache; the modified cache block is written to the next level of memory only when it is replaced. For uniprocessors, the write back policy is normally used. In many cases, the data in a block may be changed multiple times before the block is replaced and then written out to the next level of memory. By delaying the update, multiple writes to a block can be grouped into one update, which generally results in higher performance.

When a write miss occurs, the referenced block need not be loaded into the cache. In write allocate caches, the block is loaded on a write miss; a block replacement process similar to that for read misses is then used, followed by the update of the block in the cache. In no-write allocate caches, however, the referenced block is modified directly in the next level of memory and is not loaded into the cache. Write back caches generally use write allocate, hoping that subsequent writes to that block will be captured by the cache. Write through caches often use no-write allocate, since subsequent writes to that block will still have to go to memory.

The width of the busses between the CPU and cache and between the cache and the next level of memory can affect the latencies of the memory accesses. Most accesses are word-sized, a word typically being 32 or 64 bits (4 or 8 bytes) in size. The busses between the levels of the memory hierarchy are usually some multiple of the word size, though they are rarely as wide as the size of an entire cache block. As a result, portions of the block, called subblocks, are filled on consecutive bus cycles by data returning from the next level of memory when satisfying a cache miss. For instance, if the cache-to-next-level-of-memory bus width is 1/4 of the size of a block, it will take four bus cycles to fill the entire cache block. The subblock containing the desired word is normally returned first; in this case, the block starts "filling" at the desired subblock and wraps around to the beginning of the block to

complete the block fill. While this minimizes the time to access the desired (missing) word, the other words in the cache block must wait additional cycles before they are present in the cache; this additional wait can adversely affect the latency of future memory accesses, as we will see in Section 3.2.

Since the advent of pipelining, multiple memory accesses are often in flight at once. In a blocking cache, an access that follows a miss must wait to begin execution until the miss completes its access. A cache allowing hit-under-miss, on the other hand, would allow hits to complete while a miss is outstanding; a new miss would still have to wait until the earlier miss completes. A cache capable of sustaining more than one outstanding miss is called a non-blocking cache. The number of allowable outstanding accesses is defined as the maximum number of uncompleted misses that the cache can support while still allowing new memory requests to begin execution. Once this threshold is crossed, all future accesses, be they hits or misses, must wait until at least one of the outstanding misses completes before they can begin execution.

The number of ports to the cache also affects cache performance. A port is a point of access to the cache – it can either be a read port, write port, or both. Transactions can take place only when a port of the desired transaction type is available. If a read (load) is requested and no read ports are available, the access must wait until a read port becomes free; in most cases, the port becomes free the very next cycle, as a port is normally used for only one cycle per transaction. However, if a transaction uses the port for multiple cycles or there are older (pending) accesses waiting to use the desired port, the new access may have to wait additional cycles to obtain the use of the port. Increasing the number of ports to the cache can alleviate this problem, though this approach is usually avoided due to its high cost. Today's caches often have two ports so that potentially two accesses can be completed in each cycle.

#### 2.2 Terminology

In this section, we review some of the terminology that will be used throughout this paper:

Cache hit –

an access to the cache that requests data that is presently in the cache. For reads, the desired data is returned in CACHE\_HIT\_LATENCY cycles.

- Latency-adding effects effects a memory access may experience that add to its nominal execution time, e.g. trailing edge effects, bus width considerations, the number of outstanding accesses allowable, and port limitations.

- Delayed hit –

a hit that experiences latency-adding effects. These are called hits because they do not incur the full read or write miss latency; furthermore, they do not generate any additional miss traffic.

- Miss –

an access to the cache that incurs the full read or write miss latency. (Misses are further categorized below).

- Cold-start miss a miss access to the cache that occurs because the block that contains the desired data has never been accessed before. Also known as a compulsory miss.

- Capacity miss –a miss access to the cache that is not a cold-start miss, but occurs because the<br/>entire working set of the program cannot simultaneously reside in the cache.<br/>The number of capacity plus cold-start misses is the total number of misses<br/>that would occur in a fully associative cache of the same size and block size<br/>with optimal replacement.

- *Conflict miss* all other miss accesses to the cache, which occur because more than k blocks of the working set map to the same set of a k-way associative cache, and additional misses that may be due to the nonoptimality of the replacement policy, thereby causing some data to be replaced during execution.

- Read miss latency the nominal time to satisfy a read (load) request that misses in the cache, e.g. the time to return the desired data from the next level of memory to the cache under ideal circumstances.

*Write miss latency* – the same as read miss latency, except for write (store) requests.

## **3.0** Overview of cache simulation

Cache simulation is widely used to determine the performance of a given cache configuration for the execution of a target application. This evaluation can be done using behavioral cache simulators, circuit level simulators (timers), and via the measurement of actual systems (using hardware monitors). Behavioral cache simulators are highly paramaterizeable, but they do not represent the access latencies of a target machine accurately. Circuit level simulators, on the other hand, are extremely accurate for a single machine, but are not paramaterized to evaluate a variety of dissimilar machine implementations. Finally, the measurement of an actual system, while useful in gauging performance, requires a completely implemented, fully operational system, and even then may not give designers or programmers a good idea of the underlying causes of the measured performance. The Latency Effects (LE) cache model and its implementation improves upon these techniques by incorporating more of the effects that a memory access can experience than a behavioral cache simulation run. Furthermore, the statistics output by the LE tool aid the designers and programmers in determining the bottlenecks and underutilized resources of the configuration.

## 3.1 Currently available behavioral cache simulators

Many behavioral cache simulators are currently available, including DineroIII [Hill85], ACS [PARL95], Fast-Cache [Lebeck95], and others. These simulators take cache design parameters, such as cache size, block size, and associativity, together with a sequence of memory accesses as input and determine the number of cache hits and misses that would occur if the code were run on a processor with a cache of the corresponding parameters. Each memory access is analyzed individually, and its result (whether it is a hit or miss to the cache) is dependent upon the state of the cache at the time of the access. The job of the simulator is thus to maintain the cache state and decide whether each successive reference is a hit or a miss. After each access is evaluated, its effect on the cache is immediate, e.g. if a

block of data is loaded into the cache by one access, all of that data is considered to be present and immediately accessible in the cache when the very next access arrives.

#### **3.2** The LE cache model

While knowledge of the number of cache hits and misses is useful, knowing the effects of those hits and misses on a program's execution is essential for guiding the design process. One way to add this functionality to existing cache simulators is to attach a latency to each access. This addition enables us to determine the number of cycles required to execute a given sequence of memory accesses.

However, this approach assumes that all memory accesses are independent and decoupled, i.e. once the earlier access to the cache line is evaluated, the requested data is immediately present in the cache until it is replaced. In actuality, if an earlier access has not fully completed before a new access to the same cache line occurs, a trailing edge effect may be seen. The new access to the cache line will then require more than CACHE\_HIT\_LATENCY cycles to complete because the referenced data, although allocated, is not yet actually present in the cache yet. However, since an earlier access to the cache line is already in flight, this new access will not incur the full read or write miss penalty. Furthermore, performing this new access to the cache line does not generate any additional miss traffic, as the desired data is already in transit from the next level of memory to satisfy the earlier request. Current general simulators do not address trailing edge effects, as they assume that after an access is made to a cache line, all subsequent accesses to that line are cache hits (until the line is replaced). We call such a reference that experiences trailing edge effects (and other hits that experience other latency-adding effects) a *delayed hit*. Thus we divide accesses into cache hits, delayed hits, and misses.

Trailing edge effects can have an enormous effect on a program's actual execution time. The greatest impact is made when there is a series of memory accesses as in Program 1:

1 LDF A 2 LDF B 3 LDF C 4 LDF D Figure 1: Program 1 Suppose that the data in memory is laid out as follows:

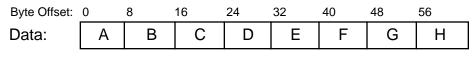

Figure 2: One block-aligned portion of memory (blocksize = 64B)

For simplicity, suppose that access requests are sent to the cache in the first Execute stage of the processor pipeline and that loads complete in the same cycle that the data returns from the cache. Assuming that the access to address A is the first access to that cache line, the LDF (floating-point load) at line 1 will always miss (it is a cold-start miss). In a cache with a block size of 64 bytes, the three subsequent LDFs will be recorded as hits to the cache in a cache simulator such as DineroIII, since each load requests 8 bytes of data and all the desired data is in the same block. This situation is shown below in Figure 3:

Cy IX-----W 1) A 2) BA---->A (miss) 3) CB---->B (hit) 4) DC---->C (hit) 5) D----->D (hit)

## Figure 3: Execution behavior of Program 1 according to unmodified DineroIII

In the figure above, Cy indicates the cycle number, I indicates the issue stage of the pipeline, X shows the start of the execution phase, and W is the writeback stage.<sup>1</sup> Without any modification, DineroIII would indicate that all the accesses complete in the same cycle that they begin execution, regardless of whether they hit or miss. The information about whether the access actually hits or misses in the cache is recorded for statistical purposes. If DineroIII were used to model memory accesses in conjunction with a processor simulator, all Execute and Writeback stages for these loads would be merged into one cycle, and this sequence of instructions would require five cycles to execute.

<sup>&</sup>lt;sup>1</sup> The target machine in this example is a uniprocessor with a single load/store execution unit that can handle one memory request per cycle. This machine model will be used throughout this study to simplify the analysis; the following examples can easily be extended to execute on a machine allowing multiple memory accesses per cycle.

The first step to improving this model would be to add leading edge latencies to each memory access. These latencies would describe the time that the access spends in the Execution and Writeback stages of the pipeline, with the Writeback stage usually requiring a single cycle. For instance, the access latency for a load miss could be 10 cycles (9 cycles for Execute and 1 cycle for Writeback), whereas a load hit would only require 2 cycles (1 cycle each for Execute and Writeback). The simulation of Program 1 with DineroIII augmented with these latencies is shown in Figure 4.

| <u>Cy</u> | <u>IX-</u> |   |   | <u>-W</u> |

|-----------|------------|---|---|-----------|

| 1)        | А          |   |   |           |

| 2)        | ΒA         |   |   |           |

| 3)        | CBA        |   |   |           |

| 4)        | DC         | A |   | В         |

| 5)        | D          | А |   | С         |

| 6)        |            | А |   | D         |

| 7)        |            | P | 1 |           |

| 8)        |            |   | А |           |

| 9)        |            |   | А |           |

| 10        | )          |   | I | ł         |

| 11        | )          |   |   | А         |

Figure 4: Execution behavior of Program 1 for leading edge latency-augmented DineroIII

Here, the program execution is more realistic in terms of overall execution latency (11 cycles total). However, the accesses to B, C, and D cannot complete before the access to A, since A, B, C, and D all reside in the same block of memory and the earliest datum to return to the cache is A! At the earliest, the accesses to B, C, and D can return to the processor in cycle 11 along with the access to A; completing any earlier would not be possible because the data would not be in the cache yet!

As introduced earlier, the accesses to B, C, and D suffer from trailing edge effects caused by A: since the block brought in by the access to A is not available when B, C, or D execute, and since all four accesses reside in the same cache block, B, C, and D must wait additional cycles to complete. If trailing edge effects were incorporated into the cache model, the execution of Program 1 would look like:

| <u>Су</u> | IXWbck |

|-----------|--------|

| 1)        | A      |

| 2)        | BA     |

| 3)        | CBA    |

| 4)        | DCBA   |

| 5)        | DCBA   |

| 6)        | DCBA   |

| 7)        | DCBA   |

| 8)        | DCBA   |

| 9)        | DCBA   |

| 10)       | DCBA   |

| 11)       | ABCD   |

Figure 5: Execution of Program 1 when trailing edge effects are taken into account and 4 read ports are available

Here, we see that all four accesses complete in cycle 11. This makes sense because it is possible that all the data in the cache line is available at cycle 11 and the data can be returned to the desired functional units in the same cycle (e.g. there are four available read ports to the cache for that cycle). The time to wait for the desired data is represented in the additional stages of Execute that those accesses must experience. As shown in Figure 5, the Execute and Writeback stages represent the miss pipeline in the cache subsystem. Different machines may handle the actual misses in this pipeline differently, but the end result is the same: the desired data is not available until the required latency has passed. Thus, this representation of the access' execution shall suffice for understanding the movement of different memory accesses through the cache subsystem.

The accesses to B, C, and D are all delayed hits, since they do not incur the full miss latency, yet they do not complete in the time required for a cache hit. Also, these accesses do not generate any additional miss traffic, as the required data is already in transit to satisfy the earlier request to A.

While a machine could be built to load an entire cache block in one bus cycle, it is likely that the cache block is loaded from main memory in multiple bus cycles (e.g. one word per cycle, with the requested word returning from memory first). Thus, in addition to trailing edge effects, a memory access can experience increased execution times due to bus width considerations. If successive data words of the block are returned to the cache in successive cycles, the program execution would look like:

| <u>Cy</u> | <u>IXW</u> |

|-----------|------------|

| 1)        | A          |

| 2)        | BA         |

| 3)        | CBA        |

| 4)        | DCBA       |

| 5)        | DCBA       |

| 6)        | DCBA       |

| 7)        | DCBA       |

| 8)        | DCBA       |

| 9)        | DCBA       |

| 10)       | DCBA       |

| 11)       | DCBA       |

| 12)       | DCB        |

| 13)       | DC         |

| 14)       | D          |

## Figure 6: Execution of Program 1 with words from memory returning in sequential cycles or with only 1 read port to the cache

There may also be port limitations that affect an access' latency – in the program execution of Figure 5, four read ports from the cache are assumed to be available at once. Typically, processors today have one read/write port to the cache; some have more than one port and in such cases, some ports may be read-only or write-only. If the target processor has one read port to the cache, regardless of whether data is returned from memory simultaneously or sequentially, Program 1 would execute as shown in Figure 6, above. Since there is only one read port, only one of the words can be returned to the processor from the cache in each cycle. In this example, subsequent requests must wait for earlier ones to complete before a port is freed and the desired word can be transferred from the cache to the processor.

Words in memory are often accessed nonsequentially. For instance, if we run Program 2 with the memory layout shown in Figure 8,

> 1 LDF I 2 LDF J 3 LDF K 4 LDF L Figure 7: Program 2

| Byte Offset: | 0 | 8 | 16 | 24 | 32 | 40 | 48 | 56 |

|--------------|---|---|----|----|----|----|----|----|

| Data:        | I | K | L  | J  | М  | N  | 0  | Р  |

Figure 8: Another block-aligned portion of memory (blocksize = 64B)

the program's execution might look like:

| <u>Cy</u> | <u> </u> |

|-----------|----------|

| 1)        | I        |

| 2)        | JI       |

| 3)        | KJI      |

| 4)        | LKJI     |

| 5)        | LKJI     |

| 6)        | LKJI     |

| 7)        | LKJI     |

| 8)        | LKJI     |

| 9)        | LKJI     |

| 10)       | LKJI     |

| 11)       | LKJI     |

| 12)       | LJK      |

| 13)       | JL       |

| 14)       | J        |

## Figure 9: Execution of Program 2 with words returning from memory in sequential cycles

While the overall program execution time remains the same as Program 1's execution time (14 cycles), the desired data returns in a different order; this is entirely a function of the location of the requested words of data in memory. For Program 1, the data returned in the order it was requested. In Program 2, the data returned in the order that the data was retrieved from memory (first I, then K, L, and J). Typically, caches fill their blocks from the next level of memory in the order that the data is found in memory, not the order the data is requested. Thus, instead of returning one cycle after I, the access to J returns three cycles after I returns since it is the last word of the four in the block to be returned when word I is requested first. The increased latency required to complete the access to J is shown by the increased time that J spends in the Execute stage; the accesses to I, K, and L complete as their desired data is loaded into the cache block. This effect is not very apparent in a simple program consisting of only memory accesses; however, if there were a fixed- or floating-point operation that depended upon the data at address J, that dependent instruction would have to wait three additional cycles: one cycle

due to the cache being unable to load the entire cache block in one cycle and two more cycles due to the placement of J within memory.

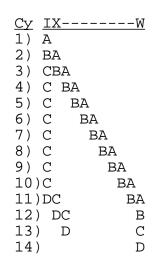

There is one more effect that we must consider. Most caches cannot continue accepting requests if there are a number of misses that have yet to be satisfied (these misses are termed "outstanding accesses"). Once the threshold of outstanding accesses is reached, subsequent accesses may be delayed until the earlier accesses complete; until at least on of these outstanding accesses completes, the cache is said to be *blocked*. If Program 1 were run on a processor whose cache could only sustain two outstanding accesses at a time, its program execution would look like:

Figure 10: Execution of Program 1 on a processor whose cache can only sustain two outstanding accesses at a time with 1 read port to the cache

Since neither A nor B are complete when C tries to enter the Execute stage, C must wait because the cache is blocked. C does not enter Execute until the first outstanding access, A, exits Execute in cycle 11. Since C was blocked in the Issue stage, D does not get to enter Issue until C exits that stage. (In more complex processor configurations, C and D would be blocked together in a processor buffer somewhere outside of the Execute stage).

Once C enters Execute, it finds that the data it wants is already in the cache, thanks to the earlier miss to the block by A. Thus, C finishes one cycle after B (due to port conflicts) and D completes one cycle after that. Since all the accesses were to the same block of the cache, the blocked cache does not adversely affect the execution time of Program 1, as its execution time remains 14 cycles.

If we were to execute Program 3 on the same (two outstanding accesses sustainable) processor and cache with the memory layouts shown in Figures 2 and 8, the program execution would look different:

> 1 LDF A 2 LDF B 3 LDF I 4 LDF K

## Figure 11: Program 3

| <u>Cy</u><br>1)<br>2)<br>3)<br>4) | <u>IX</u><br>A<br>BA<br>IBA<br>I BA | -        | <u>W</u> |

|-----------------------------------|-------------------------------------|----------|----------|

| 5)<br>6)                          | I E<br>I                            | BA<br>BA |          |

| 7)                                | I                                   | BA       |          |

| 8)                                | I                                   | BA       |          |

| 9)                                | I                                   | B.       |          |

| 10)                               |                                     |          | BA       |

|                                   | KI                                  |          | BA       |

| 12)                               |                                     |          | В        |

| 13)                               |                                     | -        |          |

| 14)                               | ) K                                 | II       |          |

| 15)                               | )                                   | KI       |          |

| 16)                               | )                                   | KI       |          |

| 17)                               | )                                   | KI       |          |

| 18)                               | )                                   | K        | I        |

| 19)                               | )                                   |          | KI       |

| 20)                               | )                                   |          | KI       |

| 21)                               | )                                   |          | K        |

Figure 12: Execution of Program 3 on a processor whose cache can only sustain two outstanding accesses at a time

In Program 3, the misses to A and I are to different blocks in the cache. I must wait until A completes before it enters execute, since A and B are outstanding when I enters the issue stage. But, once I enters execute, it finds that it, too, is a miss, and must wait 10 cycles before completion. K, being a trailing edge access to the same block as I, must wait 10 cycles to complete as well. Thus, Program 3 requires 21 cycles to execute, as opposed to 14 cycles for Program 2 running on a similar machine.

The Latency Effects (LE) cache model accounts for the nominal hit and miss times, plus the added delays due to each of the aforementioned effects of prior accesses on the timing of the next access

(trailing edge effects, bus width and port limitations, and the number of outstanding accesses allowable). By using the LE cache model instead of a currently available behavioral cache simulator like DineroIII, a more accurate simulation of the execution of memory accessing instructions can be obtained.

## 4.0 Implementing the LE cache model

In order to test the correctness of the LE cache model, a cache simulator incorporating this model was built. Instead of writing a basic cache simulator from scratch, DineroIII was used as a basis, as it is a widely-used and highly paramaterizeable behavioral cache simulator. While there are many ways that the delays associated with the LE cache model can be realized, an approach based on the Resource Conflict Methodology was used. DineroIII and the Resource Conflict Methodology are described in the next two sections, followed by the implementation of the LE cache model.

## 4.1 DineroIII

DineroIII [Hill85] is a parameterizeable, trace-driven cache simulator developed by Mark Hill. DineroIII takes a trace of memory accesses as input and determines, for each access, whether the access hits or misses based on the state of the cache at the time of the access. The cache that is simulated can be modified based on associativity, cache block size, overall cache size, and update policy, among other parameters. Statistics reported at the end of the simulation include the number of read and write hits and misses to the cache, the number of words transferred, and the total number of memory accesses.

## 4.2 Resource Conflict Methodology

The Resource Conflict Methodology (RCM) [Wellman95] was proposed by J-D Wellman as a technique for modeling and simulating computer systems early in the design cycle. Each element of the simulated processor is viewed as a resource that may be unavailable at a given time. For instance, an RCM model analyzes the effect of each instruction's execution on a given machine's resources. Each

instruction requires a certain set of resources to execute. As the instructions are executed, the availability of each resource that is used is updated, delaying the times at which those resources are available to subsequent instructions. Given the resource constraints, the execution time of a program can thus be determined by keeping track of when instructions are allowed to execute and when they complete.

### 4.3 Implementing LE on top of DineroIII

DineroIII keeps the current state of the cache in memory during simulation. The cache is "updated" when each new access is made: If the access is a hit, the data is already in the cache, but it may be marked to reflect that it is the most recently accessed datum (for a replacement policy such as LRU). If the access is a miss, any block replacement that is required is performed and the desired data is placed in the cache immediately. Any subsequent accesses to that data block (until it is replaced) are thus recorded as hits, since according to DineroIII's cache state, the data for that block is in the cache.

However, due to leading and trailing edge effects, data does not return to the cache from the next level of memory immediately. These effects can easily be incorporated into DineroIII by controlling when DineroIII's state is updated, i.e. when DineroIII "sees" a memory access. Given the cycle in which the access begins execution, we can determine the effects that it sees during execution and when it completes – and thus when DineroIII's state should be updated.

Each memory access is evaluated in turn, since we assume only a single memory access is permitted per cycle.<sup>2</sup> First, the DineroIII cache is checked to determine whether the access is a hit or a miss. If DineroIII says that the access is to data currently in the cache, the access is tentatively marked a cache hit. This access must wait CACHE\_HIT\_LATENCY cycles before the data is available for the requesting functional unit. Usually, data is returned in same cycle that it is requested when a cache hit occurs, so the CACHE\_HIT\_LATENCY is normally equal to one. Thus, the cache hit completes in the same

<sup>&</sup>lt;sup>2</sup> The single memory access per cycle limitation is due to the target machine we chose to emulate in this study. However, due to its implementation based on the RCM model, the LE cache model can inherently handle multiple accesses per cycle.

cycle in which it begins execution and the data is available for use in the processor in the very next cycle.

If an access is tentatively marked as a hit and a dependency of the second type is found (e.g. the requested data will be replaced by a currently outstanding miss access), the access is then handled as a cache miss, as explained in Section 4.4.5. If no dependencies are found, the access is indeed a cache hit, and the DineroIII cache state is updated to reflect that that block is the most recently accessed reference.

If an access is tentatively marked a cache miss, the access is not necessarily a miss that would incur the full read or write miss latency. The access may be a delayed hit, as an outstanding miss access may already have requested the desired block. Thus, a check is made to see if the new access is dependent on any currently outstanding accesses. If the access does depend on a currently outstanding access, the access is a delayed hit, which to DineroIII seems like a miss, as the desired data is not present in DineroIII's cache due to the delayed update that we have imposed on the DineroIII cache state. However, since the desired block is already in transit from the next level of memory (due to the earlier dependent miss to that block), the new access should not automatically incur the full read or write miss latency. This is the beginning of the implementation of the LE cache model outside of DineroIII.

Once the access has been completely evaluated by the LE cache model, the completion cycle for that access is known. The effects of the access on the state of the DineroIII cache are enacted (i.e. the cache is updated) when the cycle of the simulation is greater than or equal to the completion cycle of the access. The update of the DineroIII cache state is deferred for each access until the data is actually resident in the cache. This way, if an access is determined to be resident in the DineroIII cache state at any given time, the data will be available immediately (except in the case where a dependency of the second type is discovered) as a cache hit; otherwise, the access is a delayed hit or cache miss. The updating of the DineroIII cache state will be explained in greater detail in Section 4.4.5.

## 4.4 The LE cache model outside of DineroIII

As discussed in Section 3.2, there are four main sources of additional delay for a memory access:

- Trailing edge effects

- Bus width considerations

- Number of allowable outstanding accesses

- Port limitations

Each one of these effects potentially affects the completion time of an access to the cache (and the subsequent access to the next level of memory for cache misses). Each effect and its implementation is now discussed in turn.

## 4.4.1 Trailing edge effects

In order to quantify the trailing edge effects experienced by a cache access, the status of each outstanding access to the cache must be retained. Cache hits, on the other hand, can be evaluated as they occur, as they can only be affected by previous instructions. A cache hit can only be affected by prior delayed hits or misses because of its port requirements (discussed in Section 4.4.4). For instance, if a cache hit is issued in cycle X, it will complete in two cycles (using the example latencies from Section 3.2), i.e. in cycle X+2. For our model machine, the earliest time that a new memory accessing instruction can be issued is in the very next cycle, cycle X+1. If the new access is also a cache hit, it will complete in cycle X+3, and will not depend in any way on the earlier cache hit. If the new access is a delayed hit or a miss, the access will complete in cycle X+N, where  $N \ge 4$ . However, the first cache hit will complete. As a result, the cache hit will not be affected by any accesses that issue after the cache hit is issued, regardless of the outcome of the subsequent accesses. However, we will see in Section 4.4.4 that cache hits can be affected by prior delayed hits or misses whose latencies are greater than the latency of a cache hit.

Misses can affect the completion times of many subsequent accesses. The number of future accesses affected increases in proportion to the duration of the full miss latency. To determine these effects, the status of a cache miss is kept until the access is satisfied, i.e. until the requested data is

#### Early Design Cycle Timing Simulation of Caches

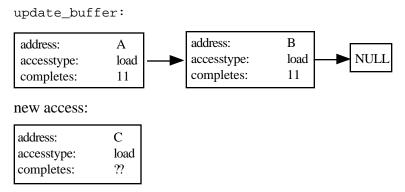

finally resident in the cache. All outstanding accesses are ordered chronologically in a linked list called the update\_buffer. When an instruction accesses data not currently in the cache, the update\_buffer is checked to see whether the desired data is currently in transit from the next level of memory to the cache. A *dependency* is found if one of two situations occur: 1) the desired data coincides with a cache block that is currently being brought into the cache from the next level of memory or 2) the desired data is currently being replaced by an outstanding access. For dependencies of the first type, instead of incurring the full miss latency of the cache, the new access will be satisfied in some shorter period of time related to the remaining time to satisfy the earlier outstanding access to the same cache block. Dependencies of the second type will require the nominal miss latency for that access type to complete, as the desired data will need to be fetched from the next level of memory to satisfy the access. As we will see in subsequent sections, this is only the first part of determining the completion time of a delayed hit or miss; once the earliest time to completion is determined (when the earlier conflicting miss completes), bus width considerations, the number of allowable outstanding accesses, and port conflicts must be taken into account. These will be discussed in detail in Sections 4.4.2, 4.4.3, and 4.4.4, respectively.

The update\_buffer corresponding to the execution of Program 1 at cycle 4 is shown in Figure 13. At this point in time, the access to C is beginning execution. We see that the first entry in the update\_buffer linked list is the load from address A. The next entry in the linked list, which corresponds to the next outstanding access to complete, is the load from address B.

Figure 13: State of update\_buffer when the access to address C is being evaluated

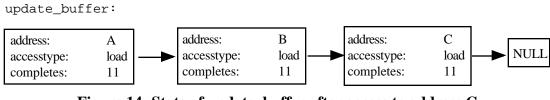

The load from address C will check the update\_buffer and find that its desired data will be present in the cache at cycle 11, thanks to the earlier request to that cache block by the access to A. Since it is only cycle 4, this access will also be placed in the update\_buffer, as it will complete in a later cycle and may affect the access time of a future memory accessing instruction. Assuming there are enough ports to satisfy three read requests from the cache in one cycle and the bus between the cache and the next level of memory is wide enough to return all three access to the cache in the same cycle, the load from address C will also complete in cycle 11. The updated update\_buffer is shown in Figure 14.

Figure 14: State of update\_buffer after access to address C has been evaluated

Every delayed hit and miss goes through this process and eventually ends up in the update\_buffer. If the access is a miss, i.e. the desired cache block is not present in the DineroIII cache state, no dependencies will be found with the entries currently in the update\_buffer. Dependencies of the second type cause hits or delayed hits to become misses, as the desired data will be replaced by an outstanding access. These accesses will incur the full miss latency for its type (read or write), plus any additional cycles due to port conflicts (see Section 4.4.4). An entry is made for the new access and it is placed in the update\_buffer so that future accesses can check against this new outstanding access as well.

By assigning differing latencies for each access depending upon its time of execution, we can more accurately predict the time to execute a series of memory access instructions. Using its first cycle of execution as the starting point for each access, the completion time for that memory access can be determined by looking at the outstanding accesses to the cache, combined with the knowledge of the read and write miss latencies for the given cache. Using varying latencies is the first step toward a more realistic cache performance estimate.

#### 4.4.2 Bus width issues

Another parameter that affects when an access completes is the bus width between the cache and the next level of memory. The data bus of a port between the CPU and the cache is normally at least the width of one access (typically a 32-bit word or a 64-bit doubleword), so requests will complete without being affected by this bus width. However, the bus width between the cache and the next level of memory is normally smaller than the block size of the cache. For instance, in the RS/6000 Model 320H [Hardell90], the block size is 64 bytes, but the cache-to-memory bus is only 8 bytes wide, causing a block of data to return to the cache in multiple cycles.

Typically, machines are designed to return the requested word within the cache block first, with subsequent subblocks (a subblock being the width of the cache-to-memory bus) arriving in subsequent cycles to the cache. The other alternative is to always return the first subblock of the block first, forcing all but the first subblock in the block to wait additional cycles for a miss access to them to be satisfied. Since most of today's machines use the former technique, the following discussion will concentrate on that method; the analysis can easily be modified to use the second cache fill policy.

Given the requested-word-first cache fill policy, the first miss to a cache block will take the required full read or write latency to complete. A subsequent miss to the same cache block that occurs while the earlier miss is in flight may or may not be satisfied in the same cycle as the earlier miss. If the subsequent miss is to the same subblock as the earlier miss, both accesses will complete in the same cycle (ignoring port conflicts for now). If the subsequent miss is to a different subblock, that access will have to wait additional cycles to be satisfied. Since the cache block is filled in a wrap-around fashion, the later access will have to wait at most an additional [(block size in bytes)/(cache-to-memory bus width in bytes) - 1] cycles to complete. If the later access is in the subblock to return immediately after the first requested subblock, the later access will complete one cycle later than the earlier access, pending port conflicts. If the later access returns in the third subblock, it will wait two additional cycles, etc. An example of bus width issues affecting memory access latencies was shown in Figure 9 with the execution of Program 2.

Given a cache's block size and cache-to-memory bus width, we can easily determine these additional delays given when the accesses occur relative to one another. The additional cycles are simply added on to the completion cycle that was determined for this access in the initial trailing edge analysis. These additional cycles will not and should not affect any earlier access' completion times, but will affect the completion times of the current and future accesses. The completion cycle of the access is stored in the access' update\_buffer entry so that future accesses can determine when this outstanding access completes.

#### 4.4.3 Number of outstanding accesses

The number of outstanding accesses that a cache can sustain affects the completion time of any memory access. Caches that do not support hit-under-miss will stall whenever there is a miss in the cache. This means that any subsequent memory accesses, even if they were to access data that was present in the cache at that time, would be stalled until the outstanding access completed. Obviously, future misses to currently absent data would also be stalled, though the delay due to the blocked cache would likely remove some of the trailing edge effects. (For an example of this situation, see Figure 10, which shows delayed hits turning into cache hits due to the blocked cache). When the cache becomes unblocked, the first waiting access begins execution. Since there are no outstanding accesses when this new access executes, it will not experience any latency adjustments due to trailing edge effects. While this case is handled by the LE model, the cache is blocked was shown earlier in Figure 12 with the execution of Program 3.

There can be a varying "number of outstanding accesses" (NOA) when hit-under-miss is allowed. If hits are allowed when only one miss is outstanding, the NOA is equal to one. This means that we can have one miss access to the cache outstanding at a time, but we can still service hits to the cache. If another miss occurs while an earlier miss access is outstanding, the processor stalls all memory accesses until the earlier miss is satisfied. After the first miss is completed, there is once again only one miss access outstanding, and hits can once again be handled if they occur. Increasing the NOA increases the number of memory accesses that can be in flight at one time, giving a corresponding increase in the number of accesses that could potentially be affected by trailing edge effects. Still, once the threshold is crossed, all accesses, be they hits or misses, must wait until at least one earlier miss is satisfied before they can execute.

To account for NOA, we simply need to check to see how many misses are outstanding when we evaluate a new memory access miss. If the number of outstanding misses is less than the NOA threshold, the current access' completion time is wholly dependent upon trailing edge effects, bus width effects, and port limitations. If the number of outstanding accesses is greater than the NOA threshold, this access must wait until enough misses are satisfied to reduce the number of outstanding accesses to less than the NOA threshold. If the new access depends on an outstanding access, the new access will complete CACHE\_HIT\_LATENCY cycles after it is allowed to execute, as the data would be in the cache by the time the request is actually made to the cache. If the new access does not depend on any outstanding access and is simply delayed due to the blocked cache, the normal trailing edge and bus width effects analysis will be applied, once the cache is no longer blocked and the access is allowed to begin execution.

If the new access is a miss, the new access would have to incur the full miss latency before it would complete. This latency would be added on to the cycle that the access was finally determined to execute to determine its completion time. As above, the new access would execute when enough misses are satisfied to reduce the number of outstanding accesses to less than the NOA threshold.

## 4.4.4 Port limitations

The final element to consider when determining an access' completion time is the availability of an appropriate port to the cache. After the completion cycle of an access is determined by considering trailing edge and bus width effects, and the number of outstanding accesses, we must check to see if the desired port for the transaction (read or write) is available in the desired completion cycle. If an appropriate port is available, the completion cycle remains unchanged and we have found the actual completion time of the access. If an appropriate port is not available, we must check subsequent cycles to see when an appropriate port does become available. This is done by scanning through subsequent cycle times, starting at the access' completion cycle + 1. The search is continued until an appropriate port is found and that cycle count is returned as the actual completion time. Thus, the access completes as soon as it possibly can, considering the trailing edge and bus width effects, the location of the word in memory, the number of outstanding accesses sustainable, and the port limitations.

Port conflicts affect hits to the cache as well. If there are earlier misses to the cache that complete in the same cycle as the new hit and there are not enough ports available to satisfy the hit to the cache, the hit must wait for one or more additional cycles. The same method described above for misses is used to find the hit's completion time.

Obviously, increasing the number of ports will reduce the likelihood that port conflicts occur. With a greater number of ports available, more requests to the cache can be returned to the processor each cycle. On a related note, if the number of outstanding accesses allowed is less than the number of ports to the cache, port limitations will only affect hits to the cache. This occurs because we would never have more misses outstanding than there are available cache ports, so the only time there will be contention for cache ports is when there are hits to the cache that complete in the same cycle that a pending miss completes. Memory accesses are evaluated sequentially in time, so older accesses reserve their use of a port before newer accesses do. Thus, even though an access may be a cache hit, if all the ports for the cycle in which the hit should complete are reserved for prior accesses, the hit must wait at least one additional cycle to obtain an available port and complete its memory access.

### 4.4.5 Flow chart diagramming the operation of the LE cache model

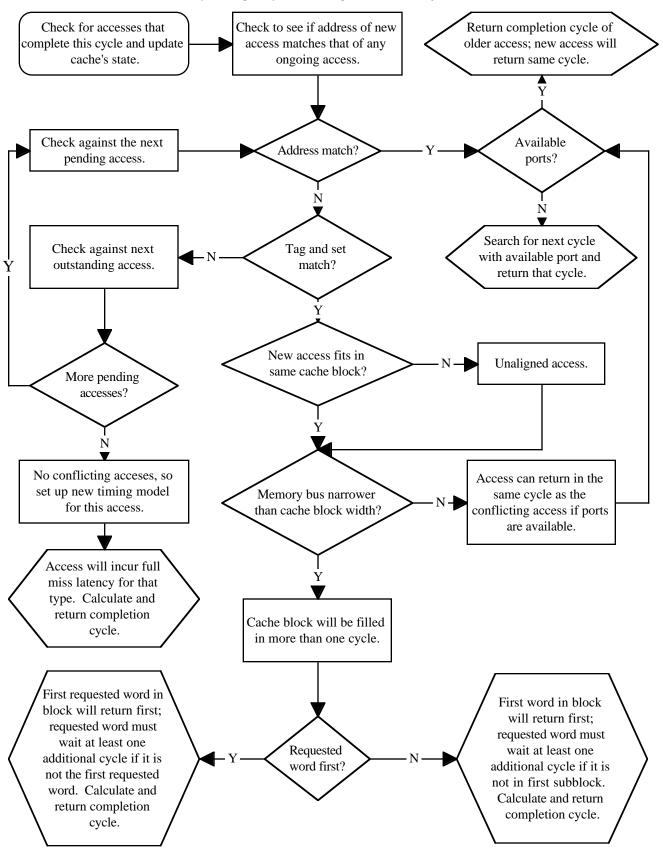

All memory accessing instructions go through the same steps of evaluation in the LE model. Once a completion cycle has been determined, that cycle, minus the cycle that execution of the instruction started, is returned as the latency of the instruction. The flow chart of the operation of LE is shown in Figure 15. At each of the "endpoints" of the flow chart, the completion time for the current access is finalized and that value is returned to the calling program.

Figure 15: Flow chart showing the operation of the LE cache model

The state of the DineroIII cache is not updated until the cycle count of the currently evaluated memory accessing instruction is greater than or equal to the completion cycle of an outstanding access in the update\_buffer. Delaying the update of the cache state until a new access occurs presents no problems, as the state of the cache is "corrected" to reflect the recently completed transactions before a new access is evaluated in LE. If the new access begins execution after an older, outstanding access completes, the new access should not depend upon that older access, and indeed it does not, since all outstanding accesses in the update\_buffer are removed from update\_buffer when they are completed and the cache's state is updated before each new access is evaluated. Since only memory accessing instructions can affect the state of the cache, delaying these updates reduces simulation time, especially during long stretches of compute-only code, as no checks need to be made on the cache unless a new instruction accesses memory. If the new access begins execution before some currently outstanding access(es). Since the outstanding access is still in the update\_buffer, a dependency may be found with the new access, causing the LE cache model to adjust the new access' completion time accordingly.

Currently, unaligned accesses are simply flagged in LE; special mechanisms by which to evaluate unaligned accesses have not been implemented. This case was not considered for two reasons: First, unaligned accesses are rare, undesirable, and avoidable, so not incorporating them into our model should not have a great impact on the model's performance. Secondly, there are many different methods used to handle unaligned accesses, so many so that incorporating a specific handling method would sacrifice the general purpose nature of the LE cache model. If a relatively simple, parameterizeable method for handling unaligned accesses can be derived, it will be incorporated into LE in the future.

## 4.5 Using the RCM model to implement LE

With regard to instruction execution, the LE cache is modeled as single resource. Memory accessing instructions check the cache (LE) resource to determine when execution can begin and when execution completes. The start and end times of each instruction's execution are determined by checking the various effects that an access can encounter, as detailed in Section 4.4. Given when a

#### Early Design Cycle Timing Simulation of Caches

memory accessing instruction completes, dependent instructions are delayed accordingly in the corresponding portions of the RCM simulator (e.g. dependent memory accessing instructions delay their issue times with respect to the cache and dependent execute instructions delay their issue time to the functional units). Since LE is modeled as a single resource, it can easily be joined to an RCM-based processor model to simulate the execution of code on a processor with cache.

Within the LE cache model itself, the cache blocks, busses to and from the cache, the ports, and the cache itself are viewed as resources. If a desired cache block is not available, the requesting instruction must wait a at least a nominal number of cycles until the data is returned to the cache. If the bus to the cache from the next level of memory is currently used to return an earlier requested word, the newer requested word from same cache block must wait additional cycles. Transfers between the cache and the processor are taken care of by the port resources; if a machine has a certain number of ports to the cache, there will be a corresponding number of simultaneously available busses between the cache and the processor. If a port of the desired transaction type is not available, the instruction must again wait additional cycles before it can complete execution. Also, if the cache itself is blocked, all further accesses must wait until some earlier miss completes before execution can continue. Thus, the LE cache model is implemented using the RCM methodology by modeling each effect accounted for in the LE cache model as determined by the availability of some resource.

## 5.0 Experimental results

In order to test the validity of the new cache model, a tool was built to simulate the memory access performance of a given program. The tool was written in the spirit of J-D Wellman's Resource Conflict Methodology, where instructions take differing amounts of time to execute depending upon resource availability. With regard to memory accesses, resources within the LE model include the ports, the cache (available unless blocked), and data (which becomes available when each access to it completes and remains available until the next access to it begins execution in the cache).

The processor and cache simulator combines J-D Wellman's RCM\_brisc tool, which simulates an RS/6000-like [Bakoglu90] machine, with the LE cache model. Based on the REAP tool, RCM\_brisc

simulates the execution of instructions fed to it in the form of a trace of the program's execution on an actual machine, which in this study is an RS/6000. The RCM\_brisc tool by itself simulates the execution of all instructions, but assumes a perfect cache model, where all data from memory is available in a fixed, predetermined amount of time. However, the perfect cache model is an unrealistic estimate of program performance in today's processor/cache designs; cache and memory effects must be included in any processor simulation if it is to realistically evaluate a program's performance on a system under consideration.

The LE cache model, in its current implementation, could easily have been combined with any other currently available instruction-level simulators such as Talisman [Bedichek95], SimICS [Magnusson95], and others. This is possible because this implementation of the LE cache model maintains the state of the caches itself and does not take into account virtual memory or TLB effects. It models the first level of data cache and assumes a perfect memory thereafter, regardless of the number of level of caches beyond that. This simplification still provides accurate pictures of program execution, as we will see later in this section. The RCM\_brisc tool was chosen since the LE cache model was implemented in the same spirit using the RCM model, and, more importantly, the creator of the RCM\_brisc tool was readily accessible (his desk is next to mine).

The combination of the LE cache model implementation with the RCM\_brisc processor simulator involved several pre-existing simulators, namely RCM\_brisc for core processor simulation and DineroIII for behavioral cache simulation. The LE cache model implementation was built on top of, and thus includes, DineroIII in this realization. LE was then fused to RCM\_brisc to "service" memory accesses and determine their execution times. A high level picture of the overall processor/cache simulator is shown in Figure 16; the white portions detail currently existing simulators while the gray, highlighted portion indicates the new work discussed in this paper.

Figure 16: A high-level picture of the overall processor/cache simulator, RCM\_brisc+LE.

The LE cache model implementation handles a wide variety of cache configurations, as determined by the inputs to the simulator. A list of the inputs handled by the LE cache simulator are shown below in Table 1.

| cache size                                                | number of read ports      |  |

|-----------------------------------------------------------|---------------------------|--|

| block size                                                | number of write ports     |  |

| associativity                                             | NOA                       |  |

| replacement policy                                        | CPU-to-cache bus width    |  |

| read miss latency                                         | cache-to-memory bus width |  |

| write miss latency                                        | word size                 |  |

| return policy (requested word first/first subblock first) |                           |  |

Table 1: Inputs used to configure the LE cache model simulator

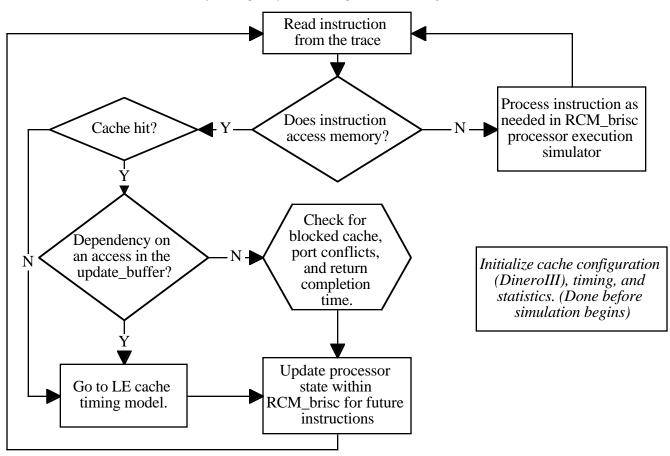

A more detailed picture of the interaction between LE and RCM\_brisc is shown in Figure 17:

Figure 17: Interaction between the processor simulator, RCM\_brisc, and LE