|

Each station is built around an MPC 823 processor/FPGA board, utilizing an NES controller that interfaces to the FPGA and provides input to the game running on the processor. The game board itself is displayed on a VGA monitor, with a framebuffer and the VGA hardware implemented on the FPGA.

Major hardware subcomponents:

NES Controller

The NES Controller is used for player input to the game. It communicates with the processor in order for it to decide what actions to take. It is used to place ships, attack, change screens, and request a rematch. We used a timer to interrupt the processor at a rate of 60 Hz. During this interrupt, the processor reads the state of the NES controller buttons from the FPGA (We have a read controller for the NES Controller on the FPGA). The NES controller is essentially a shift register, and we had to implement hardware to send a series of pulses to the controller and sequentially read the button inputs at any given time.

VGA Monitor

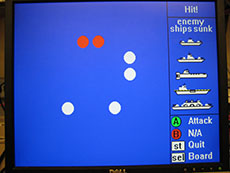

The VGA Monitor is an essential part of our project. It is where the players’ game boards are displayed, and where all the action takes place. There are 3 main screens that the player will see on the monitor. The ship placing screen is where the player will place his ships. The player screen is where the player can see his own ships, and which ones have been hit (the bottom board of a traditional battleship game). The attack screen is where the player can attack and see what squares he has already attacked (the top board of a traditional battleship game). Note that confirming a hit or miss is done automatically.

We had to implement our own framebuffer on the FPGA to store the current data on the screen between refreshes. We had a separate module that generates the Horizontal Sync and Vertical Sync signals at the correct times, according to the VGA specification. We made hardware modules that abstract away things such as writing a pixel, clearing a square, and clearing the board area to simple software calls. The framebuffer has dual ports, so that we can read from and write to it at the same time. There was not enough RAM on the FPGA to implement a 640x480 framebuffer, so we scaled it down to 320x240. It still displays at 640x480, but each pixel in the framebuffer writes to four pixels on the screen.

|