Note: This tutorial is for the Linux toolset. The directions likely apply to the Windows version also, but have not been tested there. In lab we expect you to use the Linux toolset.

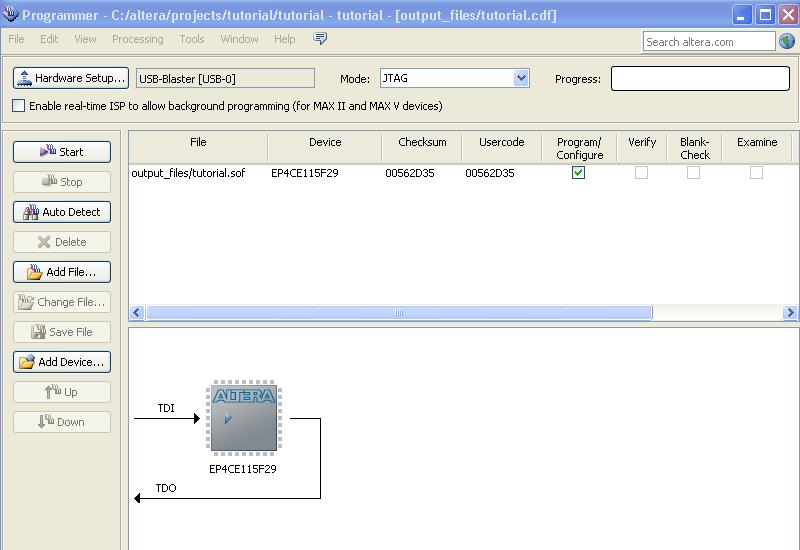

FIGURE 1: Symbol for Majority Voter

TABLE 1: Truth Table for Majority Voter

A B C M

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

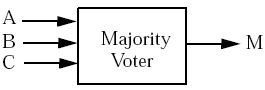

FIGURE 2: Gate Representation of Majority Voter

- Starting Quartus II

- Design Entry

The "Selection and

Smart Drawing

Tool" (Selection mode).

The "Selection and

Smart Drawing

Tool" (Selection mode).  The "Symbol Tool"

The "Symbol Tool"  The "Orthogonal Node

Tool" (Wiring

mode)

The "Orthogonal Node

Tool" (Wiring

mode) - Simulation

To begin using the Quartus software, first open a terminal window. You can do so by right-clicking on an open part of the screen and selecting "Open Terminal" from the menu. In that terminal window type quartus &. The ampersand tells the terminal window to launch the application "in the background" so that the terminal can be used for other things. It may take a minute for the splash screen to come up, so be patient. If this is the first time you've used Quartus, you will be prompted to select a "view type." Use the default: Quartus II. After a bit you should see an introduction window. Proceed to the next window. It will look something like this screenshot.

Click the "Create a New Project (New Project Wizard)" at the splash screen. A screen will appear that has 3 lines of text to fill in. The first line will be populated with the path to your AFS space. For the directory select any directory name, though we recommend you use something like 270labs/tutorial. For the name of the project and the top level-design entity, use "tutorial". Your window should now look like this screenshot. Select "Next". You should be prompted if you wish to create the directory. Select "yes". You have now created a new project.

It is best to put each lab or project in it's own directory. For example, when you start lab 1 the path should be 270labs/lab1, lab 2 should be 270labs/lab2, etc.

Next you will be prompted to add design files. We will create design files a bit later, so skip this window.

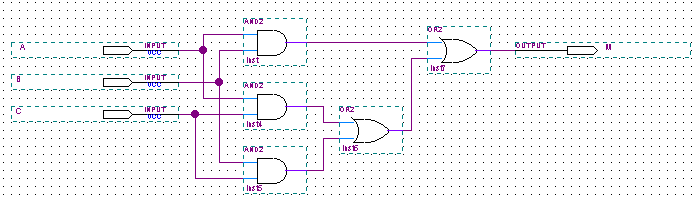

Now you need to tell the software what type of device you will be using. First select Device Family to be Cyclone IVE. Under Available Devices select EP4CE115F29C7. If you look on the DE2 board, you will notice that this is the name and device of the Altera chip. The window should look like this.

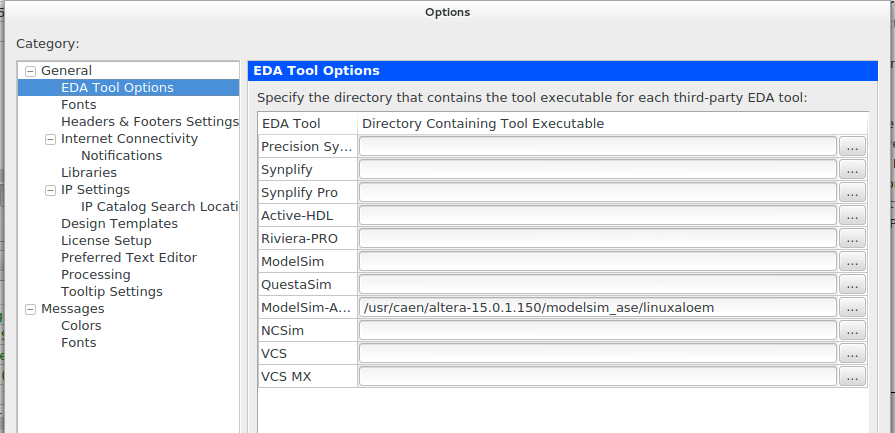

Proceed thru the last to windows (4 and 5) and using the default settings.

The first step in creating the Majority Voter is to enter the design into a schematic. To do so, select File → New... from the Menu and then select "Block Diagram/Schematic File" as shown here.

This will launch the schematic editor. On the left side of the Schematic Editor window is a toolbar containing the different modes of the editor. To change modes, simply click on the appropriate icon. You can also use the "Esc" key to go to the default "Select and Drag" mode. For this tutorial we will be using only the following three modes:

A pop-up window titled "Symbol" will appear. Click on the "plus" sign under libraries and then on the "primitives" and finally "pin". The Symbol window should now look like this screenshot. Make sure that the "repeat-insert mode" checkbox is selected. Select "input" under pins and press OK. As our circuit has three inputs, place the three input pins on the left side of the screen. Do the same thing again, but placing one output on the right side. Your design should look similar to this screenshot. Note that you can move an existing pin by switching to the selection mode. You can also delete a pin by selecting it and then pressing the "delete" key on the keyboard. You can also return to the selection tool by pressing the "Esc" key on the keyboard.

Next, we wish to give these pins names. Right click on each pin and select "properties" OR double-click on the pin. Change the input names of each of the three inputs to A, B or C. Change the output pin's name to "M". The screen should now resemble this screenshot.

Now add three 2-input AND gates and two 2-input OR gates. You will want the AND gates in a column to the right of the input pins and the OR gates to the right of them (as seen in Figure 2, above). Don't worry about the wires yet. You can select the gates by using the Symbol tool under "primitives" then "logic". You want "and2" and "or2" (see here for selecting a 2-input AND gate). Once you've added the five gates, your design should resemble this screenshot.

This would be a good time to save your design. Select File → Save Project and respond in the affirmative to any dialog box which may come up. In general, you should save your work every five minutes or so. We've had a few problems with the tool crashing.

Next, switch to wiring mode and connect the gates and pins so as

to implement

the function shown in Figure 2. You may find that the tool doesn't

always place the wire in the way you'd like. This can be a real

problem

when the tool ends up connecting a given wire to things you hadn't

intended.

A trick is to draw the wire "part way" to where you want it and

then

end the wire. From that point you can then finish the wire from the

other end. This can be

a

bit tricky and you should ask for help if things don't seem right to

you.

In general, if you see an "X" at the end of the wire, that means the

wire

isn't connected at that point. And if a wire touches an input or

output, it

is connected to that location. You can test for this by dragging a

component and making sure the wires move with it. You may find

connecting the wires difficult to begin

with, and you should be using "undo" (ctrl-Z) as needed to remove

mistakes.

Try your best to draw your circuit so it looks like this:

FIGURE 3: Completed majority gate

Congratulations, you've drawn your first circuit in Quartus!

There is a

fair

bit more to do, but you've finished the design aspect. At this

time

it is worth noting that there are other ways to do some of the things

we've

done. For example, components can also be automatically connected by

wires

if you place them touching one another and then drag them apart. (If

this

doesn't work, you should check to see that the "rubberbanding" icon ![]() is

selected. You can also call up the "Symbol tool" by double-clicking

openspace in the design pane (though the repeat-insert mode will not be

checked by default).

is

selected. You can also call up the "Symbol tool" by double-clicking

openspace in the design pane (though the repeat-insert mode will not be

checked by default).

To make sure that all wires are connected and none of the components are used incorrectly you can simply pick-up each device and move it around. Its wires should stay connected (again, assuming the "rubberbanding" icon is selected.)

Again, this would be a good time to save the project. Quartus

seems to

crash every

now and again. So save early and often.

Your lab assignments will require you to submit an image of

your schematic. To create a PDF of your schematic select,

File-->Print, and then Print to File (PDF). You can also select the

directory path in this window.

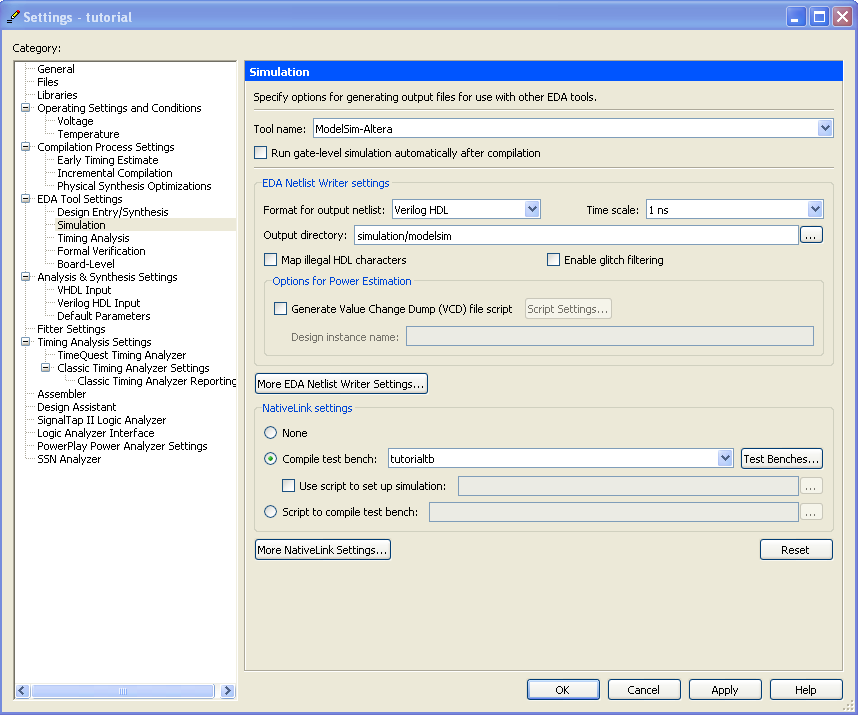

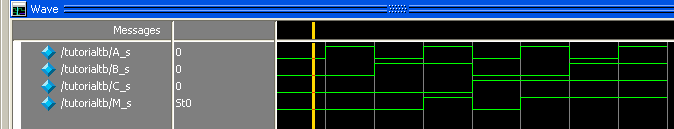

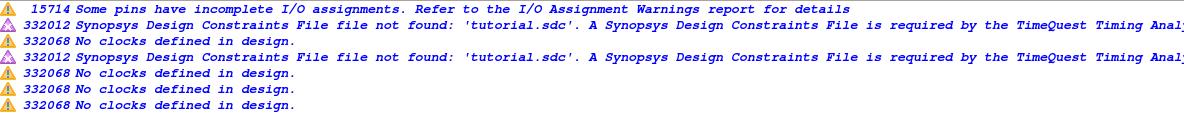

Now that the Majority Voter is completely laid out, we will test its correct functionality by observing the output M when the inputs A, B, and C are given certain values. With the Quartus toolset you can provide a set of inputs to your design and check to see what outputs are generated. This is helpful in finding errors in your design.

You might imagine the best way to test our design is to provide

all the input combinations in Table 1. One way to do this is with a

hardware descripton language (HDL) called Verilog. The file and

specification is commonly refered to as a test bench. An example of a

test bench for the majority voter that tests for all the combinations

in table 1 follows.

button in Quartus tool bar.

button in Quartus tool bar.

in the toolbar.

in the toolbar.